* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download VLSI Design Pass Transistor Logic

Power inverter wikipedia , lookup

Buck converter wikipedia , lookup

Thermal runaway wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Control system wikipedia , lookup

Curry–Howard correspondence wikipedia , lookup

Semiconductor device wikipedia , lookup

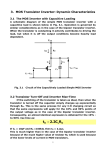

VLSI Design Pass Transistor Logic [Adapted from Rabaey’s Digital Integrated Circuits, ©2002, J. Rabaey et al.] ECE 4121 L07 Pass Transistor Logic.1 ZALAM, 2007 NMOS Transistors in Series/Parallel Primary inputs drive both gate and source/drain terminals NMOS switch closes when the gate input is high A B X Y X = Y if A and B A X B X = Y if A or B Y Remember - NMOS transistors pass a strong 0 but a weak 1 ECE 4121 L07 Pass Transistor Logic.2 ZALAM, 2007 PMOS Transistors in Series/Parallel Primary inputs drive both gate and source/drain terminals PMOS switch closes when the gate input is low A B X Y X = Y if A and B = A + B A X B X = Y if A or B = A • B Y Remember - PMOS transistors pass a strong 1 but a weak 0 ECE 4121 L07 Pass Transistor Logic.3 ZALAM, 2007 Pass Transistor (PT) Logic B B A 0 B F A B F 0 Gate is static – a low-impedance low impedance path exists to both supply rails under all circumstances N transistors instead of 2N No static power consumption Ratioless Bidirectional (versus undirectional) ECE 4121 L07 Pass Transistor Logic.4 ZALAM, 2007 Pass Transistor (PT) Logic B B A 0 B F =A•B A B F =A•B 0 Gate is static – a low-impedance low impedance path exists to both supply rails under all circumstances N transistors instead of 2N No static power consumption Ratioless Bidirectional (versus undirectional) ECE 4121 L07 Pass Transistor Logic.5 ZALAM, 2007 VTC of PT AND Gate B 1 5/0 25 1.5/0.25 2 Vout, V 0.5/0.25 A 0.5/0.25 B 0 0.5/0.25 z B=VDD, A=0→VDD 1 A=VDD, B=0→VDD A=B=0→VDD F= A•B 0 0 1 2 Pure PT logic is not regenerative - the signal gradually degrades after passing through a number of PTs (can fix with static CMOS inverter insertion) ECE 4121 L07 Pass Transistor Logic.6 ZALAM, 2007 Differential PT Logic (CPL) B A A B B PT Network A A B B Inverse PT Network B B F F=AB F AB B B F=AB B AND/NAND ECE 4121 L07 Pass Transistor Logic.7 B A F=A+B B A A F B A A F F A F=A⊕B A F=A+B B F=A⊕B A OR/NOR XOR/XNOR ZALAM, 2007 CPL Properties Differential so complementary data inputs and outputs are always available (so don’t need extra inverters) Still static, since the output defining nodes are always tied to VDD or GND through a low resistance path Design D i iis modular; d l allll gates t use th the same ttopology, l only l the inputs are permuted. Simple XOR makes it attractive for structures like adders Fast (assuming number of transistors in series is small) Additional routing overhead for complementary signals Still have static power dissipation problems ECE 4121 L07 Pass Transistor Logic.8 ZALAM, 2007 CPL Full Adder B Cin B Cin A !Sum A Sum B B Cin Cin A B !Cout Cin A B ECE 4121 L07 Pass Transistor Logic.9 Cout Cin ZALAM, 2007 CPL Full Adder B Cin B Cin A !Sum A Sum B B Cin Cin A B !Cout Cin A B ECE 4121 L07 Pass Transistor Logic.10 Cout Cin ZALAM, 2007 NMOS Only PT Driving an Inverter In = VDD A = VDD VGS D Vx = VDD-V VTn M2 S B M1 Vx does not pull up to VDD, but VDD – VTn Threshold voltage drop causes static power consumption (M2 may be weakly conducting forming a path from VDD to GND) Notice VTn increases of pass transistor due to body effect (VSB) ECE 4121 L07 Pass Transistor Logic.11 ZALAM, 2007 Voltage Swing of PT Driving an Inverter 3 In In = 0 → VDD 1.5/0.25 B x Out 0.5/0.25 Voltage, V S VDD D 0.5/0.25 2 x = 1.8V 1 Out 0 0 0.5 1 1.5 Time, ns Body effect – large VSB at x - when pulling high (B is tied i d to GND and d S charged h d up close l to VDD) So the voltage drop is even worse Vx = VDD - (VTn0 + γ(√(|2φf| + Vx) - √|2φf|)) ECE 4121 L07 Pass Transistor Logic.12 ZALAM, 2007 2 Cascaded NMOS Only PTs B = VDD B = VDD C = VDD G A = VDD M1 S C = VDD x = VDD - VTn1 z M1 x M2 y Out G y M2 Out S Swing g on y = VDD - VTn1 - VTn2 z A = VDD Swing g on y = VDD - VTn1 Pass transistor gates should never be cascaded as on the left Logic on the right suffers from static power dissipation and reduced noise margins ECE 4121 L07 Pass Transistor Logic.13 ZALAM, 2007 Solution 1: Level Restorer Level Restorer on Mr off B A=1 A=0 A 0 Mn x= 0 1 M2 Out=0 Out =1 1 M1 Full swing on x (due to Level Restorer) so no static power consumption by inverter No static backward current path through Level Restorer and PT since Restorer is only active when A is high F correctt operation For ti Mr mustt be b sized i d correctly tl ((ratioed) ti d) ECE 4121 L07 Pass Transistor Logic.14 ZALAM, 2007 Transient Level Restorer Circuit Response 3 W/L2=1.50/0.25 W/Ln=0.50/0.25 W/L1=0.50/0.25 Voltage, V 2 W/Lr=1.75/0.25 node x never goes below VM of inverter so output never switches W/Lr=1.50/0.25 1 W/Lr=1.25/0.25 W/Lr=1.0/0.25 0 0 100 200 Time, ps 300 400 500 Restorer has speed p and p power impacts: p increases the capacitance at x, slowing down the gate; increases tr (but decreases tf) ECE 4121 L07 Pass Transistor Logic.15 ZALAM, 2007 Solution 2: Multiple VT Transistors Technology solution: Use (near) zero VT devices for the NMOS PTs to eliminate most of the threshold drop (body effect still in force preventing full swing to VDD) low VT transistors In2 = 0V A = 2.5V on Out off but leaking In1 = 2.5V B = 0V sneak path Impacts static power consumption due to subthreshold currents flowing through the PTs (even if VGS is below VT) ECE 4121 L07 Pass Transistor Logic.16 ZALAM, 2007 Solution 3: Transmission Gates (TGs) Most widely used solution C C A A B B C C C = GND A = VDD B C = VDD C = GND A = GND B C = VDD Full swing bidirectional switch controlled by the gate signal C, A = B if C = 1 ECE 4121 L07 Pass Transistor Logic.17 ZALAM, 2007 Solution 3: Transmission Gates (TGs) Most widely used solution C C A A B B C C C = GND A = VDD B C = VDD C = GND A = GND B C = VDD Full swing bidirectional switch controlled by the gate signal C, A = B if C = 1 ECE 4121 L07 Pass Transistor Logic.18 ZALAM, 2007 Resistance of TG W/Lp=0.50/0.25 30 0V 25 Rn Rp Resistance, kΩ Ω 20 2.5V Vout Rp Rn 15 2.5V 10 Req W/Ln=0.50/0.25 0 50/0 25 5 0 0 ECE 4121 L07 Pass Transistor Logic.19 1 2 ZALAM, 2007 TG Multiplexer S S S S F S VDD In2 S F In1 S F = !(In1 • S + In2 • S) GND In1 ECE 4121 L07 Pass Transistor Logic.20 In2 ZALAM, 2007 Transmission Gate XOR A A⊕B B ECE 4121 L07 Pass Transistor Logic.21 ZALAM, 2007 Transmission Gate XOR weak 0 if !A ff off on A • !B A⊕B off on B • !A A 0 B 1 ECE 4121 L07 Pass Transistor Logic.22 weak 1 if A an inverter ZALAM, 2007 TG Full Adder Cin B A Sum Cout ECE 4121 L07 Pass Transistor Logic.23 ZALAM, 2007 Differential TG Logic (DPL) B A B B A A B A A A F=AB GND B F=A⊕B A B B GND A VDD A F=AB B VDD A B B AND/NAND ECE 4121 L07 Pass Transistor Logic.24 F=A⊕B XOR/XNOR ZALAM, 2007 Next Time: The MOS Transistor MOS transistor dynamic behavior (R and C)) Wire capacitance ECE 4121 L07 Pass Transistor Logic.25 ZALAM, 2007