* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Experiment 1: The Cascode Amplifier

Stage monitor system wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Chirp compression wikipedia , lookup

Negative feedback wikipedia , lookup

Alternating current wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Mains electricity wikipedia , lookup

Buck converter wikipedia , lookup

Utility frequency wikipedia , lookup

Chirp spectrum wikipedia , lookup

Schmitt trigger wikipedia , lookup

Two-port network wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Ringing artifacts wikipedia , lookup

Zobel network wikipedia , lookup

Mechanical filter wikipedia , lookup

Audio crossover wikipedia , lookup

Opto-isolator wikipedia , lookup

Analogue filter wikipedia , lookup

Distributed element filter wikipedia , lookup

Rectiverter wikipedia , lookup

Kolmogorov–Zurbenko filter wikipedia , lookup

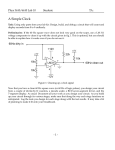

ECE 434 Linear Electronics II Laboratory and Experiment Guide 1 ECE 434 Lab Manual Table Of Contents Spring 2006 Page Date Experiment 2 Lab #1: Cascode Amplifier 3 Lab #2: Differential Amplifier 4 Lab #3: Active Filters I 7 Lab #4: Active Filters II 11 Lab #5: Fiber Optic Communications 14 Lab #6: Oscillators 16 Lab #7: Voltage-Shunt Feedback Amplifier 17 Lab #8: Series-Shunt Feedback Amplifier 18 Lab #9: IC555 Timer Monostable and Astable Exp 20 Additional Lab #1: Voltage-Series Feedback Amp 21 Additional Lab #2: Voltage Comparators 23 Data Sheet Appendix 2 Student Signature TA Signature Experiment 1: The Cascode Amplifier The cascode amplifier configuration consists of a common emitter stage followed by a common base stage. The two major advantages of a cascode amplifier are a low load resistance (which results in an improved frequency response) and a high output resistance. Build the following circuit: 0 Vcc 12V RC R1 4k 18k 1u C1 2N2222 10u R2 0 4k Vsmall 4k RL 2k 2N2222 0 1u R3 8k RE 3.3k 10u 0 Figure 1: Cascode Amplifier 1. Measure the DC operating point of each transistor and compare your results with the calculated values. 2. At a frequency of 5 KHz, measure the voltage gain, the input and the output resistance and compare your results with the theoretical values. Calculate the power gain from both experimental and theoretical values. 3. Find the maximum peak-to-peak output voltage swing (i.e. the maximum swing without distortion). 4. Measure the frequency response of the circuit and comment on the change observed in comparison with a single stage common-emitter amplifier. 5. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 3 Experiment 2: The Differential Amplifier 0 15V RL RL Vo 1 Vo 2 Ri 1k Ri 2N2222 2N2222 R1 1k 2N2222 Vi 1 Vi 2 R2 RE 0 1.5k 0 RE 15V 0 Figure 2: Constant Current Source 15V 0 Figure 1: Differential Amplifier 1. Calculate the resistor values so that the Q points of the transistors are at 8 volts and 3 milliamps. 2. Set Vi2 equal to zero volts. Measure and plot the DC transfer characteristics of Vi1 versus the two outputs. (Vary Vi1 from -1V to 1V in small increments) 3. Apply a small differential input signal υi at Vi1. Measure the single-ended differential gain and the common-mode gain. Compare the resulting values with the theoretical values. 4. Find the theoretical and experimental common-mode rejection ratios of the circuit. 5. Replace RE and adjoining voltage source with the circuit found in Figure 2. Calculate resistor values that will give the same operating points. Repeat steps 3, 4, and 5. 6. Simulate both circuits using Pspice. Compare the Pspice results with those obtained in the previous parts. 4 Experiment 3: Active Filters I Low Pass Filters An ideal low pass filter is a circuit that passes those frequencies lower than the corner frequency and attenuates those frequencies higher than the corner frequency. Therefore, the ideal low pass filter has a gain of unity below the corner frequency and has a gain of zero above the corner frequency. In practice however, it is not possible to achieve this ideal characteristic; the gain of the filter begins to decrease when the frequency approaches the corner frequency and it does not decrease as sharply as that of the ideal filter after this frequency. The simplest form of the active low pass filter is shown in Figure 1. C1 1n R2 10k 0 - . R1 12V 10k . 600 + R3 LM 741 RL 1k . RG 4.7k -12V VS 0 0 0 0 Figure 1: Low Pass Filter This filter uses a capacitor and a resistor connected in parallel in the feedback path of an inverting amplifier. When the frequency is low, the reactance of the capacitor is very large; so the gain is approximately unity. At high frequencies, however, the reactance is small, and the feedback impedence is small. This causes a small gain. This filter is a single pole filter because there is only one pole in the transfer function of the filter, which is created by the RC pair. The corner frequency of the filter is given by: 1 fc = 2πRC Since the corner frequency is defined as the frequency where the gain is .707 (3dB), the reactance of the capacitor must be equal to the value of the resistor. Note that the roll-off for the single pole filter is 6 dB per octave (equal to 20 dB per decade). A two pole active low pass filter is shown in Figure 2. 5 0 12V - . C1 20n . R2 + 10k RG LM 741 . R1 10k 600 RL C2 1k 10n VS - 12V 0 0 0 0 Figure 2: Two pole active low pass filter It is called a two pole filter because there are two poles in the transfer function as a result of having tow RC pairs. Since there are two poles, the roll-off after the corner frequency will be 12 dB per octave, or 40 dB per decade. Thus, the two pole filter is a better approximation to the ideal filter. In this case, the corner frequency is given by the following equation: 1 fc = 2π R1 R2 C1C 2 R2 High Pass Filters 10k 0 R1 C1 10k 20n - . 12Vdc . 600 + LM 741 . RG RL R3 1k 10k VS -12Vdc 0 0 0 Figure 3: Single pole high pass filter 6 0 The high pass filter attenuates the low frequencies below the corner frequency and passes the high frequencies above the corner frequency. The effect is just the opposite of the low pass filter and its response is the symmetric of the low pass response about the vertical axis passing through the corner frequency. Again there are single pole and two pole high pass filters (as shown in Figures 3 and 4 respectively). The formulas for the critical and corner frequencies are the same as those given for the low pass filter. Of course, the roll-off is 6 dB per octave for a single pole filter and 12 dB per octave in a two pole filter. R1 4.7k 0 12V - RG C2 10n . 600 + R2 LM 741 . 10n . C1 10k RL 1k -12V VS 0 0 0 0 Figure 4: Two pole high pass filter Procedure 1. 2. 3. 4. Build the single pole low pass filter shown in Figure 1 Sweep the input signal frequency from10 Hz to 100 KHz while monitoring the output signal (Use an input signal of 1 Volt peak-to-peak). Measure the corner frequency (or -3 dB frequency) and plot the frequency response. Monitor the 6 dB per octave (or 20 dB per decade slope). 5. Repeat the steps above for the filters shown in Figures 2,3, and 4. For the two pole filters monitor the 12 dB per octave (or 40 dB per decade slope). 7. Simulate all circuits using Pspice. Compare the Pspice results with those obtained in the previous parts. 7 Experiment 4: Active Filters II 1. Band Pass Filters An ideal band pass filter is a circuit that passes only a specific frequency or a group of frequencies. There are different types of band pass filters: The “Twin T” active band pass filters are highly selective. If a broad band of frequencies are to be passed, the cascaded low and high pass filters are used. Finally, the state variable active filter finds its use when the passing frequencies and bandwidth is to be made variable. The “Twin T” Band Pass Filters The “Twin T” band pass filter is a combination of low pass and high pass filters (see Figure 1). In this type of filter, the roll-off frequency of the low pass filter coincides with the roll-off frequency of the high pass filter. However, there is a 180 degree phase difference in the currents at the center frequency. Theoretically, the currents therefore cancel. Also, at the center frequency, the impedances of the T circuits are very high, which results in a high gain. The frequency at which the gain of the filter has a maximum peak is given by: 1 fc = 2πRC where R=R1=R2, C=C1=C2, R3=R2/2, and C3=2C R6 100k R1 R2 6.8k 6.8k R3 C3 20n 10k C1 10n C2 0 10n 0 12Vdc - . R4 10k . RL . + RG LM 741 1k 600 R5 5.6k VS -12Vdc 0 0 0 Figure 1: "Twin T" Band Pass Filter 8 0 Cascaded Band Pass Filters Cascading the two pole low pass and high pass filters provides a band pass filter which has a broad frequency selection capability, a flat response in the pass band (unity gain), and a roll-off on both the high and low end of the pass band which, theoretically, is 40 dB per octave (refer to Figure 2). R1 10k 0 0 C11 1n 12V C1 RG R11 C2 20n R22 . . + 600 10k 10k + . LM 741 LM 741 . 10n - . - . 12V RL C22 R2 10k VS 1k 500p -12V -12V 0 0 0 0 0 0 Figure 2: Cascaded Band Pass Filter The State Variable Band Pass Filter The state variable band pass filter is a combination of two low pass filters (integrators) and an inverting (summing) amplifier. Basically, the band pass is accomplished by the two low pass filters, where one is converted to a high pass filter by an additional 180 degree phase shift (see Figure 3). The center frequency of the state variable band pass filter is given by: 1 fc = 2π R5 R7C1C2 2. Band Reject Filters Band reject (or band stop) filters do exactly the opposite of the band pass filters; they reject a specific frequency or a group of frequencies and pass the rest. A “Twin T” band reject filter is shown in Figure 4. Notice that the only change in the circuit compared to the “Twin T’ band pass filter is the location of the two twin circuits. Since the T circuits have a very high impedance at the center frequency, the gain at the center frequency will be approximately zero. 9 R9 10k R10 C1 4.7k 20n R2 R5 10k 100k 0 0 C2 20n 0 12V 12V R7 . 10k R4 VS R3 0 10k LM 741 + LM 741 R6 -12V 4.7k 0 0 R8 -12V 10k 0 0 1k 0 0 Figure 3: The State Variable Band Pass Filter 0 R5 R1 100k 12V R2 6.8k 6.8k C1 C2 - . + RG 600 10n LM 741 10n RL C3 1k R6 R3 20n VS 0 10k 0 100k -12V 0 Figure 4: Band Reject Filter 10 0 RL -12V 10k . + LM 741 . 600 + . RG . . . . 10k - . - - . R1 . 12V 0 0 Procedure 1. 1.1. Build the “Twin T” band pass filter shown in Figure 1. 1.2. Measure the center frequency using a 100 mV peak-to-peak input signal. 1.3. Measure the voltage gain at the center frequency and verify by: R AV = 6 R4 1.4. Measure the bandwidth of the filter ( Bw = f H − f L ) and verify the result by using f Bw ≈ c where Q = AV . Q 1.5. Plot the frequency response. 2. 2.1. Build the cascaded band pass filter shown in Figure 2. 2.2. Using a 1 V peak-to-peak input signal, measure the low and high cutoff frequencies and find the bandwidth. 2.3. Plot the frequency response. 3. 3.1. Build the state variable band pass filter shown in Figure 3. 3.2. Measure the center frequency using a 100 mV peak-to-peak input signal. Adjust resistor R9 so that the center frequency is at the theoretical value. 1 3.3. Measure the bandwidth and verify your result by Bw ≈ 2π R5C1 3.4. Plot the frequency response. 4. 4.1. Build the band reject filter shown in Figure 4. 4.2. Using a 1 V peak-to-peak input signal, measure the center frequency. 4.3. Plot the frequency response. 5. Simulate all circuits using Pspice. Compare the Pspice results with those obtained in the previous parts. 11 Experiment 5: Fiber Optic Communications Background: Digital communication systems transmit information in binary format, i.e., the information transmitted by a digital communication system consists of a sequence of bits. This brings about two fundamental questions: 1. 2. How is information converted into a sequence of bits? How are bits transmitted, i.e., mapped to the signals used by the communications system? We will experiment with solutions to each of these questions. For this experiment, we will focus on transmitting textual information. Converting a sequence of characters into a sequence of bits is fairly straightforward and is referred to as encoding. The standard way to convert text into bits relies on the ASCII code that maps each character into a sequence of eight bits. An excerpt from the ASCII conversion table is attached. Alternative conversion methods exist and we wil1look at encoding used for telegraph systems as well; the corresponding code is known as the Morse code. There are many methods for transmitting a sequence of bits. Each bit is mapped to one of two allowed values for the amplitude ( e.g. +5V and 0V), phase ( e.g., 0 degrees or 180 degrees), or frequency of the transmitted signal. These digital modulation methods are known as amplitude shift keying (ASK), phase shift keying (PSK), and frequency shift keying (FSK), respectively. The receiver observes the signal and makes a decision which bit (0 or 1) was transmitted. Systems operating in this way require tight synchronization between the transmitter and receiver. Both transmitter and receiver must agree when the transmission of a specific bit transmission begins and ends. For the purposes of this experiment, synchronization is difficult to achieve. Instead we resort to using an alternative modulation method that is self-synchronizing. Pulse width modulation (PWM) maps bits to long or short pulses. There is a pause between each pulse that signals the beginning and end of bits. Therefore, the receiver can deduce the bit timing very easily from the observed signal itself. For this experiment, we let a O-bit be transmitted as a short pulse and a 1-bit is transmitted as a long (wide) pulse. Long pulses should be approximately three times as long as a short pulse. Using pulse width modulation you will be able to operate the transmitter manually and also decode the received signal manually. Hence, you get (literally) hands-on experience how a digital transmitter and receiver work. 12 Part 1: Building the Fiber Optical Communication System circuits Important note: You will not use the printed circuit boards in your kit as the circuit requires some modifications to ensure reliable operation. Procedure: 1. Study the instructional booklet. You are expected to be familiar with the theory of the operation of the kit as described in the booklet before you come to the lab. 2. Set up the transmitter circuit as shown in Figure 9 of the booklet. 3. Verify the operation of the transmitter circuit by observing the voltage at test point TP 1 with input EN equal to 0 and input EXT varied between 0 and 1. Then measure the voltage across the LED (IF-E96). Make a note of your expected results compared with your actual measurements. 4. Prepare and connect the optical fiber according to the instructions on page 5 of the booklet. 5. Set up the receiver circuit (preferably on a second board) according to the diagram below. 5V 0 1k TP2 DATA Q2 Q1 4093 IF-D92 Q2N3904 1k TP3 0 Figure 1: Circuit Diagram Of The Receiver 6. You will have to tune the biasing resistor between the two transistors. What is the purpose of that transistor and what voltage should you expect to observe between the base and emitter of the second transistor, i.e., across the lower half of the potentiometer? • To tune the circuit, you should adjust the potentiometer such that you observe the proper switching behavior in your receiver, in other words, monitor both the EXT input of the transmitter (set EN equal to 0) and the DATA output of the receiver and adjust the potentiometer until both are equal. • Measure the DC voltage across the base-emitter junction of the second transistor. 13 7. 8. The remaining measurements are intended to assess the performance limits of this circuit. For this purpose, connect a square wave signal generator to the EXT input of the circuit (EN remains equal to 0). Make sure the signal generator produces TTL levels! Throughout, observe signals at test points TP 1 (transmitter) and TP 3 (receiver) on the oscilloscope. Begin with a frequency of 1 KHz. Compare the two signals. Observe the effect when adjusting the biasing potentiometer. Fine-tune the potentiometer to make the two signals as similar as possible. Sketch the two signals and accurately measure and indicate the observed voltage levels as well as the delay between the two signals. Part 2: Using the Fiber Optical Communication System Procedure: l. In the circuit from the previous experiment, connect the EXT input of the transmitter to one of the toggle switches (labeled A/A with overbar). Connect the DATA output to one of the LEDs. Verify that you can switch the DATA output via the EXT toggle switch. If necessary, correct the EN input. 2. Take a short text message (5-10 characters, e.g., your name or the name of your dog) and convert it into a sequence of bits. Use the Morse code table below for encoding. Dots denote short pulse and dashes stand for long pulses. If the duration of a dot is taken to be one unit, then that of a dash is three units. The space between the components of one character is one unit, between characters is three units and between words seven units. 3. While you are transmitting the resulting Morse code sequence using pulse width modulation, your lab partner should observe the DATA LED and convert his observation into a text message. Did any errors occur? 4. The partner who operated the receiver should observe the DATA LED and convert his observation into a text message. Did any errors occur? Repeat parts 2 through 4 with reversed roles. 5. Morse Code Table A B C D E F G .-… -.-. -.. . ..-. --. H I J K L M O …. .. .---..-.. ---- P Q R S T U V 14 .--. --..-. … ..…- W X Y .--..-.-- Z --.. Experiment 6: Oscillators Part 1: RC Phase Shift Oscillator 12V R1 47k RC 0 6.8k C C Q2 C R 3.9k R 3.9k 0 0 2N2222 R2 6.8k RE 1k CE 10u R3 0 560 Figure 1: RC Phase shift Oscillator 1. Build the circuit taking C = 10 nF. 2. Power up the circuit and observe the output on the oscilloscope. 3. Measure the period and find the frequency. 4. Verify the experimental result by using: f = 1 * 2π RC 1 6+4 RC R 5. Repeat the above experiment for C = 1 nF. 6. Simulate both circuit configurations using Pspice. Compare the Pspice results with those obtained in the previous parts. Questions: 1. Why is the value of R2 not equal to that of R? 2. How does the emitter bypass capacitor affect the output? 3. What happens when one of the capacitors in the feedback network has a different value than the others? Thoroughly explain the reason for it. 15 Part 2: Wein Bridge Oscillator 12V 0 1k 470 22k 82k 2N2222 2N2222 10n 18k 3.9k C 10n 0 1.5k R 15k Figure 1: Wein bridge Oscillator 1. Build the correct circuit and do not power it up until you have made certain that all connections are complete and correct. 2. Observe the output on the oscilloscope. Vary the 1 KOhm potentiometer to obtain the maximum output voltage without distortion. 3. Measure the frequency and amplitude of the output signal. 4. Based on theory, what is the possible maximum peak-to-peak output voltage? 5. The theoretical value of the frequency of the output is given by: 1 fc = 2πRC where R and C are the resistor and capacitor in the feedback circuit. Substitute the values of Rand C in the above equation and calculate the frequency. Compare this with your experimental result. 6. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 16 Experiment 7: Voltage-Shunt Feedback Amplifier 15V RL 0 RF R1 2N2222 VS 0 0 Figure 1: Voltage-Shunt feedback amplifier 1. Design the circuit so that the transistor operates with VCE equal to 6 volts and IC equal to 1 mA. Neglect the base current in the design of the input circuit and assume: R f + R1 = 100 Kohms 2. Measure the voltage gain. Explain any discrepancy from the theoretical value. 3. Measure the frequency response of the amplifier. 4. Measure the input and output resistances and compare them with the theoretical values. 5. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 17 Experiment 8: Series-Shunt Feedback Amplifier 0 10.7V R3 20k Q3 2N2222 Rs 10k Q1 Q2 2N2222 R2 9k 2N2222 Vsmall RL 0 1mA R1 1k 0 0 5mA 2k 0 0 Figure 1: Series-Shunt feedback amplifier 1. Design the two current sources and construct the circuit shown above in Figure 1. 2. Using a small input signal measure the voltage gain of each stage, the total voltage gain, the input resistance, and the output resistance 3. Plot the frequency response of the amplifier. 4. Using A = Vf ' Vo ' [R3 // (β3 + 1)(re 3 + (RL // (R1 + R2 )))] RL // (R1 + R2 ) and = 10 R1 // R2 ( ( ) ) Vi ' r + R // R + R e 3 L 1 2 re1 + re 2 + + β1 + 1 β1 + 1 R1 compare experimental results with calculated values. Note that Vo ' R1 + R2 A is the open-loop amplifier gain and β is the feedback factor. Also note that β1 , β 2 , and β 3 are the beta values of the transistors Q1 , Q2 , and Q3 respectively. β= 5. = Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 18 Experiment 9: IC555 Timer For Monostable and Astable Operation Monostable Operation: In this case the timer functions as a one-shot. The external capacitor C is initially held discharged by a transistor inside the timer. Upon application of a negative trigger pulse of less than 1/3 Vcc to pin 2, the internal flip flop is set. This both releases the short circuit across the capacitor and drives the output high. The voltage across the capacitor increases exponentially for a period of t = 1.1Ra C1 at the end of which time the voltage equals 2/3 Vcc. The comparator then resets the internal flip flop, which in turn discharges the capacitor and drives the output to its low state. Complete the following: 0 +5 to 15 V Reset Vcc 4 8 Ra 50 2 3 Discharge Threshold 7 6 Trigger CV Out 5 C . 4. 5. Connect the circuit as shown in Figure 1 for Monostable Operation Design values for which Ra and C produce t= 1.1 ms Measure and draw the waveform using an oscilloscope and compare with the theoretical values. Write down your observations and comments. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 1M 1 1. 2. 3. LM555 0.1u 0 Figure 1: Monostable Operation 19 Astable Operation: If the circuit is connected as shown in Figure 2 (pins 2 and 6 shorted), it will trigger itself and free run as a multi-vibrator. The external capacitor C charges through Ra+Rb, and discharges through Rb only. Thus the duty cycle may be precisely set by the ratio of these two resistors. In this mode, the charge and discharge times, and therefore the frequency are independent of the supply voltage. Complete the following: 1. 2. Connect the circuit as shown in Figure 2 for Astable Operation Design values of Ra and Rb using t1 = .693( Ra + Rb )C = 4.7ms and 3. 4. 5. t 2 = .693Rb C = 2ms , where t1 is the charge time, and t2 is the discharge time. Calculate the total time period and the Duty Cycle. Write down your observations and comments. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 0 +5 to 15 V Reset Vcc 4 8 Ra 50 Discharge 7 Rb 2 Threshold CV Out 6 5 1M 1 . 3 Trigger LM555 C 0.1u 0 Figure 2: Astable Operation 20 Additional Experiments These experiments will be used at the T.A.’s discretion. They could be used as a regular experiment, as a midterm or final exam, or just for practice. Additional Experiment 1: Voltage Series Feedback Amplifier 12V 100k 2.2k 0 2.2k 120k 10u 10u 2N2222 2N2222 10u 30k VS 1.5k 22u 51k 1.5k 22u 200 200 10u 0 0 0 2k 0 Figure 1: Voltage-Series feedback amplifier 1. Construct the circuit without the 2kΩ/10μF feedback network and measure the DC operating point of each transistor. 2. Using a small input signal (at f = 5 KHz ) measure the voltage gain of each stage, the total voltage gain, the input resistance, and the output resistance 3. Find the lower and higher cutoff frequencies if possible. 4. Connect the feedback network to the circuit and repeat steps 2 and 3. 5. Compare experimental results with calculated values. 6. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 21 Additional Experiment 2: Voltage Comparators The LM311 is a high speed voltage comparator. This device is designed to operate from a wide range of power supply voltages, including +15V supplies for operational amplifiers and 5V supplies for logic systems. The output levels are compatible with most TTL and MOS circuits. These comparators are capable of driving lamps or relays isolated from the system ground. The outputs can drive loads referenced to ground, +Vcc or –Vcc. The offset balancing and strobe capabilities are available, and the outputs can be wire-OR connected. If the strobe is low, the output will be in the off state regardless of the differential output. Summary of Features: 1. Operates from a single 5V supply 2. Input current 150 nA max 3. Offset current 20 nA max 4. Differential input voltage range ±30V 5. Power consumption is 135 mW at ±15V Applications of Voltage Comparators: There are several applications, but we are looking at the following two only: 1. Positive Peak Detector 2. Zero Crossing Detector Driving MOS Logic Experiment Procedure: 1. Positive Peak Detector a. Connect the circuit as shown in Figure 1 b. Increase the amplitude of the input for various waveforms (sine, square, triagle) and note the output waveform. Measure the positive peak value and output voltage value by using an oscilloscope. c. Draw the waveforms and write your comments. d. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 2. Zero Crossing Detector a. Connect the circuit as shown in Figure 2 b. Change the circuit frequency of the signals for various waveforms (sine, square, and triangle) and note the particular reading when the comparator detects the zero crossing point reading. c. Draw the waveforms and write your comments. d. Simulate the circuit using Pspice. Compare the Pspice results with those obtained in the previous parts. 22 15V R1 2 2k . 8 0 + LM311 7 . Vin 3 Internally Shorted 1 . 4 . - LM310N . R3 3 + R2 + 10k C1 1.5n 1000k 15V 0 0 0 Figure 1: Positive Peak Detector R2 3k 5V 0 2 LM311 . . - . 6 7 1 R3 10k To MOS Logic 4 3 . Vin + . . 8 5 R1 3k 0 0 -10V 0 -10V 0 0 Figure 2: Zero Crossing Detector Driving MOS Logic 23 6