* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Comparison of Simulation Results Three Level and Five Level H

Stepper motor wikipedia , lookup

Audio power wikipedia , lookup

Electronic engineering wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electrical ballast wikipedia , lookup

Power engineering wikipedia , lookup

Current source wikipedia , lookup

History of electric power transmission wikipedia , lookup

Three-phase electric power wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Electrical substation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Distribution management system wikipedia , lookup

Surge protector wikipedia , lookup

Stray voltage wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Voltage regulator wikipedia , lookup

Alternating current wikipedia , lookup

Opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Mains electricity wikipedia , lookup

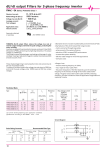

Comparison of Simulation Results Three Level and Five Level H-bridge Inverter and hardware implementation of Single Leg H-Bridge Three Level Inverter ISSN 2319-9725 Mamta N. Kokate M-Tech (Student): Dept. of Electrical Engg Ramdeobaba College of Engineering and Management Nagpur, (India) Prof. Preeti V. Kapoor Assistant Professor, Dept. of Electrical Engg Ramdeobaba College of Engineering and Management Nagpur, (India) Abstract: The conventional two level inverter has many limitations for high voltage and high power application. Multilevel inverter becomes very popular for high voltage and high power application. The multilevel began with the three level converters. The elementary concept of a multilevel converter to achieve higher power to use a series of power semiconductor switches with several lower voltage dc source to perform the power conversion by synthesizing a staircase voltage waveform. However, the output voltage is smoother with a three level converter, in which the output voltage has three possible values. This results in smaller harmonics, but on the other hand it has more components and is more complex to control. In this paper, study of different three level inverter topologies and SPWM technique is explain and SPWM technique has been applied to formulate the switching pattern for three level and five level H-Bridge inverter that minimize the harmonic distortion at the inverter output. This paper deals with comparison of simulation results of three level and five level H-Bridge inverter and implementation of single leg of three level H-Bridge inverter. Keywords: Topologies of Multilevel inverter, Sinusoidal Pulse Width Modulation, THD. April, 2013 www.ijirs.com Vol 2 Issue 4 1. Introduction: The conventional voltage source inverters produce an output voltage at the poles with levels +V dc/2 or –Vdc/2 , where Vdc is the DC link voltage are known as two level inverter. To obtain a quality output voltage or a current waveform with a minimum amount of ripple content, they require high switching frequency along with various pulse width modulation strategies. In high voltage and high power application these two level inverters however, have some limitations in operating at high frequency mainly due to switching losses and constraint of device rating. Multilevel inverters have been attracting in favor of academic as well as industry in the recent decade for high-power and medium-voltage energy control. In addition, they can synthesize switched waveforms with lower levels of harmonic distortion than an equivalently rated two-level converter. The multilevel concept is used to decrease the harmonic distortion in the output waveform without decreasing the inverter power output. This paper presents the most important topologies like diodeclamped inverter (neutral- point clamped), capacitor-clamped (flying capacitor), and cascaded multilevel with separate dc sources. Multilevel inverter is based on the fact that sine wave can be approximated to a stepped waveform having large number of steps. The steps being supplied from different DC levels supported by series connected batteries or capacitors[1][2]. The unique structure of multi- level inverter allows them to reach high voltages and therefore lower voltage rating device can be used. As the number of levels increases, the synthesized output waveform has more steps, producing a very fine stair case wave and approaching very closely to the desired sine wave. It can be easily understood that as motor steps are included in the waveform the harmonic distortion of the output wave decrease, approaching zero as the number of levels approaches infinity. Hence Multi- level inverters offer a better choice at the high power end because the high volt- ampere ratings are possible with these inverters without the problems of high dv/dt and the other associated ones [2] 2. Multilevel Inverter Topology: The basic three types of multilevel topologies used are [3]-[4]: i. Diode clamped multilevel inverters ii. Flying capacitors multilevel inverter or capacitor clamped multilevel inverter iii. Cascaded inverter with separate DC sources. International Journal of Innovative Research and Studies Page 389 www.ijirs.com April, 2013 Vol 2 Issue 4 2.1 Diode Clamped Multilevel Inverters: The diode clamped multilevel inverter uses capacitors in series to divide up the dc bus voltage into a set of voltage levels. To produce n levels of the phase voltage, an n level diode clamp inverter needs (n-1) capacitors on the dc bus. A1 C C1 B1 Vdc 2 D1 A2 D1 B2 D1 C2 VA VB VC O Vdc D2 C A1 Vdc 2 D2 B1 D2 C1 A1 A2 B2 C2 Figure 1: Diode Clamped Three Level Inverters In this paper, diode clamped multilevel inverters topology is used shown in fig 1. 2.2 Flying Capacitor Multilevel Inverter: It uses ladder structures of dc side capacitors where the voltage on each capacitor differs from that of the next capacitor. To generate n- level staircase output voltage, (n-1) capacitors in the dc bus are needed. The size of the voltage increment between two capacitors determines the size of the voltage levels in the output wave. International Journal of Innovative Research and Studies Page 390 www.ijirs.com April, 2013 C Vol 2 Issue 4 A1 B1 C1 A2 B2 C2 Vdc 2 O C2 C1 C3 VA VB VC Vdc A1 C Vdc 2 B1 C1 B2 C2 A1 A2 Figure 2: Flying Capacitor Three Level Inverter 2.3 Cascaded Inverters With Separate DC Source: This inverter is nothing but the series connection of single connection of single phase inverters with separate dc source. This inverter can be avoiding the extra clamping diodes or voltage balancing capacitors. VA A1 VB B1 A2 Vdc VC B2 Vdc A1 A2 C1 C2 C1 C2 Vdc B1 B2 N Figure 3: Cascaded Inverters with Separate DC Source International Journal of Innovative Research and Studies Page 391 www.ijirs.com April, 2013 Vol 2 Issue 4 3. Control Technique: The sinusoidal PWM technique is very popular for industrial converters. Fig4. Shows the general principle of SPWM, where an isosceles triangle carrier wave of frequency fc is compared with the fundamental frequency f sinusoidal modulating wave, and the points of intersection determine the switching points of power devices.[7]-[8] Figure 4: Control Pulse Generation for Three Figure 5: Control Pulse Generation for Five Level SPWM Level SPWM Three level pulse width modulated waveforms can be generated by sine carrier PWM. Sine carrier PWM is generated by comparing the reference control signals with two triangular carrier waves as shown in fig: 4, similarly pulse generation for five level inverter is generated by comparing the reference control signals with four triangular carrier wave shown in fig: 5 Vio = Vdc/2, when A1 =A2 =1 Vio = 0, when A1=1 A2 =0 or A1=0 A2 =1 Vio = -Vdc/2, when A1 =A2 =0 Where i = a, b or c The reference control signals are phase shift 120 degree each other with same amplitude for three phase system. Two carrier waves are in phase each other with dc voltage offset. Two important parameters of the design process are amplitude modulation index ma = Vr/Vc, International Journal of Innovative Research and Studies Page 392 www.ijirs.com April, 2013 Vol 2 Issue 4 where Vr is the amplitude of reference control signals, Vc is the peak amplitude of the carrier wave, and the frequency modulation index mf = fc/fr where fc is the frequency of the carrier wave and fc is the carrier frequency. 4. Simulation Results: Simulation of three phase H-bridge inverter using sinusoidal pulse width modulation was carried out with the help of “MATLAB”. Simulation was carried out to observe the improvement in the line voltage THD for RL load of three level and five level H-bridge inverter and it also observed that the output is nearly equal to sine wave. Table 1: Inverter parameters DC Bus Voltage 100 V Carrier frequency 1 kHz Figure 6: Phase Voltage of 3-Level Inverter International Journal of Innovative Research and Studies Figure 7: Phase Voltage of 5-Level Inverter Page 393 April, 2013 www.ijirs.com Vol 2 Issue 4 Figure 8: Output Voltage of 3-Level Inverter Figure 9: Output Voltage for 5-level Inverter Figure 10: Harmonic spectrum Line Voltage of 3-level inverter for R=10ohm and L=10H International Journal of Innovative Research and Studies Page 394 www.ijirs.com April, 2013 Vol 2 Issue 4 Figure 11: Harmonic spectrum Line Voltage of 5-level inverter for R=10ohm and L=10H 5. Hardware Implementation Of Single Phase Three Level Inverter: The main steps which are followed while implementation of hardware is explain as below: i. CONTROL CIRCUIT ii. DRIVER CIRCUIT iii. POWER CIRCUIT 6. Design of Control Circuit: Figure 12: Basic Scheme For Control Circuit International Journal of Innovative Research and Studies Page 395 April, 2013 www.ijirs.com Vol 2 Issue 4 Figure 13: Triangular Wave Generating Circuit Figure 14: Setup for Triangular wave Generation Circuit International Journal of Innovative Research and Studies Page 396 April, 2013 www.ijirs.com Vol 2 Issue 4 Figure 15 Figure 16: Output of Control Circuit International Journal of Innovative Research and Studies Page 397 April, 2013 www.ijirs.com Vol 2 Issue 4 7. Design Of Deadband And Opto-Isolator Circuit (Driver Circuit): Deadband circuitry allows accurate control of the deadband time to eliminate cross conduction. Figure 17: deadband circuit while falling edge Figure 18: deadband circuit while rising edge International Journal of Innovative Research and Studies Page 398 www.ijirs.com April, 2013 Vol 2 Issue 4 Figure 19: Pin Diagram of Driver IC (TLP 250) For providing opto-isolation between the power stage and the drive signal stage, the opto-isolator driver IC TLP 250 is used. Following reasons justify the advantages of using TLP 250. i. Input threshold voltage current If = 5mA (max) ii. Supply Voltage 10V-35V iii. Output Peak current 2A iv. Response speed 0.5µs v. Isolation voltage 2500Vrms Figure 20: Output of Driver Circuit with Deadband International Journal of Innovative Research and Studies Page 399 www.ijirs.com April, 2013 Vol 2 Issue 4 8. Design Of Power Circuit: Figure 21: Design of Power Circuit Figure 22: Final Setup International Journal of Innovative Research and Studies Page 400 www.ijirs.com April, 2013 Vol 2 Issue 4 Figure 23: Output of Single Phase Three Level Inverter 9. Conclusion: LEVEL Thee Level % THD 42.02 Five Level 21.63 Table 2: % THD analysis From this analysis, it has shown that decrease in THD from three level inverter to five level inverter. In this paper the performance of both inverters was tested using RL load in MATLAB simulation. The simulation of the inverter namely Three Level and Five level H-bridge Inverter has been carried out, and compare it’s results and it was shown that the output voltage levels are increased as the level of inverters are increase, and output voltage approaches near sine wave, to get the higher voltage and reduced Total Harmonic Distortion. International Journal of Innovative Research and Studies Page 401 April, 2013 www.ijirs.com Vol 2 Issue 4 References: 1. Muhammad H. Rashid, “Power electronic circuits, devices and applications”, 3rd edition 2003, Pearson Education Inc., chapter 9, pp 406-430. 2. J. Rodriguez, J. Lai, and F. Peng, “Multilevel inverters: A survey of topologies, controls and applications,” IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002. 3. M. M. Renge and H. M. Suryawanshi, “Five-level diode clamped inverter to eliminate common mode voltage and reduce dv/dt in medium voltage rating induction motor drives,” IEEE Trans. Power Electron., vol. 23,no. 4, pp. 1598–1607, Jul. 2008. 4. Kapil Jain, Pradyumn Chaturvedi , “ MATLAB -based Simulation & Analysis of Three -level SPWM Inverter” International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-2, Issue-1, March 2012,pp. 56-59 5. L. M. Tolbert, F. Z. Peng, and T. Habetler, “Multilevel Converters for Large Electric drives,” IEEE Trans. Ind. Applicat.,vol.35,pp. 36-44, Jan./Feb. 1999. 6. T.Prathiba, P.Renuga “A comparative study of Total Harmonic Distortion in Multilevel inverter topologies in the paper” Journal of Information Engineering and Applications ISSN 2224-5782 (print) ISSN 2225-0506 (online) Volume- 2, No.3, 2012, pp.26-36. 7. Pardasani Hitendra K. Arora Kapildev N. “Simulation of Three Level Inverter Using Sinusoidal Pulse Width Modulation Technique by MATLAB” in National Conference on Recent Trends in Engineering & Technology. 8. B.Shanthi and S.P.Natarajan, “Comparative Study on Carrier Overlapping PWM Strategies for Five Level Flying Capacitor Inverter”, International Journal of Science and Techniques of Automatic control & Computer Engineering, IJ-STA,Volume 4,No.1,July 2010.pp 1158-1173 9. [9] Xiaoming Yuan, Ivo Barbi, “ Soft-Switched Three-Level Capacitor Clamping Inverter with Clamping Voltage Stabilization,” IEEE Transactions on Industry Electronics, vol. 36, no. 4,July/Aug. 2002, pp. 1165-1173 10. R. Chibani, E.M. Berkouk and M.S. Boucherit, “Input DC Voltages of Three-level Neutral Point Clamped Voltage Source Inverter Balancing Using a New Kind of Clamping Bridge”, International Journal of Computer and Electrical Engineering, Vol. 2, No. 5, October, 2010 1793-8163.pp 879-886 11. Pradyumn Chaturvedi, Shailendra Jain and Pramod Agrawal, “Modeling, Simulation and Analysis of Three-Level Neutral Point Clamped Inverter Using Matlab/Simulink/Power System Blockset”, Eighth International Conference on1223-122727-29 Sept. 2005 International Journal of Innovative Research and Studies Page 402 April, 2013 www.ijirs.com Vol 2 Issue 4 12. Santiago Cobreces, , Josep Bordonau, , Joan Salaet, Emilio J. Bueno and Francisco J. Rodriguez,“ Exact Linearization Nonlinear Neutral-Point Voltage Control for Single-Phase Three-Level NPC Converters”, IEEE Trans. on power electronics, VOL. 24, NO. 10, OCTOBER2009 13. Yang Han, Lin Xu, Gang Yao, Li-Dan Zhou, Mansoor, Chen Chen, “Operation Principles and Control Strategies of Cascaded H-bridge Multilevel Active Power Filter”, ISSN 1392 – 1215 ELECTRONICS AND ELECTRICAL ENGINEERING 2009. No. 3(91 International Journal of Innovative Research and Studies Page 403