* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download CBC early test report - Mark Raymond

Nanogenerator wikipedia , lookup

Phase-locked loop wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Oscilloscope wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Surge protector wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Index of electronics articles wikipedia , lookup

Oscilloscope history wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Radio transmitter design wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Integrating ADC wikipedia , lookup

Voltage regulator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Wilson current mirror wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

CBC test report

Change log

3/5/2011

13/5/2011

Mark Raymond

v.0 draft – not released

v.1 – contains section on leakage current tolerance

Contents

1. Introduction

1.1. Problems identified so far.

2. Digital functionality - interfaces

2.1. Fast - SLVS

2.2. Slow - I2C

3. Powering

3.1. Bias generator

currents and voltages vs. I2C setting

3.2. DC-DC switched capacitor functionality

3.3. LDO functionality

3.3.1. DC measurements

3.3.2. AC measurements

3.4. Power consumption

3.4.1. Digital

3.4.2. Analogue

3.4.3. Total

4. Analogue functionality

4.1. Amplifier

4.1.1. Pulse shape

4.1.2. Noise

4.1.3. Linearity

4.2. Comparator

4.2.1. Threshold tuning and uniformity

4.2.2. Hysteresis

4.2.3. Timewalk

4.3. Overload recovery

4.4. Leakage current tolerance

1. Introduction

The CBC appears to be working rather well – certainly well enough to achieve all the

objectives set for this prototype.

The CBC chips were delivered mid February 2011. This report documents the results

of ongoing testing in the lab and a format has been adopted that should allow updating

and addition of new information and sections, as further results and understanding of

1

behaviour arises – with figures grouped together at the ends of sub-sections rather

than inserted in the text. Since it is intended to be a continuously evolving working

document it is bound to contain errors. Note that in drawing conclusions it must be

borne in mind that most of the results come from measurements on just a few chips.

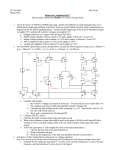

Figure 1.1 shows a functional block diagram of the CBC front end showing which

bias signals act on which block.

Figure 1.2 shows a photograph of the CBC test setup.

1.1 Problems identified so far

single dummy test channel

It has not been possible to make very effective use of this feature due to stability

issues which I initially thought were attributable to a poor layout of the CBC test

board for access to these particular pads (e.g. preamp input and output tracks running

adjacent). The dummy channel has been bonded out in a 40 pin DIL package, figure

1.3, where all pads are bonded to pins with intermediate pins grounded. The

preamplifier output works better if the postamplifier bias currents are set very low, but

at nominal bias conditions the postamplifier is still unstable, and this appears to

couple back and upset the preamp too. Figure 1.4 shows the dummy test channel

output tracking to the source followers, and off the chip. There is the possibility of

some coupling between the postamp output and input (preamplifier output), so

perhaps that is where the problem lies. Nevertheless the ability to access the

preamplifier output has provided some useful confirmation of functionality (e.g. the

expected DC shifts caused by leakage current can be verified). It would be good to

understand why the dummy channel performance is degraded.

VPAFB needs to be decoupled for stability

VPAFB biases the postamplifier feedback and is derived from IFPA using the circuit

shown in figure 1.5 where each postamplifier receives its VPAFB bias voltage via the

1 M resistor. In electrons mode the circuit behaves as expected. In holes mode a

common mode instability has been found. The following is the probable explanation.

In electrons mode the signal polarity at the preamp output and postamp input is

positive and results in a negative going signal at the postamp output. The MOSFET

MFE is selected by the switches as the feedback component. MFE and MFM together

form a current mirror, so that the current flowing in MFM (set by IFPA via VPAFB

and the 1M resistor) is the maximum current that can flow in MFE. This current can be

set to be small (~ few nA – few 10’s nA) to achieve a very high resistance. The source

of MFE is connected to the inverting input of the postamp, effectively at the same

potential as the non-inverting input (VPLUS, ~ 600 mV – half the supply rail), so the

source of MFM is also connected to VPLUS. The potentials of the sources of MFE and

MFM are essentially fixed at VPLUS so the gates are DC biased.

In holes mode the signal polarity is reversed and the switches select MFH instead of

MFE. Because of the polarity reversal the source of MFH has to connect to the

postamp output, and so the source of MFM also has to go to the postamp output. But

since the postamp output moves with the signal (positive) the gates of the current

mirror have to also go positive to ensure the correct current mirror operation, and this

2

is achieved by the 1 pF capacitor coupling the gates to the sources. In simulation this

circuit works as expected. The feedback network for an individual channel is

effectively isolated from all others by the presence of the 1 M resistor. So what is

causing a problem?

Although it has not been verified in simulation, I think I can already see what the

problem is. If you hypothesize a common mode disturbance to the chip (by whatever

mechanism) then this could result in all postamp outputs moving together. If the

postamp outputs of all channels move together then the postamp sides of the 1 M

resistors all move together (assuming holes mode – in electrons mode there is no

significant postamp output coupling to the current mirror gates). In this circumstance

the disturbance can couple to VPAFB, because the 1M resistors of all channels

effectively add in parallel to give 78k which is low compared with the impedance on

the driving side of VPAFB. A self-sustaining oscillation can therefore develop. This

needs to be verified in simulation, but stability is easily achieved in practice by adding

an external 100 nF capacitor to ground on the VPAFB bias generator pad. A better fix

needs to be found for the next version of the chip, which might just be to use a voltage

(with an acceptably low source impedance) to drive VPAFB, but this needs study.

VCTH

The global comparator threshold voltage suffers from a similar (though not identical)

problem to VPAFB. This is explained and discussed further in section 3.1.

BGO/BGI

The bandgap output (BGO) is brought off-chip and taken back on again (BGI –

neighbouring pad) to allow overriding if necessary. It is found that for better power

supply noise rejection it is necessary to decouple this voltage to ground – see section

3.3.2. In a relatively quiet system this is unnecessary.

power supply rejection

The chip is very sensitive to power supply noise in a rather narrow bandwidth centred

on 15 MHz – see section 3.3.2. It is not yet clear what is going on here.

IPAOS

There is some unexplained behaviour associated with the current bias to the

postamplifier output stage with regards to:

1) The adjustable range of this current is significantly larger than specified – see

section 3.1.

2) There is rather limited linear range in holes polarity mode which can be increased

if IPAOS is increased well above its nominal design value.

Neither of these issues is particularly dramatic, but the behaviour needs to be

understood.

3

VPAFB

polarity

VPLUS

CBC front end

Vdda

feedback

network

Ipaos2

100f

80f

pipeline

1p

16k

Vcth

2k

4k

200k

VPLUS

Ipaos1

8k

Ipaos2

IPA

92k

115k

VPLUS

16k

postamp O/P

offset adjust

IPRE1

IPRE2

IPAOS

IPSF

polarity

8-bit value

(per channel)

4-bits

hysteresis

select

Figure 1.1. CBC front end functional block diagram.

Figure 1.2. CBC test setup.

4

Ck40

500k

16k

60k

polarity

sel

GND

GND

GND

GND

DummyIn

GND

Preamp

Postamp1

GND

Postamp2

GND

Comp

GND

HitDet

VDDD

1

VPC

DATA+

VPAFB

DATA-

VPLUS

CLK+

VCTH

CLK-

Ibias

TRG+

IbiasOff BGI

BGO

VDDA

RST

SDAIN SDAOUT SCLK

TRG-

Figure 1.3. CBC bonded out into 40 pin DIL package for better dummy channel

testing.

Figure 1.4. CBC dummy test channel tracking.

5

VPLUS

1p

+

80f

s

MFE

e

e

6/0.2

1/5

2/0.2

MFH

h

s

h

1/5

switch

implementation

(NMOS enclosed)

1p

h

postamp

feedback

network

(1 per chan.)

VPLUS

e

postamp feedback bias (1 per chip)

VPLUS

~0.6V

1/5

100/5

MFM

VPAFB

1M

IFPA: 0 - 25 uA

VPAFB

Figure 1.5. Postamplifier feedback circuit.

6

2. Digital functionality

The correct digital functionality of the CBC can be verified to some extent by

applying a trigger at a fixed time following a fast reset101, for a certain programmed

latency, and checking that the value returned in the digital header is correct. With 12

clock cycles between the first ‘1’ of the reset101 and the trigger pulse, as in figure

2.1, the column address returned in the digital header of the output data stream should

be zero. This check has been made and the chip performs as expected for VDDD

values down to 0.9 Volts (VDDD = 1.2 Volts nominal) indicating that there is

significant speed margin for correct operation (speed goes as VDDD2).

Figure 2.1. Correct Ck and T1 timing to trigger on column address zero.

2.1. Fast control interface - SLVS

The 40 MHz clock to the CBC, the T1 level one trigger to the chip, and the data

stream from the chip, are all implemented using the scalable low voltage signalling

standard (SLVS) using a circuit supplied by CERN1. This circuit has provision to

programme different bias settings for the transmitter to control the amplitude (and

bandwidth) of the differential signal. Figure 2.1.1 shows the CBC output frame header

(DATA+/-) for minimum, nominal (default) and maximum bias settings, where all

three settings can produce clean signals for the 40 Mbps data stream.

2.2. Slow control interface - I2C

The slow control interface has been verified operational at 100 kHz speed only. The

functioning of only one bonded address has so far been verified.

1

E-link: A Radiation-Hard Low-Power Electrical Link for Chip-to-Chip Communication, S. Bonacini

et al, TWEPP-09, Paris, France, 21 - 25 Sep 2009, pp.422-425

7

MINIMUM BIAS

0.35

0.30

0.25

0.3

DATADATA+

0.2

(DATA+) - (DATA-)

0.1

0.20

0.0

0.15

-0.1

0.10

-0.2

0.05

-0.3

0.00

NOMINAL BIAS

0.35

0.3

0.30

0.2

Volts

0.25

0.1

0.20

0.0

0.15

-0.1

0.10

-0.2

0.05

-0.3

0.00

MAXIMUM BIAS

0.35

0.3

0.30

0.2

0.25

0.1

0.20

0.0

0.15

-0.1

0.10

-0.2

0.05

-0.3

0.00

50 nsec. / division

Figure 2.1.1. SLVS fast control interface signals. MINIMUM, NOMINAL and

MAXIMUM bias settings correspond to 0.5 mA, 2 mA and 2.5 mA respectively.

8

3. Powering

3.1. Bias generator

Figure 3.1.1 shows a measurement of the bias generator currents dependence on

register setting. The measurements were made by monitoring the voltage developed

across a 1 kOhm resistor connected between the bias generator monitoring pad on the

bottom edge of the chip and the appropriate supply rail. The CBC was powered via

the on-chip LDO regulator (more detailed functionality measurements of the LDO can

be found in section 3.3). The measured bandgap reference voltage was 604 mV and

the LDO output voltage was 1.097 V. Two set of data are displayed for both internal

(solid coloured lines) and external (dashed lines) master reference current generation.

The external reference current was adjusted to be 64 A so the very close

correspondence of the two sets of curves implies that the internal value must also be

very close to 64 A.

The linearity is not great, but is not expected to be. What is perhaps more surprising is

that there are discontinuities at some of the binary transition points (e.g. 127 to 128,

and elsewhere) which ought not to be there since the method used to produce these

currents is, in principle, monotonic. This needs further investigation, though the effect

is relatively small and unlikely to be an operational issue.

While the method of performing the measurements in figure 3.2.1 is ok for studying

the currents produced by the bias generator in isolation, it is not equivalent to the

situation in the chip where the bias generator output currents are further mirrored into

the individual channels. To investigate this behaviour the current in the VDDA power

rail dependence on I2C register setting was measured. All other current bias settings,

apart from the one under study, were set to nominal values. The resulting data were

scaled by subtracting the zero I2C setting value and then dividing by the number of

channels to get the current-per-channel value, as shown figure 3.1.1. The results are

shown in figure 3.1.2, where the actual currents produced in the individual channels

are different to the picture in figure 3.1.1.

The full-scale currents values achieved in figure 3.1.2 are compared with the

predictions from the final design review simulations in table 3.1.1. While there is no

cause for concern, several of the measured values are outside the simulated range and

this should be further investigated and understood.

Table 3.1.1. Comparison of full-scale bias generator currents with simulation.

current register

user guide [uA]

simulated range

measured [uA]

[uA]

IPRE1

255

215 – 270

220

IPRE2

51

42 – 57

53

IPSF

51

44 - 51

36

IPA

51

30 – 49

40

IPAOS

12.7

11.5 - 15

74

ICOMP

12.7

36 – 54

34

9

Figure 3.1.3 shows a measurement of three of the bias generator voltage dependences

on I2C register setting. VPC and VPLUS are implemented by mirroring a current into

a resistor, and the voltage range covered is consistent with what is expected from

simulation. VPAFB is not a simple voltage setting, but the voltage across a gate-drain

connected NMOS transistor which biases the feedback network to the postamplifier

(figure 1.4). VPAFB is generated from the IFPA I2C register setting. The range

covered is consistent with simulation.

Figure 3.1.4 shows a measurement of the VCTH bias generator voltage (comparator

global threshold) dependence on bias register setting. The behaviour designated “no

extra resistor” is the normal behaviour, where there is an abrupt discontinuity as the

voltage ramps up, and the voltage saturates at a high level ~ 1 Volt. This is clearly

undesirable, but can now be understood by the following explanation.

Figure 3.1.5 shows the on-chip circuit which is used to convert a current Ibias to a

voltage Vout which is in this case VCTH, the global comparator threshold. The pulldown capability of this circuit is governed by the 25.5 uA current sink at the output.

Figure 3.1.6 shows a functional schematic of the CBC comparator with the resistors

which implement the hysteresis. If VCTH is lower than the Postamp output then the

node Nint is low and the resistor network will draw current from VCTH. The amount

of current that the circuit in figure 3.1.5 can deliver has no hard limit. When VCTH

exceeds the Postamp output voltage Nint goes high and will supply current to VCTH.

But the total current that VCTH can sink is 25.5 uA, which is easily exceeded if

enough comparator channels switch simultaneously, and so the VCTH node gets

pulled high. The point at which this should occur is the quiescent point of the postamp

output, which was set at 600 mV in this case. The fact that VCTH doesn’t reach 600

mV before this occurs in figure 3.1.4 is probably due to the comparators triggering on

noise, probably due to the I2C activity.

The blue curve in figure 3.1.4 confirms the above explanation, because the addition of

a 5.1k resistor (effectively in parallel with the 25.5 uA) allows the current-to-voltage

circuit to sink sufficient current, and the abrupt discontinuity and saturated behaviour

goes away. This perhaps points to a solution to the problem (the resistor could be

integrated on the chip), but there is still some distortion in the curve around the point

where all comparator outputs change state, so further design study is needed to

determine if a solution like this is good enough, or whether a better solution is

required. In normal operation not all comparator outputs switch simultaneously, of

course.

A good workaround for controlling VCTH is to overdrive the bias generator output

with an external DAC, and this is the method used for the measurements in the reset

of this report. An I2C DAC with high precision (< 1 mV) was used which has turned

out to be very useful for precision performance measurements.

10

Figure 3.1.1. Bias generator currents dependence on register setting for external

reference current (coloured lines) and internal Iref (black dashed lines superimposed).

IPRE1 relates to the left hand side axis: All other curves relate to the right side axis.

11

225

90

IPRE1

IPRE2

IPSF

IPA

IPAOS

ICOMP

200

70

150

60

125

50

100

40

75

30

50

20

25

10

0

0

50

100

150

200

All other currents [microamps]

IPRE1 current [microamps]

175

80

0

250

I2C register setting

Figure 3.1.2. Bias generator currents dependence on register setting deduced from the

current in the VDDA rail. IPRE1 relates to the left hand side axis: All other curves

relate to the right side axis.

12

Figure 3.1.3. Bias generator voltages dependence on register setting for external

reference current (coloured lines) and internal Iref (black dashed lines superimposed

Figure 3.1.4. VCTH bias generator voltage dependence on register setting for external

reference current (coloured lines) and internal Iref (black dashed lines superimposed

13

Figure 3.1.5. On-chip circuit which converts current Ibias to voltage Vout.

Figure 3.1.6. Functional schematic of CBC comparator.

14

3.2 DC-DC switched capacitor functionality

Figure 3.2.1. shows the copper pattern on the CBC PCB indicating the locations of

capacitors. Voltages were probed on the CBC board with a differential probe as close

as possible to the bonds (approximate probe points are indicated by the yellow stars).

One side of the probe was on the voltage, the other on the nearest ground area.

Figure 3.2.2 shows some transient voltages measured with the differential probe. The

conditions for this measurement were the following:

DC-DC switching frequency: 1.25 MHz (derived from 40 MHz)

DC-DC voltage in: 2.518 V @ 14.2 mA

DC-DC voltage out: 1.200 V @ 26.4 mA

=> efficiency (for these particular conditions): 89%

Bandgap voltage input to LDO: 590 mV

LDO output voltage: 1.066 V

The difference between the blue and red waveforms in figure 3.2.2 can only be

attributed to the different local impedances present at the two locations, since the

voltages should be the same. Since the differential probe method measures the

difference between the point being probed and the nearest ground area it is possible

that the disturbance is actually on the ground rather than the probe point, but the

ground is a solid plane underneath the chip and on the other side of the board.

Another possibility is that the probe picks up more radiated interference when it is

nearer the DC-DC converter itself. Figure 3.2.3 shows an expanded timescale picture

of one of the transient disturbances in figure 3.2.2.

Figure 3.2.4 shows the dependence of the DC-DC output voltage as a function of the

current drawn from the DC-DC input voltage. Note that the current drawn on the

output (lower voltage) side would be approximately twice that shown on the x-axis in

the figure.

15

Figure 3.2.1. CBC PCB pattern showing locations of capacitors on power circuitry

outputs and inputs and differential probe points (yellow stars). The blue wire link

connects the DC-DC output to the LDO input.

1.30

1.25

Volts

1.20

1.15

DC-DC output

LDO input

LDO output

1.10

1.05

0

1

2

3

4

5

6

7

microseconds

Figure 3.2.2. Transient waveforms associated with the switched capacitor DC-DC

voltage converter

16

1.30

1.25

Volts

1.20

1.15

DC-DC output

LDO input

LDO output

1.10

1.05

3.50

3.55

3.60

3.65

3.70

3.75

3.80

microseconds

Figure 3.2.3. Transient waveforms associated with the switched capacitor DC-DC

voltage converter - expanded time-scale

1.4

1.2

Volts

1.0

0.8

0.6

0.4

0.2

0.0

0

5

10

15

20

25

30

Current drawn from 2.519 Volt supply [mA]

Figure 3.2.4. DC-DC output voltage dependence on current drawn

17

35

3.3. LDO functionality

3.3.1. DC measurements

Figure 3.3.1.1 shows the dependence of the LDO output on input voltage, for two

different load currents, and also the bandgap voltage. The bandgap voltage for this

chip is very close to 0.6 Volts and varies by only 1 mV between 1.0 and 1.5 Volts.

Figure 3.3.1.2 shows a magnified view of the LDO output voltages in the dropout

region where the dropout voltages are approximately 20 and 40 mV for the 30 and 60

mA load cases respectively. The line regulation is 0.6% for the 60 mA load case,

which corresponds to an increase of 0.6 mV in output voltage for an input voltage

change of 1.15 to 1.25 Volts.

Figure 3.3.1.3 shows the load regulation performance of the LDO where the output

voltage changes by 5 mV for a 60 mA change in the load current.

1.2

dropout

1.1

volts

1.0

bandgap voltage

LDO out (30 mA load)

LDO out (60 mA load)

0.9

0.8

0.7

0.6

0.5

0.8

0.9

1.0

1.1

1.2

1.3

1.4

1.5

LDO input voltage [V]

Figure 3.3.1.1. LDO and bandgap output voltages dependence on LDO input voltage.

18

dropout & line regulation

1.10

volts

LDO out (30 mA load)

LDO out (60 mA load)

1.05

1.05 1.10 1.15 1.20 1.25 1.30 1.35 1.40 1.45 1.50

LDO input voltage [V]

Figure 3.3.1.2. Expanded view of LDO output dependence on input voltage in dropout

region.

Figure 3.3.1.3. LDO output voltage dependence on load current.

19

3.3.2. AC measurements

The primary reason for including the LDO circuit in the CBC was to improve the

power supply rejection by using it to provide a “clean” regulated voltage to the

analogue front end circuitry from an external supply that could be potentially noisy.

Figure 3.3.2.1 shows the dependence on frequency of the peak-to-peak amplitudes of

the sinusoidal waveforms present on the LDO input and output. For these

measurements the LDO sinusoidal input voltage was supplied by a function generator

with a DC offset of ~ 1.25 V. The function generator had a 50 Ohm output impedance

and so the amplitude at the LDO input voltage (green symbols) has a dependence on

frequency. The LDO input and output voltages were monitored using the differential

probe technique described in section 3.2.

The red symbols in figure 3.3.2.1 show the LDO output amplitude and a reduction in

amplitude, compared with the input, is visible, but the rejection is much poorer than

expected at frequencies in the 104 - 106 Hz range where the LDO regulation should be

particularly effective. After some consideration and experimentation it was found that

this could be completely removed by decoupling the bandgap reference voltage with

an external capacitor (an arbitrary value of 10 uF was used). This makes sense since

the bandgap is also supplied by the LDO input voltage. The workaround of externally

decoupling this voltage can be effectively used for this version of the chip, but an

alternative approach needs to be found for the future (maybe a long time-constant onchip RC filter?).

Figure 3.3.2.2 shows the PSRR expressed in dB using the relation:

PSRR = 20log10{ (LDO O/P with BG decoupled) / (LDO I/P) }

The rejection is good at frequencies below 1 MHz, but begins to get poorer at higher

frequencies. It would have been better if the range of measurement had been extended

to higher frequencies, as it is not clear whether a peak has been reached, but the

function generator used here could not supply a big enough signal to higher

frequencies to be studied, where the impedance of the system becomes low and most

of the signal is dropped across the internal 50 Ohm series resistance. This will need to

be re-visited.

To investigate further the dependence of channel noise on LDO input disturbance

frequency was studied. As before the LDO input (VLDOI) was supplied by a signal

generator. For a specific frequency the signal generator output amplitude was adjusted

to obtain 10 mV peak-to-peak amplitude on VLDOI. The S-curve for an arbitrary

input channel was then taken and the noise computed. Figure 3.3.2.3 shows the results

with and without the decoupling capacitor on the bandgap reference voltage. The

decoupling can be seen to remove the broad feature centred on 100 kHz which was

also observed in figure 3.3.2.1. But there is another striking feature centred on 15

MHz which is not much affected by the decoupling. The S-curves were observed to

be significantly distorted when the input disturbance was close to the central

frequency.

The effect was investigated further by deducing the impedance at the VLDOI input,

which was calculated from the amplitude of the function generator signal required to

20

achieve the 10 mV disturbance. This is plotted in figure 3.3.2.4, where the 15 MHz

feature can be seen to correspond to very low impedance.

At this time it is not clear what is causing the 15 MHz feature. It looks like some kind

of resonance. While low frequencies show up an issue associated with the bandgap,

could the bandgap circuit also be implicated here?

amplitude [V]

100

10

1

LDO I/P

LDO O/P

LDO O/P with BG decoupled

0.1

10

4

10

5

6

7

10

10

frequency [Hz]

Figure 3.3.2.1. Peak-to-peak AC amplitudes of LDO input and output voltages.

-10

PSRR [dB]

-20

-30

-40

-50

-60

10

4

10

5

10

6

10

7

frequency [Hz]

Figure 3.3.2.2. Power supply rejection ratio calculated using PSRR=20log{(LDO

O/P)/(LDO I/P)} (using bandgap output decoupled data).

21

30

rms noise [mV]

25

no decoupling

bandgap output decoupled

20

15

10

5

0

0.001

0.01

0.1

1

10

100

VLDOI input impedance [Ohms]

frequency [MHz]

Figure 3.3.2.3. CBC channel noise dependence on frequency of sinusoidal disturbance

on LDO input, with and without decoupling capacitance on the bandgap output.

100

10

1

0.1

0.001

no decoupling

bandgap output decoupled

0.01

0.1

1

10

100

frequency [MHz]

Figure 3.3.2.3. LDO input impedance dependence on frequency, with and without

decoupling capacitance on the bandgap output.

22

3.4. power consumption

The digital and analogue power rails are kept separate on the chip and so the

consumption for each rail can be separately determined.

3.4.1. digital

Supplying VDDD with a 1.2 Volt supply, table 3.4.1.1 details the currents and power

consumption depending on various bias settings

Table 3.4.1.1. Power consumption dependence on various power conditions

conditions

current from

total

power

VDDD [mA] power

/channel

[mW]

[uW]

SLVS enable off

0.4

0.48

3.75

SLVS enable on, no SLVS transmitter bias

1.9

2.28

17.8

minimum SLVS bias

2.8

3.36

26.3

nominal SLVS bias

4.0

4.8

37.5

maximum SLVS bias

4.5

5.4

42.3

Figure 3.4.1.1 shows the VDDD current dependence on the master clock frequency.

There is no measurable difference in the power consumption for different T1 trigger

rates, in the range 0 (no trigger at all) to 280 kHz.

VDDD current [mA]

4.0

3.5

3.0

2.5

2.0

0

10

20

30

40

clock frequency [MHz]

Figure 3.4.1.1. VDDD current dependence on clock frequency

The digital circuitry functions effectively down to VDDD = 0.9 Volts, based on the

fact that the correct digital header is returned following a trigger (see section 2).

23

3.4.2. analogue

The current drawn from VDDA depends on the sensor capacitance as the CBC is

designed for a range of input capacitance, and the approach adopted was to maintain

the preamplifier risetime constant, by increasing the current in the input device for

increasing sensor capacitances. In the noise results section 4.1.2 this is the technique

employed, where the CBC front end is biased in line with what was simulated. The

analogue power / channel is taken from that section, and is quoted here as:

analogue power / channel = 130 + 21.CSENSOR[pF]

[microWatts]

So for a mid-range sensor capacitance of 5 pF this gives 235 W

3.4.3. total

Combining the nominal digital and analogue power consumptions into one figure

gives:

total power / channel = 170 + 21.CSENSOR[pF]

which for a 5 pF sensor would give 275 W.

24

[microWatts]

4. analogue functionality

4.1 amplifier

In a binary readout system the front end amplifier behaviour and performance can be

inferred from measurements of S-curves, sweeping comparator thresholds and the

time of charge injection. In the CBC prototype there is also a dummy analogue

channel included with access to signals along the analogue chain via pads on the top

edge of the chip, but as yet it has not been possible to make very effective use of this

feature due to stability issues which I think are attributable to a poor layout of the

CBC test board for access to these particular pads (e.g. preamp input and output tracks

run adjacent). The dummy channel has been bonded out in a 40 pin DIL package,

where all pads are bonded to pins with intermediate pins which can be grounded,

which I believe should allow better operation and test, but this has not yet been

studied.

4.1.1. pulse shape - can infer from timewalk

I expect to be able to produce some pictures if the DIL test structure approach works.

25

4.1.2. noise

The noise performance depends on input transistor bias current and so can be

increased or reduced depending on the acceptable power consumption, but the preamp

output rise time is also dependent on input device current and so care has to be taken

not to invalidate timewalk requirements. The approach adopted here has been to bias

the input device in line with simulation.

I have measured the CBC noise performance a significant number of times now as my

understanding of the chip performance, and the best method to perform the

measurement, has progressed. It is possible to obtain some variation in performance,

but generally the noise has always been close to or within specification (less than

1000 electrons for sensor capacitance of 5 pF). I will go through the measurement

procedure used here in some detail to clarify the setup and procedure, before

presenting the results

The current in the CBC input transistor is the sum of IPRE1 and IPRE2. IPRE2 is the

current in the cascode branch and is fixed at 10 uA. IPRE1 feeds the drain of the input

device directly, and is the one that is varied to compensate for added external

capacitance Cext. Table 4.1.2.1 shows the simulated noise dependence on added

external capacitance including the values of IPRE1 used.

Table 4.1.2.1. Simulated noise dependence on external capacitance.

added external

IPRE1 simulated noise, simulated noise,

capacitance

value

electrons mode holes mode [rms

Cext [pF]

[rms electrons]

electrons]

[A]

2

55

608

626

4

87.5

767

777

6

120

878

895

8

152.5

990

995

10

185

1081

1085

A fit to IPRE1 vs. Cext gives:

IPRE1 = 22.5 + 16.25.Cext

[A]

which can be used to determine the required value of IPRE1 for different values of

externally added capacitance.

To provide different values of external capacitance some boards were made which

were plugged into the CBC test board in the place occupied by the charge injection

board in figure 1.2. The capacitors on these boards were precision 0402 components,

but it is still necessary to measure the overall capacitance since the stray tracking and

connector capacitance is not negligible, including that on the CBC test board itself.

Without going into ultimate detail of the measurement technique, the capacitance was

measured at 1 MHz with the test capacitor boards plugged into a bare CBC test board,

so all stray contributions ought to be included apart from the wire-bonds to the CBC

inputs. The results are shown in table 4.1.2.2, together with the required values of

IPRE1 calculated from the above equation. The final column in the table gives the

26

IPRE1 I2C register setting to achieve the required currents for the different capacitor

values from the measured IPRE1 current-per-channel curve in figure 4.1.2.2.

Table 4.1.2.2. Measured capacitance and required IPRE1 current and I2C setting, for

the test boards used to add capacitance to the CBC inputs.

actual mounted

measured total

IPRE1 value

IPRE1 I2C reg.

capacitance [pF] capacitance [pF] required [A] setting required

0.1

1.78

50

35

1.5

3.78

85

67

3.3

5.79

115

105

5.6

8.11

155

160

8.2

10.7

200

230

The noise can be determined from the S-curves obtained by sweeping the comparator

threshold in steps of 1 mV (using the external DAC which allows to do this with

precision). To measure an S-curve a signal has to be injected. To translate the

measured noise in rms mV to ENC it is necessary to obtain a calibration factor for the

channel under study. Since the external capacitor board occupies the position where

charge would normally be externally injected the internal capacitors connected to the

test pulse inputs must be used, but this requires that the value of the internal

capacitors be known. This can simply be done by measuring the sizes of the measured

signal amplitudes, using the mid-points of the resulting S-curves, when injecting

charge through an external calibrated capacitor with the amplitudes when injecting

charge using the external test pulse input. Using this method the internal capacitors

are found to be very close to 20 fF, and this value has been confirmed to be the same

on several chips. It is slightly larger than the 15 fF nominal design value.

Figure 4.1.2.3 shows an example of an S-curve measurement used for the noise

measurement. Two s-curves are taken for different values of injected charge, so that

the gain and noise can be calculated. The fitted S-curve is a complementary error

function and the differences between the midpoints, where the curves pass through

one half of the maximum number of events (1000 in this case) gives the gain, and the

noise is given by the sigma of the S-curve fit (maybe put in the S-curve fitting theory

here? – or maybe in an appendix).

Table 4.1.2.3. gives the results of measuring the gain and noise, by the method

described, in both electrons and holes mode The gains are approximately consistent

with expectation, although approximately 20 % down - in simulation the electrons and

holes mode gains were ~50 mV/fC and ~60 mV/fC respectively. The noise in holes

mode is consistently slightly higher, which is also to be expected as the T-network of

resistors contributes ~200 electrons more.

The noise and associated total analogue power dependences on external added

capacitance are shown graphically in figures 4.1.2.4 and 4.1.2.5 for electrons and

holes modes respectively. Simulation results are also plotted, where the values used

are for a temperature of 30 degrees. The measured noise values are in very good

agreement with simulation, although the lowest capacitance measurement is

noticeably slightly higher than expectation in both modes of operation (not clear

why). The power measurements are also slightly higher than expectation, but the

simulation result does not include anything other than the front end circuits alone.

27

Table 4.1.2.3. Gain and noise dependence on added external capacitance

electrons mode

holes mode

capacitance

gain

noise

gain

noise

added [pF]

[mV/fC]

[rms electrons]

[mV/fC]

[rms electrons]

1.78

47.0

695

37.8

720

3.78

46.7

758

37.9

794

5.79

44.7

877

37.8

898

8.11

42.6

1025

36.8

1023

10.7

40.4

1164

35.5

1196

Figures 4.1.2.4 and 4.1.2.5 show plots of the noise dependence on added input

capacitance in electrons and holes modes respectively. Included in the plots is the

total analogue power dependence.

The noise dependence on leakage current has been measured but the results are not

totally meaningful and should be re-measured more carefully. I am quite sure that the

chip sources and sinks currents up to 1 uA, but have not managed to get a good

measurement to demonstrate this yet.

28

Figure 4.1.2.1. Transistor level preamp schematic.

IPRE1 current per channel [uA]

0.20

0.15

0.10

0.05

0.00

0

50

100

150

200

250

IPRE1 I2C register setting

Figure 4.1.2.2. Deduced IPRE1 current-per-channel dependence on I2C register

setting. Values of IPRE1 I2C register setting for the required IPRE1 currents in table

4.1.2.2 are indicated.

29

2000

1.2 fC data

1.97 fC data

1.2 fC S-curve fit

1.97 fC S-curve fit

number of events

1500

1000

500

0

620

640

660

680

700

comparator threshold VCTH [mV]

Figure 4.1.2.3. Example S-curves used for noise measurements

400

electrons mode

1000

350

800

300

600

250

400

200

200

150

0

0

2

4

6

8

10

power per channel [uW]

noise [rms electrons]

1200

100

12

external capacitance [pF]

Figure 4.1.2.4. Noise and associated total analogue power dependence on added

external capacitance, measured in electrons mode. Closed symbols are measurements,

open circles are simulations.

30

400

holes mode

1000

350

800

300

600

250

400

200

200

150

0

0

2

4

6

8

10

power per channel [uW]

noise [rms electrons]

1200

100

12

external capacitance [pF]

Figure 4.1.2.5. Noise and associated total analogue power dependence on added

external capacitance, measured in holes mode. Closed symbols are measurements,

open circles are simulations.

31

4.1.3. linearity (as a function of IPAOS for holes)

Figure 4.1.3.1 shows S-curves taken in electrons mode with signals in the range 1 to 8

fC in 1 fC steps. The signals were injected using the test pulse input, and the added

channel input capacitance was 5.8 pF. Figure 4.1.3.2 plots the dependence of the Scurve midpoints on the charge signal injected. Reasonable linearity is achieved for

signals up to 8 fC, though reasonable linearity is only important in the region where

the comparator threshold will be set, which is around 1 fC.

Figures 4.1.3.3 and 4.1.3.4 show the same picture for holes mode where it is clear

that the linear range is substantially less – though still acceptable from the viewpoint

of where the threshold will be set. It is not yet clear what is going on here, as I don’t

recall seeing this limitation in simulation. There is a dependence on the quiescent

current flowing in the postamplifier output stage, because the range increases if

IPAOS is increased, as can be seen in figures 4.1.3.5 and 4.1.3.6. (some kind of slewrate effect?)

This needs to be investigated further and understood, but the lack of linear range

beyond a few fC should not compromise the overall performance of the chip.

32

100

number of events

80

60

1 fC

8 fC

40

20

0

200

300

400

500

comparator threshold VCTH [mV]

Figure 4.1.3.1. S-curves in electrons mode for signals in the range 1 to 8 fC in 1 fC

steps. Note that the S-curves are actually inverted (i.e. number of events = 100 –

number of events above threshold) to allow the same fitting routine procedure that is

used for the holes case.

600

S-curve mid-point [mV]

electrons mode

500

400

300

0

2

4

6

8

charge injected[fC]

Figure 4.1.3.2. S-curve midpoints dependence on charge signal injected for the

electrons mode of operation, from the data in figure 4.1.3.1.

33

100

IPAOS setting = 15

number of events

80

60

1 fC

8 fC

40

20

0

650

700

750

800

850

900

comparator threshold VCTH [mV]

Figure 4.1.3.3. S-curves in holes mode for signals in the range 1 to 8 fC in 1 fC steps.

IPAOS setting 15 should correspond to 10 uA in the postamplifier output stage.

850

holes mode

S-curve mid-point [mV]

800

750

700

650

600

0

2

4

6

8

charge injected[fC]

Figure 4.1.3.4. S-curve midpoints dependence on charge signal injected for the holes

mode of operation, from the data in figure 4.1.3.3.

34

100

holes mode

IPAOS setting = 45

number of events

80

60

8 fC

1 fC

40

20

0

650

700

750

800

850

900

comparator threshold VCTH [mV]

Figure 4.1.3.5. S-curves in holes mode for signals in the range 1 to 8 fC in 1 fC steps.

IPAOS setting 45 should correspond to 20 uA in the postamplifier output stage.

850

S-curve mid-point [mV]

800

holes mode

IPAOS = 45

750

700

650

600

0

2

4

6

8

charge injected[fC]

Figure 4.1.3.6. S-curve midpoints dependence on charge signal injected for the holes

mode of operation, from the data in figure 4.1.3.5.

35

4.2. comparator

4.2.1. threshold tuning and uniformity

Figure 4.2.1.1 shows the S-curves obtained for 64 channels on a CBC, where all

channel offset registers (the registers which allow for tuning the offsets at the

postamplifier outputs) are set to zero. The S-curves were measured in holes mode,

with an injected signal of approximately 1 fC. The figure illustrates the comparator

threshold mis-matching but will also include any mis-match in the charge injection

capacitors across the chip. The peak-to-peak spread is < 30 mV which is less than 1

fC.

Figure 4.2.1.2. shows the S-curves for 16 channels with channel offset values of 0 and

255, illustrating that the adjustment range in this case is approximately 80 mV, but

this will depend on the value of IPAOS programmed. The value programmed should

be equivalent to 10 uA, which should lead to an adjustment range of 200 mV. The fact

that it is smaller suggests that the actual value of IPAOS is smaller. This needs further

investigation, but there was also something strange going on in table 3.1.1 where the

bias generator performance was measured, and there is also the lower than expected

linear range (holes mode) that is IPAOS dependent in section 4.1.3. (hmmm…).

Figure 4.2.1.3 shows the S-curves after tuning the channel offsets individually. The

values required for the individual channels are shown in table 4.2.1.1 along with the

S-curve mid-points before and after tuning. Plotting the S-curve mid-points before

tuning dependence on the value required to achieve matching in figure 4.2.1.4 shows

some correlation as would be expected.

Table 4.2.1.1.S-curve mid-points before and after tuning, and the channel offset

settings used for tuning, to get the matching in figure 4.2.1.3.

channel

S-curve mid-point

channel offset I2C

S-curve mid-point

value before tuning

setting required for

value after tuning

[mV]

tuning

[mV]

7

664.7

71

689.9

15

661.9

69

689.2

23

673.3

37

689.3

31

676.1

36

689.7

39

672.2

37

689.0

47

665.4

57

689.4

55

677.9

33

689.5

63

663.8

82

688.9

71

671.4

50

689.3

79

671

50

689.6

87

672.3

47

689.3

95

667.8

45

689.5

103

655.4

85

689.1

111

653.6

107

689.3

119

679.4

20

689.3

127

659.8

90

689.9

36

number of events

200

channel offsets = 0

150

100

50

0

640

650

660

670

680

690

700

comparator threshold VCTH [mV]

Figure 4.2.1.1. S-curves for 64 channels, channel offsets = 0.

number of events

200

channel

offsets

= 255

channel

offsets

=0

150

100

50

0

640

660

680

700

720

740

760

780

comparator threshold VCTH [mV]

Figure 4.2.1.2. S-curves for 16 channels, channel offsets = 0 and 255.

number of events

200

channel offsets tuned

150

100

50

0

640

660

680

700

720

740

760

comparator threshold VCTH [mV]

Figure 4.2.1.3. S-curves for 16 channels, after channel offset tuning.

37

780

680

S-curve midpoint [mV]

675

670

665

660

655

650

20

30

40

50

60

70

80

90

100

110

IPAOS value after tuning

Figure 4.1.2.4. S-curve midpoint before tuning vs. channel offset value required to

tune midpoints to be closely matched

38

4.2.2. hysteresis

The hysteresis functionality of the comparator is certainly functioning, but a

systematic study has not yet been performed. All results presented have used

minimum hysteresis which appears to work fine.

39

4.2.3. timewalk

The comparator output stays high while the postamplifier output signal is above

threshold, which may exceed a single bunch crossing, so to ensure that in normal

operation only one pulse is written into the pipeline, the “hit detection” logic sits

between the comparator output and the input of the pipeline and (if enabled) ensures

that only a single hit (in a single 25 ns timeslice) is recorded in the pipeline. The hit

detect functionality is illustrated in figure 4.2.3.1.

If the CBC is triggered on a single pipeline timeslice (with respect to a reset101) and

the time of charge injection is swept, then a hit will be seen in the output data if the hit

detect output is high at the time when the specific timeslice was written. This is

illustrated in figure 4.2.3.2, where only the charge injection times giving rise to the

green and brown postamp outputs result in a signal in pipeline timeslice 2. Putting it

another way, to see a hit in a specific timeslice there is an associated 25 ns wide

period (corresponding to timeslice 1 in the figure) during which the comparator must

fire, if the hit detect circuit is operated in “single” mode. In “variable” mode the

sensitive period is longer, as is illustrated in figure 4.2.3.3.

In variable mode the sensitive period will depend on signal size, since the bigger the

signal the longer it will spend above threshold. In single mode this is not the case

because the hit detect circuit constrains the comparator output pulse to 25 ns. Note

that the relative timing of 25 ns sensitive period with respect to the 40 MHz clock

phase will depend on signal size, and this is illustrated in figure 4.2.3.4. In case a) the

different size signals are injected at the same time, but because the big signal fires the

comparator sooner than the small one, the hit in the pipeline occurs in the timeslice

before. For the hits to appear in the same pipeline timeslice (timeslice 2 in the figure)

the big signal charge injection must be delayed with respect to the small one. This is

essentially the timewalk phenomenon which occurs in any system where a comparator

is fired by signals of varying sizes.

Figure 4.2.3.5 shows charge injection delay scans for signals in the range 1.25 to 10

fC, with a comparator threshold of 1 fC, in both variable and single hit detect modes

for a channel with and added capacitance of 5.8 pF. The data were taken by injecting

signals using the test pulse input for that channel. The value of VCTH required for a 1

fC threshold was determined from an S-curve scan with a 1 fC input signal.

The timewalk is taken to be the difference between the half maximum points on the

1.25 and 10 fC curves, which can be seen to be about 15 ns from the single hit detect

mode data.

Figures 4.2.3.6 and 4.2.3.7 show charge injection delay scans plots for a range of

added external capacitance. The data are pretty much what I would expect. The effect

of increasing noise with larger capacitance shows up in the turn-on and turn-off slopes

of the curves. The slight asymmetry in the single hit curves is puzzling.

40

high threshold

postamp

output

low threshold

raw

comp.

O/P

40 MHz clock

hit detect O/P

variable mode

hit detect O/P

single mode

Figure 4.2.3.1. Hit detect circuit functionality diagram

postamp

output

threshold

raw

comp.

output

40 MHz

hit

detect

output

timeslice

1

2

3

Figure 4.2.3.2. Hit detect output (single mode) timing dependence on time of charge

injection.

41

sensitive period

for observing a

hit in timeslice 3

postamp

output

threshold

raw

comp.

output

40 MHz

hit

detect

output

1

timeslice

2

3

4

5

6

Figure 4.2.3.3. Hit detect output (variable mode) timing depending on time of charge

injection.

a)

big signal

b)

small signal

big signal

small signal

raw comp.

output

40 MHz

hit in

pipeline

timeslice 1

timeslice 2

timeslice 1

timeslice 2

Figure 4.2.3.4.Relative timing of hits in the pipeline depending on signal amplitudes.

In case a) the charge injection time for both large and small signals is the same and

the big signal appears in the pipeline timeslice before the small. So if always

triggering timeslice 2 then to see comparator output from big signal it has to be

injected later as illustrated in case b).

42

1000

no. of events

800

600

1.25 fC

1.5 fC

2 fC

3 fC

10 fC

400

VARIABLE

200

0

100010

20

40

50

60

70

80

90

100

110

90

100

110

1.25 fC

charge injection delay [nsec.]

1.5 fC

2 fC

3 fC

10 fC

800

no. of events

30

600

400

SINGLE

200

0

10

20

30

40

50

60

70

80

charge injection delay [nsec.]

Figure 4.2.3.5. Charge injection delay scan in variable and single hit detection modes,

for signal sizes in the range 1.25 to 10 fC. Comparator threshold set at 1 fC. These

data taken for Cadded = 5.8 pF.

43

1000

800

600

400

Cadded

= 1.8 pF

1.25 fC

1.5 fC

2 fC

3 fC

10 fC

200

0

1000

Cadded

= 3.8 pF

800

600

400

number of events

200

0

1000

Cadded

= 5.8 pF

800

600

400

200

0

1000

Cadded

= 8.1 pF

800

600

400

200

0

1000

Cadded

= 10.7 pF

800

600

400

200

0

20

30

40 50 60 70 80 90 100

charge injection delay [nsec.]

Figure 4.2.3.6. Timewalk measured by delaying the time of charge injection with

respect to a fixed trigger time, for different values of added external capacitance. CBC

hut detections logic in SINGLE mode. Comparator threshold set at 1 fC.

44

1000

800

600

400

1.25 fC

1.5 fC

2 fC

3 fC

10 fC

Cadded

=1.8 pF

200

0

1000

800

600

400

Cadded

=3.8 pF

number of events

200

0

1000

800

600

Cadded

=5.8 pF

400

200

0

1000

800

600

Cadded

=8.2 pF

400

200

0

1000

800

600

400

Cadded

=10.7 pF

200

0

10 20 30 40 50 60 70 80 90 100 110

charge injection delay [nsec.]

Figure 4.2.3.7. Timewalk measured by delaying the time of charge injection with

respect to a fixed trigger time, for different values of added external capacitance. CBC

hut detections logic in VARIABLE mode. Comparator threshold set at 1 fC.

45

4.3. overload recovery

some rather rough measurements exist which show that the specification is probably

met, but the measurement technique needs further development to get results good

enough to show.

46

4.4. Leakage current tolerance

Figure 4.4.1 show the simple circuit used to inject leakage current and charge into a

CBC input. The current is measured across a 100 k resistor and fed via a 1 M resistor

into the CBC input. The 1 M resistor is a negligible noise source compared with the

200k resistor already in the CBC preamplifier feedback loop.

Figure 4.4.2 shows the output of the dummy channel response to a 10 fC injected

signal. The measurement was made using the CBC bonded into a DIL package (figure

1.3). The output pulse is distorted but approximately the expected shape. Switching

from electrons to holes mode shows the expected output DC shift of the preamp

output produced by the T network. Note that the preamp output also includes a

positive DC shift due to the extra source follower on the test signals – the input of the

CBC (and consequently the output in electrons mode before the source follower) sits

at approximately 200 mV, so the DC shift from the source follower is about 300 mV.

Note that the a 200k resistor in the individual devices test structure has been measured

at 204k.

It is clear that there is more headroom to tolerate leakage current in electrons mode,

but both modes are able to tolerate leakage currents of at least 1 uA, as specified.

It remains to confirm the expected noise performance with leakage current.

Measurements so far show only a very modest increase in noise, consistent with an

additional noise source due to the leakage current alone of less than 200 electrons.

This does not seem correct – simple calculations suggest something closer to 450

electrons would be expected (to be added in quadrature with the amplifier noise). This

needs to be re-measured.

47

(100 mV = 1 uA)

V

+5V

adjust

leakage

1M

100k

CBC

50 k

100 nF

I/P

GND

Cinj

-5V

50

Vin

Figure 4.4.1. Circuit to adjust leakage current and inject charge into CBC input.

1.1

3.6 uA

1.0

holes mode

0.9

0 - 1.8uA, 200nA steps

preamp output [mV]

0.8

0.7

0 uA

0.6

0.5

0 uA

0.4

electrons mode

1.8 uA

0.3

0 - 3.6uA, 200nA steps

0.2

0

100

200

300

400

500 0

[nsec.]

100

200

300

400

500

[nsec.]

Figure 4.4.2. Preamp output of dummy test channel dependence on leakage current in

both holes and electrons mode.

48