* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Impact of Temperature Fluctuations on Circuit Characteristics in

Variable-frequency drive wikipedia , lookup

Power inverter wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Flexible electronics wikipedia , lookup

Three-phase electric power wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Current source wikipedia , lookup

Thermal runaway wikipedia , lookup

Voltage regulator wikipedia , lookup

Lumped element model wikipedia , lookup

Integrated circuit wikipedia , lookup

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Stray voltage wikipedia , lookup

Rectiverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Surge protector wikipedia , lookup

Buck converter wikipedia , lookup

Voltage optimisation wikipedia , lookup

Opto-isolator wikipedia , lookup

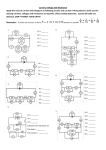

Impact of Temperature Fluctuations on Circuit Characteristics in 180nm and 65nm CMOS Technologies Ranjith Kumar and Volkan Kursun Department of Electrical and Computer Engineering University of Wisconsin – Madison Madison, Wisconsin 53706-1691 Abstract – Temperature fluctuations alter threshold voltage, carrier mobility, and saturation velocity of a MOSFET. Temperature fluctuation induced variations in individual device parameters have unique effects on MOSFET drain current. Device parameters that characterize the variations in MOSFET current due to temperature fluctuations are identified in this paper for 180nm and 65nm CMOS technologies. Operating an integrated circuit at the prescribed nominal supply voltage is not preferable for reliable circuit operation under temperature variations. A design methodology based on optimizing the supply voltage for temperature variation insensitive circuit performance is presented. Circuits display a temperature variation insensitive behavior when operated at a supply voltage 45% to 53% lower than the nominal supply voltage in a 180nm CMOS technology. Similarly, the optimum supply voltages are 68% to 69% lower than the nominal supply voltage for circuits in a 65nm CMOS technology. The optimum supply voltages are similar for a diverse set of circuits in both technologies. The proposed technique of operating large scale designs at an optimum supply voltage for diminishing the performance sensitivity to temperature fluctuations is demonstrated to be feasible. Index terms – Propagation delay fluctuations, supply voltage optimization, temperature variation. temperature range from -40°C to 150°C [9]. Temperature variations affect the device characteristics of MOSFETs thereby varying the performance of integrated circuits. Propagation delay of a circuit is a function of the drain saturation current produced by active transistors. Performance of an integrated circuit under temperature fluctuations is determined by a set of device parameters. Temperature fluctuations alter threshold voltage, carrier mobility, and saturation velocity of a MOSFET [3]. Temperature fluctuation induced variations in individual device parameters have unique effects on MOSFET drain current. The dominant parameter that determines circuit speed varies with the device/circuit bias conditions. Variation of the drain current (IDS) of NMOS and PMOS transistors with supply voltage (VDD) and temperature in a 65nm CMOS technology is shown in Fig. 1. At higher supply voltages, the drain saturation current of a MOSFET degrades when the temperature is increased. Alternatively, provided that the supply voltage is low, MOSFET drain current increases with temperature, indicating a change in the dominant device parameter. 0.10 1. INTRODUCTION _______________________________________________________________________ * This research was supported in part by a grant from the Wisconsin Alumni Research Foundation (WARF). √|IDS| (A) 4 Process and environment parameter variations in scaled CMOS technologies are posing greater challenges in the design of high performance integrated circuits. Variations can be categorized into die-to-die variations and within-die variations. Die-to-die fluctuations affect every element in an integrated circuit similarly. Alternatively, within-die variations cause a non-uniformity of physical characteristics among the devices in an integrated circuit. The accuracy of estimating the variations relates to the manufacturing cost of an integrated circuit. An overestimation of variations increases the design effort, thereby delaying the time-to-market. Alternatively, an underestimation of variations compromises the performance and functionality, thereby degrading yield. Increasing withindie parameter fluctuations and the complexity in estimating the variations require new design methodologies for suppressing the effects of process and environment parameter fluctuations in future technology generations. Because of the imbalanced utilization and diversity of circuitry at different sections of an integrated circuit, temperature can vary significantly from one die area to another [1]. Furthermore, environmental temperature fluctuations can cause significant variations in die temperature. For example, electronic systems mounted on automobile engines operate in a NMOS NMOS PMOS PMOS 0.08 0.06 at at at at 25°C 125°C 25°C 125°C 0.04 0.02 Voptimum PMOS 0.00 0.0 0.2 Voptimum NMOS 0.4 0.6 0.8 1.0 VDD (V) Fig. 1. Variation of MOSFET saturation current (IDS) with supply voltage (VDD) and temperature in a 65nm CMOS technology. |VDS| = |VGS| = VDD. Temperature dependent device parameters that determine MOSFET current characteristics in 180nm and 65nm CMOS technologies are identified in this paper. MOSFET current is characterized at elevated temperature and scaled supply voltages for two different CMOS technologies. A design methodology based on optimizing the supply voltage for temperature variation insensitive circuit performance is proposed. The optimum supply voltages for achieving temperature variation insensitive delay characteristics for a diverse set of circuits in 180nm and 65nm CMOS technologies are presented. The paper is organized as follows. Temperature dependent device parameters that determine the drain current produced by a MOSFET are identified in Section 2. Effect of temperature fluctuations on the device and circuit characteristics in 180nm and 65nm CMOS technologies are examined in Section 3. The optimum supply voltages for temperature variation insensitive circuit performance are presented in Section 4. Finally, some conclusions are provided in Section 5. 2. FACTORS INFLUENCING MOSFET CURRENT UNDER TEMPERATURE FLUCTUATIONS Device parameters that are affected by temperature fluctuations, causing variations in the drain current produced by a MOSFET, are identified in this section. BSIM3 and BSIM4 MOSFET current equations are used for an accurate characterization of temperature fluctuation induced drain current variations in deeply scaled nanometer devices. The linear and saturation region drain current of a MOSFET is [5][7] I ds ∝ I ds 0 (1) I ds 0 , R ds I ds 0 1+ V dseff ⎛ A bulk V dseff V gsteff μ eff V dseff ⎜ 1 − ⎜ 2 (V gsteff + 2V T ⎝ ∝ ⎛ ⎞ V dseff ⎜1 + ⎟ ⎜ ⎟ E L SAT eff ⎝ ⎠ ⎞ ⎟ ) ⎟⎠ (2) , where Ids, Ids0, Rds, Vdseff, Vgsteff, Abulk, µeff, VT, ESAT, and Leff are the drain current with short-channel effects, drain current of a long channel device, parasitic drain-to-source resistance, effective drain-to-source voltage, effective gate overdrive (VGSVt), parameter to model the bulk charge effect, effective carrier mobility, thermal voltage, electric field at which the carrier drift velocity saturates, and effective channel length, respectively. Threshold voltage, carrier mobility, and saturation velocity are [6]-[7] ⎛ ⎞⎛ T ⎞ KT 1L NMOS : Vt (T ) = Vt (T0 ) + ⎜ KT 1 + + Vbseff KT 2 ⎟⎜⎜ − 1⎟⎟, (3) ⎜ ⎟ L T eff ⎠ ⎝ ⎠⎝ 0 ⎛ ⎞⎛ T ⎞ KT 1L PMOS : Vt (T ) = Vt (T0 ) − ⎜ KT 1 + + Vbseff KT 2 ⎟⎜⎜ − 1⎟⎟, (4) ⎜ ⎟ L T eff ⎠ ⎝ ⎠⎝ 0 ⎛ ⎛T ⎞ μ eff (T ) = ⎜⎜ U 0 ⎜⎜ ⎟⎟ ⎝ ⎝ T0 ⎠ U te 2 ⎞⎧ ⎛ V ⎟ ⎪1 + ⎜ gsteff + 2Vt (T ) ⎞⎟ U (T ) ⎨ b ⎟ ⎜ ⎟ TOXE ⎠ ⎠ ⎪⎩ ⎝ ⎛ V gsteff + 2V t (T + (U c (T )V bseff + U a (T )) ⎜⎜ T OXE ⎝ ⎛ T ⎞ V SAT (T ) = V SAT (T 0 ) − AT ⎜⎜ − 1 ⎟⎟ , ⎝ T0 ⎠ ) ⎞ ⎫⎪ ⎟⎬ ⎟⎪ ⎠⎭ −1 , (5) (6) where Vt, KT1, KT1L, KT2, Vbseff, U0, Ute, TOXE, Ua, Ub, Uc, VSAT, AT, T0, and T are the threshold voltage, temperature coefficient for threshold voltage, channel length dependence of the temperature coefficient for threshold voltage, body-bias coefficient of threshold voltage temperature effect, effective substrate bias voltage, mobility at the reference temperature, mobility temperature exponent, electrical gate-oxide thickness, first order mobility degradation coefficient, second order mobility degradation coefficient, body effect of mobility degradation coefficient, saturation velocity, temperature coefficient of saturation velocity, reference temperature, and the operating temperature, respectively. KT1, KT1L, KT2, and AT are temperature independent empirical parameters while Ua, Ub, and Uc are temperature dependent [6]-[7]. Ua, Ub, and Uc are ⎛ T ⎞ U a (T ) = U a (T 0 ) + U a1 ⎜⎜ − 1 ⎟⎟ , T 0 ⎝ ⎠ (7) ⎛ T ⎞ U b (T ) = U b (T 0 ) + U b1 ⎜⎜ − 1 ⎟⎟ , T ⎝ 0 ⎠ (8) ⎞ ⎛ T U c (T ) = U c (T 0 ) + U c1 ⎜⎜ − 1 ⎟⎟ , ⎠ ⎝ T0 (9) where Ua1, Ub1, and Uc1 are the temperature coefficients of Ua, Ub, and Uc, respectively. As given by (3), (4), (5), and (6), absolute values of threshold voltage, carrier mobility, and saturation velocity degrade as the temperature is increased [5]-[7]. The saturation velocity is typically a weak function of temperature [3]. Threshold voltage degradation with temperature tends to enhance the drain current because of the increase in gate overdrive (VGS-Vt). Alternatively, degradation in carrier mobility tends to lower the drain current as given by (1) and (2). Effective variation of MOSFET current is, therefore, determined by the variation of the dominant device parameter when the temperature fluctuates. 3. DEVICE AND CIRCUIT BEHAVIOR UNDER TEMPERATURE FLUCTUATIONS Influence of temperature fluctuations on the device and circuit characteristics in TSMC 180nm and Berkeley Predictive 65nm CMOS technologies are evaluated in this section. Test circuits are designed for equal low-to-high and high-to-low propagation delays at 125°C. Temperature fluctuation induced gate overdrive and carrier mobility variations at the nominal supply voltage are shown in Figs. 2 and 3, respectively. The nominal supply voltages are 1.8V and 1.0V for the 180nm and 65nm CMOS technologies, respectively. For circuits operating at the nominal supply voltage, variations in gate overdrive are smaller as compared to carrier mobility variations when the temperature fluctuates in both technologies. The MOSFET current and the circuit speed, therefore, degrade as the temperature is increased in both technologies. Propagation delay variations with temperature for the test circuits operating at the nominal supply voltage in 180nm and 65nm CMOS technologies are listed in Tables I and II, respectively. Gate overdrive variations with temperature are similar in both technologies. Alternatively, variations in carrier mobility are higher for devices in the 65nm CMOS technology as compared to variations observed in the 180nm CMOS TABLE I DELAY VARIATION WITH TEMPERATURE FOR CIRCUITS OPERATING AT THE NOMINAL SUPPLY VOLTAGE (VDD = 1.8V) IN A 180NM CMOS TECHNOLOGY 16-bit 180nm Brent Domino Domino Temp CMOS Inverter NAND2 NAND4 NOR2 NOR4 XOR2 Kung AND2 OR2 (°C) Technology Adder 25 6.12E-11 6.06E-11 5.18E-11 1.28E-09 2.88E-11 9.41E-11 1.45E-10 1.21E-10 2.49E-10 Average Delay (s) 125 3.06E-11 1.10E-10 1.74E-10 1.37E-10 2.81E-10 6.79E-11 6.90E-11 5.84E-11 1.44E-09 6.4 16.6 19.6 13.2 13.0 11.0 14.0 12.8 12.6 Delay Variation (%) TABLE II DELAY VARIATION WITH TEMPERATURE FOR CIRCUITS OPERATING AT THE NOMINAL SUPPLY VOLTAGE (VDD = 1.0V) IN A 65NM CMOS TECHNOLOGY 16-bit 65nm Brent Domino Domino Temp CMOS Inverter NAND2 NAND4 NOR2 NOR4 XOR2 Kung AND2 OR2 (°C) Technology Adder 25 1.54E-11 5.62E-11 8.65E-11 6.86E-11 1.35E-10 2.82E-11 3.73E-11 2.90E-11 6.33E-10 Average Delay (s) 125 Delay Variation (%) 2.08E-11 8.52E-11 1.32E-10 1.05E-10 2.05E-10 4.12E-11 5.55E-11 4.36E-11 9.79E-10 35.0 51.6 52.6 52.4 52.1 46.1 48.9 50.2 54.5 4.9% 3.2 5.4% 37% At 25°C At 125°C 1.4 m /Vs) 1.3 2.4 2 1.2 At 25°C At 125°C 2.8 2.0 -2 1.1 1.0 4.7% 0.9 4.7% 0.8 Mobility (x10 Absolute Overdrive |GateGate Overdrive| (V) (V) _ 1.5 1.6 1.2 18% 50% PMOS NMOS 53% 0.8 0.4 0.7 0.6 0.0 NMOS PMOS NMOS 180nm PMOS 65nm CMOS Technology NMOS 180nm PMOS 65nm CMOS T echnology Fig. 2. Gate overdrive variation with temperature for devices in 180nm and 65nm CMOS technologies. Fig. 3. Mobility variation with temperature for devices in 180nm and 65nm CMOS technologies. technology. Therefore, for a die temperature spectrum of 25°C to 125°C, degradation of high temperature speed of the 65nm CMOS circuits is more significant than the speed degradation observed for the 180nm CMOS circuits, as listed in Tables I and II. When operating at the nominal supply voltage, the speed of circuits degrades by up to 19.6% and 54.5% as the temperature is increased from 25°C to 125°C in the 180nm and 65nm CMOS technologies, respectively. mobility when the temperature fluctuates [2]. A transistor biased at this optimum voltage produces a temperature variation insensitive drain saturation current, as illustrated in Fig. 1. The optimum supply voltages for various test circuits in 180nm and 65nm CMOS technologies are listed in Tables III and IV, respectively. Circuits display a temperature variation insensitive behavior when operated at a supply voltage 45% to 53% lower than the nominal supply voltage in a 180nm CMOS technology. Similarly, the optimum supply voltages are 68% to 69% lower than the nominal supply voltage for circuits in a 65nm CMOS technology. The optimum supply voltages are similar for a diverse set of circuits in both technologies. The proposed technique of operating large scale designs at an optimum supply voltage for diminishing the performance sensitivity to temperature fluctuations is, therefore, feasible. Gap between the optimum and nominal supply voltages is higher in a 65nm CMOS technology due to the significantly higher mobility variations as compared to the 180nm CMOS technology. Performance variations in a speed centric design 4. SUPPLY VOLTAGE OPTIMIZATION The results presented in Section 3 indicate that operating an integrated circuit at the prescribed nominal supply voltage is not preferable for reliable circuit operation under temperature variations. A new design methodology based on scaling the supply voltage is proposed in this paper for suppressing the current variations due to temperature fluctuations. In order to compensate for the variations of carrier mobility, the sensitivity of gate overdrive to temperature fluctuations should be enhanced by lowering the supply voltage in both technologies. At the optimum supply voltage, gate overdrive variation completely compensates the variation of carrier TABLE III OPTIMUM SUPPLY VOLTAGES FOR TEMPERATURE VARIATION INSENSITIVE PROPAGATION DELAY CHARACTERISTICS IN A 180NM CMOS TECHNOLOGY 16-bit 180nm Brent Domino Domino Temp CMOS Inverter NAND2 NAND4 NOR2 NOR4 XOR2 Kung AND2 OR2 (°C) Technology Adder Average 25 5.78E-11 3.05E-10 5.78E-10 3.01E-10 6.61E-10 1.67E-10 1.84E-10 1.47E-10 3.50E-09 Delay (s) at Optimum Supply 125 5.79E-11 3.05E-10 5.81E-10 3.01E-10 6.62E-10 1.67E-10 1.84E-10 1.47E-10 3.50E-09 Voltage Delay Variation (%) 0.09 0.14 0.50 0.22 0.13 -0.12 0.26 -0.01 0.03 Optimum Supply Voltage (V) 0.97 0.89 0.85 0.99 0.97 0.97 0.94 0.95 0.96 TABLE IV OPTIMUM SUPPLY VOLTAGES FOR TEMPERATURE VARIATION INSENSITIVE PROPAGATION DELAY CHARACTERISTICS IN A 65NM CMOS TECHNOLOGY 16-bit 65nm Brent Domino Domino Temp CMOS Inverter NAND2 NAND4 NOR2 NOR4 XOR2 OR2 (°C) Kung AND2 Technology Adder Average 25 1.82E-10 9.20E-10 1.57E-09 1.20E-09 2.36E-09 4.17E-10 6.93E-10 4.88E-10 1.12E-08 Delay (s) at Optimum Supply 125 1.81E-10 9.26E-10 1.58E-09 1.19E-09 2.38E-09 4.13E-10 6.89E-10 4.84E-10 1.12E-08 Voltage Delay Variation (%) -0.45 0.71 0.51 -0.90 0.82 -0.91 -0.46 -0.90 0.18 Optimum Supply Voltage (V) 0.31 0.32 0.32 0.31 0.31 0.32 0.32 0.32 0.32 would, therefore, be more significant in a 65nm CMOS technology when temperature fluctuates. Alternatively, low power integrated circuits with deeply scaled supply voltages can be less sensitive to temperature fluctuations. 5. CONCLUSIONS Temperature fluctuation induced propagation delay variations in CMOS integrated circuits are examined in this paper. Temperature dependent device parameters that cause variations in MOSFET drain current are identified. Variation of carrier mobility with temperature dominates the propagation delay variations in circuits operating at the nominal supply voltage for both 180nm and 65nm CMOS technologies. The MOSFET currents together with circuit switching speed degrade following the degradation of carrier mobility as the temperature is increased in both technologies. When operating at the nominal supply voltage, the propagation delay increases by up to 19.6% and 54.5% as the temperature is increased from 25°C to 125°C in 180nm and 65nm CMOS technologies, respectively. A new design methodology based on optimizing the supply voltage for temperature variation insensitive circuit performance is presented. The supply voltages which compensate the temperature fluctuation induced variations of carrier mobility and threshold voltage are identified for circuits in two different technology generations. Circuits display a temperature variation insensitive behavior when operated at a supply voltage 45% to 53% lower than the nominal supply voltage in a 180nm CMOS technology. Similarly, the optimum supply voltages are 68% to 69% lower than the nominal supply voltage for circuits in a 65nm CMOS technology. The optimum supply voltages are similar for a diverse set of circuits in both technologies. The proposed technique of operating large scale designs at an optimum supply voltage for diminishing the performance sensitivity to temperature fluctuations is, therefore, feasible. REFERENCES [1] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, “Parameter Variation and Impact on Circuits and Microarchitecture,” Proceedings of the IEEE/ACM International Design Automation Conference, pp. 338-342, June 2003. [2] R. Kumar and V. Kursun, “Voltage Optimization for Temperature Variation Insensitive CMOS Circuits,” Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, August 2005. [3] Y. Cheng, K. Imai, M. C. Jeng, Z. Liu, K. Chen, and C. Hu, “Modeling Temperature Effects of Quarter Micrometre MOSFET in BSIM3v3 for Circuit Simulation,” Semiconductor Science Technology, Vol. 12, pp. 1349-1354, November 1997. [4] Y. P. Tsividis, Operation and Modeling of the MOS Transistor, McGraw-Hill, New York, 1999. [5] Y. Cao, T. Sato, D. Sylvester, M. Orshansky, and C. Hu, "New Paradigm of Predictive MOSFET and Interconnect Modeling for Early Circuit Design," Proceedings of the IEEE Custom Integrated Circuits Conference, pp. 201-204, June 2000. [6] W. Liu et al., BSIM3v3.2.2 MOSFET Model – User Manual, Department of Electrical and Computer Engineering, University of California, Berkeley, 1999. [7] X. Xi et al., BSIM4.3.0 MOSFET Model – User Manual, Department of Electrical and Computer Engineering, University of California, Berkeley, 2003. [8] A. Bellaouar, A. Fridi, M. J. Elmasry, and K. Itoh, “Supply Voltage Scaling for Temperature Insensitive CMOS Circuit Operation,” IEEE Transactions on Circuits and Systems II, Vol. 45, No. 3, pp. 415-417, March 1998. [9] R. W. Johnson et al., “The Changing Automotive Environment: High Temperature Electronics,” IEEE Transactions on Electronics Packaging Manufacturing, Vol. 27, No. 3, pp. 164-176, July 2004.