* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download 0.0 0.5 1.0 1.5 2.0 2.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Survey

Document related concepts

Transcript

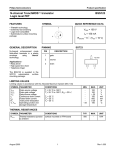

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on September 8, 2002 by Leland Chang ([email protected]) Borivoje Nikolic Homework #2 EECS 141 Due Tues., September 17th, 5pm @ 275 Cory Problem 1 – Extracting Parameters for the Unified Model Below are the I-V curves for an NMOS transistor: 5.5 Vgs=2.5V, Vbs=0V 5.0 Drain Current [mA] 4.5 Vgs=2.5V, Vbs=-1V 4.0 3.5 3.0 Vgs=2V, Vbs=0V 2.5 Vgs=2V, Vbs=-1V 2.0 1.5 Vgs=1.5V, Vbs=0V 1.0 Vgs=1.5V, Vbs=-1V 0.5 Vgs=1V, Vbs=0V Vgs=1V, Vbs=-1V 0.0 0.0 0.5 1.0 1.5 2.0 2.5 Drain Voltage [V] In this problem, the objective is to use a transfer curve like the one above to obtain information about the transistors. The transistor has (W/L)=(5/1). You may also assume that velocity saturation does not play a role in this example. Also assume –2ΦF = -0.6V From the figure above, determine the following parameters: VT0, γ, λ. Problem 2 – Showing Off Your SPICE Prowess This problem requires you to generate I-V curves for a PMOS transistor. In order to do so, you must have SPICE properly configured in your EECS instructional account. Make sure you add the following line to your deck: .lib ‘/home/ff/ee141/MODELS/g25.mod’ TT Using SPICE, generate the family of curves for a PMOS with the following parameters: W/L = 10.0u/0.25u Sweep VDS from -2.5V to 0V in 0.1V increments VGS = -0.5V, -1V, -1.5V, -1.5V, -2V, -2.5V VBS = 0V, 0.5V, 1V Problem 3 – Helping a Stanford Friend with Device Analysis A friend of yours decided to study EE at Stanford. She has taken a bunch of measurements on a transistor, but is unsure about how to extract the parameters that describe the device. Since you are taking EE141 here at Cal, you realize that you can help her with this predicament. You are also an excellent student, so you tell her that with only the information she already has, you can tell her anything and everything she might need to know about her transistor. Measurement Number 1 2 3 4 5 6 7 VGS VDS VSB ID -2.5V 1.0V -1V -2.0V -2.5V -2.5V -2.5V -2.5V 1.0V -0.8V -2.5V -2.5V -1.5V -1V 0 0 0 0 -1V 0 0 -892.5uA 0.0 -43.5uA -573.8uA -720.6uA -815.5uA -777.0uA You may assume that VDSAT = -1.0V and -2ΦF = 0.6V. a) b) c) Is the measured transistor a PMOS or an NMOS device? Explain your answer. From the measurements above, help her to determine the following parameters for this device: VT0, γ, λ. Now, to really impress your friend, you use the values you obtained in part b) to figure out the operating region at each measured data point. Possible operating regions are: “linear”, “cutoff”, “saturation”, or “velocity saturation.” Problem 4 – First Order Delay Analysis The figure below is a very atypical RTL circuit where the active device is a PMOS transistor. Way back in the day, when RTL design was popular, such circuits normally used an NMOS transistor with a resistive load. 2.5V W/L= 2µm/0.25µm Vin Vout 3kΩ 20fF Because we haven’t yet covered timing analysis using the full transistor model, you may make the following assumptions: Assume switch model behavior of the PMOS transistor. When Vin > 1.25V, the resistance of the transistor is infinite. When Vin < 1.25V, the transistor can be modeled as having a resistance of 50Ω. a) b) Determine VOH and VOL. Explain your answer. Calculate tpLH and tpHL to obtain the average propagation delay, tp. Problem 5 – Generating a Voltage Transfer Characteristic Your graduate student friends are working on a new transistor structure made out of carbon nanotubes*. Sure, it’s not silicon, but these devices that function like normal MOSFETs. They want to put their device into the RTL circuit (like in Problem 3) as shown below, in which a PMOS carbon nanotube transistor is coupled with a non-linear load device represented by the shaded box. Accompanying the figure is the I-V characteristic for this non-linear load device. 0.9V Current [mA] 0.5 Vin Vout 0.4 0.3 0.2 0.1 0.0 0.0 0.2 0.4 0.6 Voltage [V] 0.8 The carbon nanotube PMOS functions just like your standard MOSFET: Assuming a device with 100 nanotubes, data adapted from: McEuen, et al., IEEE Trans. on Nanotechnology, March 2002, pp. 78-85 -0.8 Drain Current [mA] -0.7 VGS = -0.9V -0.6 -0.5 -0.4 VGS = -0.7V -0.3 -0.2 -0.1 VGS = -0.5V VGS = -0.3V VGS = 0, -0.2V 0.0 -0.9 -0.8 -0.7 -0.6 -0.5 -0.4 -0.3 -0.2 -0.1 0.0 Drain Voltage [V] *If you’re curious, read: Collins and Avouris, “Nanotubes for Electronics,” Scientific American, Dec. 2000, pp. 62-9. a) Draw the VTC for this circuit. Determine (or estimate, if necessary, from your VTC) the following parameters: VOH, VOL, VM b) Notice that this circuit is similar to a traditional CMOS inverter, except that the nonlinear device acts as an NMOS transistor (NMOS devices are hard to make using these carbon nanotubes). From the concepts discussed thus far in lecture and from the results of your VTC, what are the disadvantages of this method?