* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download asic 2001: formatting and submitting your paper

Switched-mode power supply wikipedia , lookup

Stray voltage wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Surge protector wikipedia , lookup

Voltage optimisation wikipedia , lookup

Rectiverter wikipedia , lookup

Integrated circuit wikipedia , lookup

Opto-isolator wikipedia , lookup

Semiconductor device wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Mains electricity wikipedia , lookup

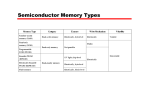

Read/Write Analysis of 8T SRAM Using 12nm Tri-Gate FinFET Technology 1Varun 1, 2, 3 1 Gupta, 2Vimal Kumar Mishra, 3Dr. R.K. Chauhan Department of Electronics and Communication Engineering Madan Mohan Malaviya University of Technology, Gorakhpur, India [email protected] , [email protected] 3 [email protected] ABSTRACT In this paper, new SRAM design for FinFET technology are proposed. The FinFET has very good candidate for future VLSI due to its simple architecture and better performance when compare to SOI MOSFET . FinFET based SRAM has been proposed as an alternative solution to the bulk device. FinFET has better scalability and better short channel effect. In this paper a study of designing and writting operation of 8T finfet SRAM using Visual TCAD tool . The high-k dielectric material is replace to dielectric.the analysis of 8T FinFET SRAM at 12nm gate length and at low supply voltage at 0.8 v. Keywords: 8-T FinFET SRAM, Potential Variation,Doping , HfO2, Read and Write. importance that this cell is scaled to minimum dimensions. However, some constraints have to be satisfied. For proper dimensioning of the cell, two basic constraints have to be satisfied. Pull Up transistors have to be weaker than Pass Gate transistors (this constraint is called write ability), and pull down (PD) transistors have to be stronger than Pass Gate transistors (readability). A write operation in SRAM is typically carried out at a WL voltage of VDD. In some cases, WL voltage can be lowered during the cell. In this paper 8T FinFET SRAM cell design and read/write operation has been studies using Visual TCAD simulation .the layout of 8T FinFET SRAM developed using K-Layout software and corresponding mask is generated using Visual TCAD shown in fig.5 & 6. I. INTRODUCTION From last 5 decades we are scaling down CMOS devices to achieve the better performance in term of speed power dissipation ,size and reliability .Variability has become increasingly troubling as the SRAM cell size is reduced ,such as short channel effect ,higher DIBL, poor sub threshold swing collectively known as SCE. The Fin type mosfet(FinFET)is one of the most desired device to scaled CMOS devise. To solve this problem 3-D device structure could be a solution . In the FinFET short channel effects are suppressed by a thin body instead of channel dopants. The 8T finfet sram is shown in fig 1 . the 8T SRAM is similar to 6T with addional 2 transister to decoupled separate read and write operation . in 6T SRAM during read operation there is potential stability problem . To overcome the problem of data storage destruction during the read operation an 8T SRAM is implemented, for which separate read/write line are used. Over the years, the 8T SRAM cell [ Fig.1] was the de facto choice for SRAM design . the need for bigger memory devices is always present , it is crucial Fig-1 circuit of 8T finfet SRAM II. FinFET Technology In this section the device architecture of tri-gate FinFET are presented,N-type FinFET with 12nm gate length are designed and simulated using Visual-TCAD. The 3-D architecture of tri-gate N-type FinFET are shown in figure-2 and figure-3 III. Proposed 8T FinFET SRAM Cell DEVICE STRUCTRURE AND SPECIFICATION Physical parameter of device is shown in Table I. Fig.2 N-type FinFET Fig. -3: FinFET Structure and Symbol The Vd-Id characteristics of N-type FinFET are shown in figure 4 Fig-4 Vd-Id characteristics of N-type FinFET Gate length Threshold voltage(Vth) Ion 12nm 0.35v 0.05mA Table I: N-type FinFET characteristics Design rule unit lambda SRAM (um) Height of fin(um) Depth of STI trench is Thickness of gate oxide (Hfo2) Well doping concentration (acceptor) for nMOS 0.006 0.08 0.2um 1.1e-3 1e17 Rmin of well doping for nMOS (um) S/D doping concentration (donor) for nMOS 0.05 3e-20 Supply Voltage Vdd 0.8 V Thickness of the buried oxide (um) 0.02 Thickness of the poly-silicon gate (um) 0.002 Thickness of the ILD dielectric (um) 0.008 S/D doping concentration (acceptor) for nMOS (cm^-3) 3e20 Lateral characteristic length of S/D doping for nMOS (um) 0.004 Vertical characteristic length of S/D doping for nMOS (um) 0.003 Doping Concentration in p-type 1e16 Doping Concentration in body 1e17 Table II: Important Device Parameters Fig-7: Potential variation in 8-T FinFET SRAM Cell Fig-5 Layout of 8-T SRAM ‘Fig-7’ shows that the net doping variation in 8T FinFET SRAM in which red color shows electon density means donor ion (Nd) and blue color shows the hole density means acceptor ion(Na) IV. SIMULATION RESULTS Fig-6: 8-T FinFET SRAM corresponding to layout Write/Read Operations . The 8T FinFET SRAM is shown has three bit line and two word line (write bit lines BL, BLB and read bit line RBL and write word line WWL, read word line RWL). During the read operation the read bit line is precharged to “1” state. A read current flow from RBL through Q7 to Q8 is Iread.this read current created voltage drop across Q8 at the point charge on RBL is drop to Vss. The write operation of 8T SRAM is similar as 6T SRAM. During the write “1” operation Q5 is on by enabling the WWL line. As the bit line is charged to logic “1” the q node start charging and turns on Q4 ,lead the qb node to logic “0”. Now qb node enable the Q1 which facilitate writing good logic “1” at node q. for writtig “0” bit line is discharge to 0 which discharge node q to “0” and turn on Q2 which flip the qbar node to logic “1”.. Fig-11: read current Write Margin Fig-8 : Read and write Cycle of 8-T FinFET SRAM Cell Write margin is the minimum bit line voltage required the flip the SRAM state. Fig-12:write margin of 8T FinFET SRAM Fig-9 : Q and Qbar of 8-T FinFET SRAM Cell Read/Write Delay The read access time of the cell is time taken for the bitlines to developed a potential difference at least 100mv. The read time is depends on the read path transistor size. The write delay for write operation is time from the 50% activation of the WWL to the time when qbar become 90% . Write delay 35.5ps Read delay 27.4ps Read current 0.2uA Write margin 450mV SNM 141.4mV Fig-10:butterflow curve for 8T FinFET SRAM Table-III: simulated result data V. CONCLUTION As the technology scales in deep nanometer era, the challenges in designing an SRAM increase substantially. The challenges arise due to increase in write, read, analysis. It is now becoming common for SRAMs to have read and write assist techniques to enable robust operation at lower supply voltages. In this work, we reviewed the read and write analysis of 8t FinFET SRAM cells across the operating range of supply voltages at 0.8V . Our analyses suggest that the wordline boosting and negative bit-line techniques seem most promising at lower supply voltages. In this work we analysis of 8T FinFET SRAM and get a mimimum write/read delay and high write margin. ACKNOWLEDGEMENT Author, wishes to thank AICTE, for this research promotion scheme (RPS-160) for developing FinFET in VLSI lab of ECE department MMMUT Gorakhpur. . REFERENCES Tawfik and Volkan Kursun “Robust FinFET Memory Circuit With P-Type Data Access Transistors For Higher Integration Density and Reduced leakage power” Journal of low power electronics vol.5,pp-1-12, 2009 . [2]. J.P. Colinge “FinFET and other Multigate [1]. SherifA. Transistor ”, Springer+Bussiness media, LLC, 2008. [3]. Andrew Carlson , Zheng Guo Sriram Balasubramanian, radu Zlatanovici , Tsu-Jae King Liu “Sram read/write Margin Enhancements Using FinFETs”, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS [4] R. V. Joshi, R. Q.Williams, E. Nowak, K. Kim, J. Beintner, T. Ludwig, I. Aller, and C. Chuang, “FinFET SRAM for high-performance lowpower applications,” in Proc. ESSCIRC, 2004, pp. 211–214. [5] Ming-HTu,Jihi-Yu Lin, Ming-chien Tsai,Shyh-Jye Jou and Ching-Te Chuang “Single ended sbthreshold SRAM with Asymmetrical Write/Read-Assist” IEEE Trans. Circuits Syst. I, Exp. Briefs, vol. 57, no. 12, pp. 3039–3047, Dec 2010. [6] K. Ohmori et al., “Impact of additional factors in threshold voltage variability of metal/high-k gate stacks and its reduction by controlling crystalline structure and grain size in the metal gates,” IEDM Tech. Dig., pp.409 - 412, 2008. [7] H. F. Dadgour et al., “Grain-Orientation Induced Work Function Variation in Nanoscale Metal-Gate Transistors –Part II: Implications for Process, Device, and Circuit Design,” IEEE TED, pp. 2515-2526, 2010. [8] A. R. Brown et al., “Impact of Metal Gate Granularity on Threshold Voltage Variability: A FullScale Three-Dimentional Statistical Simulation Study,” IEEE EDL, pp. 1199-1201, 2010. [9] Y. F. Lim et al., “Random Telegraph Signal Noise in Gate-All-Around Si-FinFET With Ultranarrow Body,” IEEE EDL, pp. 765-768, Sep. 2006. [10] A. Asenov et al., “RTS Amplitudes in Decananometer MOSFETs: 3-D Simulation Study,” IEEE TED, pp. 839-845, 2003. [11] H. H. Mueller and M. Schulz, “Random telegraph signal: An atomic probe of the local current in fieldeffect transistors,” J. Appl. Phys., p.1734, 1998. [12] S. C. Luo and L. Y. Chiou, “A sub-200-mV voltage-scalable SRAM with tolerance of access failure by self-activated bitline sensing,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 6, pp. 440–445, Jun. 2010. [13] C. T. Chuang, S. Mukhopadhyay, J. J. Kim, K. Kim, and R. Rao, “Highperformance SRAM in nanoscale CMOS: Design challenges and techniques,” in IEEE Int. Workshop Memory Technol., Des. Testing, Dec. 3–5, 2007, pp. 4–12. [14] M. Yabuuch et al., “A 45 nm low-standby-power embedded SRAM with improved immunity against process and temperature variations,” in ISSCC Dig. Tech. Papers, 2007, pp. 326–327. [15] K. Takeda et al., “A read-static-noise-margin-free SRAM cell for low-Vdd and high-speed applications,” in ISSCC Dig. Tech. Papers, 2005, pp. 478–479. .