Tuning IBM System x Servers for Performance

... 8.4.1 Physical Address Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152 8.5 64-bit memory addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155 8.6 Advanced ECC memory (Chipkill) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156 ...

... 8.4.1 Physical Address Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152 8.5 64-bit memory addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155 8.6 Advanced ECC memory (Chipkill) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156 ...

Tuning IBM System x Servers for Performance

... 3.2.1 Types of information that benchmarks can provide . . . . . . . . . . . . . 34 3.2.2 System benchmarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 3.2.3 Product-specific benchmarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 3.2.4 Industry sta ...

... 3.2.1 Types of information that benchmarks can provide . . . . . . . . . . . . . 34 3.2.2 System benchmarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 3.2.3 Product-specific benchmarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 3.2.4 Industry sta ...

Series 5000 Chip Data Book

... Series 5000 chips have a new memory architecture, for both the external memory interface and the internal on-chip memory. The external memory interface for external non-volatile memory is a serial interface using either the SPI or I2C protocol. The internal on-chip memory includes 64 KB of RAM, of w ...

... Series 5000 chips have a new memory architecture, for both the external memory interface and the internal on-chip memory. The external memory interface for external non-volatile memory is a serial interface using either the SPI or I2C protocol. The internal on-chip memory includes 64 KB of RAM, of w ...

The Linux Kernel by D.A.Rusling

... number of non-Intel Linux systems are becoming more commonly available. Amongst these are Alpha AXP, ARM, MIPS, Sparc and PowerPC. I could have written this book using any one of those platforms but my background and technical experiences with Linux are with Linux on the Alpha AXP and, to a lesser e ...

... number of non-Intel Linux systems are becoming more commonly available. Amongst these are Alpha AXP, ARM, MIPS, Sparc and PowerPC. I could have written this book using any one of those platforms but my background and technical experiences with Linux are with Linux on the Alpha AXP and, to a lesser e ...

Technology Comparison for Large Last-Level Caches

... from one of the bit-lines (BL or BLB) to ground, enabling fast differential sensing operation. When performing a write operation, the cell content is written based on the bit-lines’ differential voltage signal applied by the write driver. SRAMs can be built using standard CMOS process. They also pro ...

... from one of the bit-lines (BL or BLB) to ground, enabling fast differential sensing operation. When performing a write operation, the cell content is written based on the bit-lines’ differential voltage signal applied by the write driver. SRAMs can be built using standard CMOS process. They also pro ...

PC Hardware – a Beginner`s Guide

... Copyright © 2001 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or r ...

... Copyright © 2001 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or r ...

reducing communication cost in scalable shared memory systems

... Distributed shared-memory systems provide scalable performance and a convenient model for parallel programming. However, their non-uniform memory latency often makes it difficult to develop efficient parallel applications. Future systems should reduce communication cost to achieve better programmabi ...

... Distributed shared-memory systems provide scalable performance and a convenient model for parallel programming. However, their non-uniform memory latency often makes it difficult to develop efficient parallel applications. Future systems should reduce communication cost to achieve better programmabi ...

computer hardware

... Since EFI is able to manage its own storage space - normally envisioned as a partition on a hard disk - hardware manufacturers will be able to add many more diagnostic and control options, and include support for different kinds of computer systems and configurations, without being constrained by th ...

... Since EFI is able to manage its own storage space - normally envisioned as a partition on a hard disk - hardware manufacturers will be able to add many more diagnostic and control options, and include support for different kinds of computer systems and configurations, without being constrained by th ...

the Experience Developing Operating

... presence of processor caches, it seemed most appropriate to use the maximum interleave amount so as to make the maximum memory bandwidth available for cache reload. For our purposes, a single page table bit indicating whether a page was located in sequential memory or was interleaved across the enti ...

... presence of processor caches, it seemed most appropriate to use the maximum interleave amount so as to make the maximum memory bandwidth available for cache reload. For our purposes, a single page table bit indicating whether a page was located in sequential memory or was interleaved across the enti ...

Document

... A Random-Access Memory (RAM) is so called to contrast with its predecessor, the Serial-Access Memory. In a serial access memory, memory positions become available for reading on a sequential fashion. Therefore to read an specific memory position, the reader must wait a variable time delay for the me ...

... A Random-Access Memory (RAM) is so called to contrast with its predecessor, the Serial-Access Memory. In a serial access memory, memory positions become available for reading on a sequential fashion. Therefore to read an specific memory position, the reader must wait a variable time delay for the me ...

MainMemory

... in a similar fashion as the fast page mode and EDO DRAM. However the consecutive data is output synchronously on the falling/rising edge of the clock, instead of on command by CAS. How many data elements will be output (the length of the burst) is programmable up to the maximum size of the row. The ...

... in a similar fashion as the fast page mode and EDO DRAM. However the consecutive data is output synchronously on the falling/rising edge of the clock, instead of on command by CAS. How many data elements will be output (the length of the burst) is programmable up to the maximum size of the row. The ...

Analog System Builder, FlashROM, and Flash Memory System

... files, and log files. They all appear in your project folder under the directory. Do not modify

any of these generated files or store additional files in this folder. This folder will be recreated every time you

overwrite the core.

...

... files, and log files. They all appear in your project folder under the

asic 2001: formatting and submitting your paper

... carried out at a WL voltage of VDD. In some cases, WL voltage can be lowered during the cell. In this paper 8T FinFET SRAM cell design and read/write operation has been studies using Visual TCAD simulation .the layout of 8T FinFET SRAM developed using K-Layout software and corresponding mask is gene ...

... carried out at a WL voltage of VDD. In some cases, WL voltage can be lowered during the cell. In this paper 8T FinFET SRAM cell design and read/write operation has been studies using Visual TCAD simulation .the layout of 8T FinFET SRAM developed using K-Layout software and corresponding mask is gene ...

Document

... A Random-Access Memory (RAM) is so called to contrast with its predecessor, the Serial-Access Memory. In a serial access memory, memory positions become available for reading on a sequential fashion. Therefore to read an specific memory position, the reader must wait a variable time delay for the me ...

... A Random-Access Memory (RAM) is so called to contrast with its predecessor, the Serial-Access Memory. In a serial access memory, memory positions become available for reading on a sequential fashion. Therefore to read an specific memory position, the reader must wait a variable time delay for the me ...

Introduction - TAMU Computer Science Faculty Pages

... • Suppose 15% reduction in voltage results in a 15% reduction in frequency. What is impact on dynamic power? Powerdynamic 1 / 2 CapacitiveLoad Voltage FrequencySwitched ...

... • Suppose 15% reduction in voltage results in a 15% reduction in frequency. What is impact on dynamic power? Powerdynamic 1 / 2 CapacitiveLoad Voltage FrequencySwitched ...

DRAM - CMU (ECE) - Carnegie Mellon University

... Goal: Reduce the latency of memory array access and enable multiple accesses in parallel Idea: Divide the array into multiple banks that can be accessed independently (in the same cycle or in consecutive ...

... Goal: Reduce the latency of memory array access and enable multiple accesses in parallel Idea: Divide the array into multiple banks that can be accessed independently (in the same cycle or in consecutive ...

Lecture 19: SRAM

... In nanometer CMOS – Avoid bends in polysilicon and diffusion – Orient all transistors in one direction Lithographically friendly or thin cell layout fixes this – Also reduces length and capacitance of bitlines ...

... In nanometer CMOS – Avoid bends in polysilicon and diffusion – Orient all transistors in one direction Lithographically friendly or thin cell layout fixes this – Also reduces length and capacitance of bitlines ...

Semiconductor Memories - VLSI

... • Column Decoder: To select one out of 2M bits lines of the ROM array, and to route the data of the selected bit line to the data output • NOR-based column address decoder and pass transistors: » Only one nMOS pass transistor is turned on at a time » # of transistors required: 2M(M+1) (2M pass trans ...

... • Column Decoder: To select one out of 2M bits lines of the ROM array, and to route the data of the selected bit line to the data output • NOR-based column address decoder and pass transistors: » Only one nMOS pass transistor is turned on at a time » # of transistors required: 2M(M+1) (2M pass trans ...

Lecture 13: SRAM - Harvey Mudd College

... FIFO, LIFO Queues q First In First Out (FIFO) – Initialize read and write pointers to first element ...

... FIFO, LIFO Queues q First In First Out (FIFO) – Initialize read and write pointers to first element ...

Lecture 17 - Harvey Mudd College

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

ppt - CMOS VLSI Design

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

SRAMs

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

2 NAND overview: from memory to systems

... Memories: RAM loses its content when power supply is switched off, while ROM virtually holds it forever. A third category lies in between, i.e. NVM, acronym for Non-Volatile Memories, whose content can be electrically altered but it is also preserved when power supply is switched off. These are more ...

... Memories: RAM loses its content when power supply is switched off, while ROM virtually holds it forever. A third category lies in between, i.e. NVM, acronym for Non-Volatile Memories, whose content can be electrically altered but it is also preserved when power supply is switched off. These are more ...

Lecture 15

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

... Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8:1 column multiplexers ...

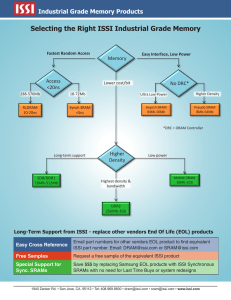

Industrial Grade Memory Products Brochure

... • Independent ECC with hamming code for each byte • Detect and correct one bit error per each byte • Better reliability than parity code schemes which can only detect an error but not correct an error ...

... • Independent ECC with hamming code for each byte • Detect and correct one bit error per each byte • Better reliability than parity code schemes which can only detect an error but not correct an error ...

Random-access memory

Random-access memory (RAM /ræm/) is a form of computer data storage. A random-access memory device allows data items to be accessed (read or written) in almost the same amount of time irrespective of the physical location of data inside the memory. In contrast, with other direct-access data storage media such as hard disks, CD-RWs, DVD-RWs and the older drum memory, the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement delays.Today, random-access memory takes the form of integrated circuits. RAM is normally associated with volatile types of memory (such as DRAM memory modules), where stored information is lost if power is removed, although many efforts have been made to develop non-volatile RAM chips. Other types of non-volatile memory exist that allow random access for read operations, but either do not allow write operations or have limitations on them. These include most types of ROM and a type of flash memory called NOR-Flash.Integrated-circuit RAM chips came into the market in the late 1960s, with the first commercially available DRAM chip, the Intel 1103, introduced in October 1970.