* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Real-World Avalanche Testing Of Single

Survey

Document related concepts

Transcript

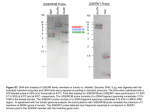

Real-World Avalanche Testing Of Single-Die, Wafers, Hybrid Modules, and Packaged Devices Steven T. Clauter Taichi Ukai Test Equipment Design Engineer President and CEO Integrated Technology Corporation Tiatech, Incorporated www.inttechcorp.com www.tiatech.com Avalanche Testing Background • MOSFET Avalanche Testing - 1985 • Manufactures Disagreed On Usefulness • Major Manufactures Now Provide Energy Ratings • What Is Avalanche Mode? • What Is Ruggedness? • Avalanche Test Methods • Industrial Avalanche Test Standards • MIL-STD-750 METHOD 3470.2 • JEDEC STANDARD JESD24-5 June 8 to 11, 2008 IEEE SW Test Workshop 2 Ideal Avalanche Test Circuit Decoupled VD UIS Method EAVA = ½L x I2D June 8 to 11, 2008 IEEE SW Test Workshop 3 Good Avalanche Test Waveform T1 and T2 Times Calculated From: Inductance Value I Peak Rated Drain Voltage Shows DUT Passing Avalanche Based On Measured T2 Time June 8 to 11, 2008 IEEE SW Test Workshop 4 Failed Avalanche Test Waveform Shows DUT Failing Avalanche Based On Measured T2 Time June 8 to 11, 2008 IEEE SW Test Workshop 5 Real-World Avalanche Circuit T2 = T1 = L RLoss ∗ IP LN 1 − RLoss VON ( VON L LN 1 − RLoss ∗ IP + VON RLoss ( ) ) RLoss > 0 L RLoss ∗ IP LN 1 − RLoss VON L VON T2 = LN 1− RLoss RLoss ∗ IP + VON ( T1 = ( June 8 to 11, 2008 ) ) VON = VLoss + VDUT ON VOFF = VLoss + VDUT OFF VDUT OFF = VAvalanche IEEE SW Test Workshop 6 Real-World With Losses Waveform Note the “Rounded Current” Waveshape Losses Increase T1 Time Losses Decrease T2 Time June 8 to 11, 2008 IEEE SW Test Workshop 7 Package Level Avalanche Testing DUT … now to extend this same testing to Wafer and Die June 8 to 11, 2008 IEEE SW Test Workshop 8 High Power Testing on Probe Cards Welded Needles High Power Test Events DUT Failures June 8 to 11, 2008 Damaged Probe Tips IEEE SW Test Workshop Aluminum Welds to Probe Tips 9 Wafer and Die High Power Avalanche Testing Realities: • Probe Cards • Probe Tips • Testing Environment Benefits: • Lower Cost Failures • Faster Process Analysis • Higher Net Yield • Comparison with Packaged Parts June 8 to 11, 2008 IEEE SW Test Workshop 10 Typical Die/Chip Carrier & Probe Card Chip Carrier Probe Card with 5 mil tip dia probes and Pogo Pins Enlarged Carrier View June 8 to 11, 2008 IEEE SW Test Workshop 11 200 Amp, 1000V Probe Card June 8 to 11, 2008 IEEE SW Test Workshop 12 Probe Tips on Aluminum Pad June 8 to 11, 2008 IEEE SW Test Workshop 13 Probe Tip Protection Technique I T = TEST CURRENT I source C ONTR OL I source CON TR O L I sour ce CON TRO L CO N TRO L It = 20 Amps I sour ce P1 P2 P3 P4 Imax = 5A/Probe, 5 mil dia IP1 = 5A, VP1 = 0.5V PP1 = 2.5W 0.1 0.5 1.0 1.5 ALUMINUM PAD POWER MOSFET DIE RETURN Manage Probe Current & Voltage to keep POWER Dissipation from harming Probes IP4 = 5A, VP4 = 7.5V PP4 = 37.5W!!!! TOO HIGH June 8 to 11, 2008 IEEE SW Test Workshop 14 Probe Simulation Circuit L1 50µH IRL530NS_L IRL530NS_L IRL530NS_L IRL530NS_ 3.0 V2 3.0 R1 0.1 V3 3.0 R2 0.5 V4 Probe4 M4 Probe3 M3 Probe2 V1 M2 Probe1 V5 PULSE(0 50) M1 3.0 R3 1.0 R4 1.5 .tran 0.000022 June 8 to 11, 2008 IEEE SW Test Workshop 15 Probe Tip Currents 5 .A 5 A .0 4 A .5 4 A .0 I(R 1 ) I(R 2 ) I(R 3 ) I(R 4 ) 3 A .5 3 A .0 2 A .5 2 A .0 1 A .5 1 A .0 0 A .5 0 .A -0 A .5 0 µ s June 8 to 11, 2008 2 µ s 4 µ s 6 µ s 8 µ s 1 0 µ s 1 2 µ s IEEE SW Test Workshop 1 4 µ s 1 6 µ s 1 8 µ s 2 0 µ s 2 µ s 16 Probe Tip POWER 4 W 4 W 0 V (p ro b e 4 )*IR 3 W 6 3 W 2 2 W 8 2 W 4 V (p ro b e 3 )*IR 2 W 0 1 W 6 V (p ro b e 2 )*IR 1 W 2 W 8 V (p ro b e 1 )*IR W 4 W 0 1 0 µ s June 8 to 11, 2008 1 µ s 1 2 µ s 1 3 µ s 1 4 µ s 1 5 µ s 1 6 µ s 1 7 µ s IEEE SW Test Workshop 1 8 µ s 1 9 µ s 2 0 µ s 2 1 µ s 2 µ s 17 Power Limiter Showing Probe Tip Protection Concept June 8 to 11, 2008 IEEE SW Test Workshop 18 Production Avalanche WPS June 8 to 11, 2008 IEEE SW Test Workshop 19 Simple Avalanche Connection Diagram June 8 to 11, 2008 IEEE SW Test Workshop 20 Realized Avalanche Waveforms June 8 to 11, 2008 IEEE SW Test Workshop 21 Avalanche Waveform – PASS Collector Current Collector Voltage Gate Voltage Sense Emitter June 8 to 11, 2008 IEEE SW Test Workshop 22 Avalanche Waveform – FAILURE Collector Current Collector Voltage Gate Voltage Sense Emitter June 8 to 11, 2008 IEEE SW Test Workshop 23 Advanced Chip or Die Level Avalanche Testing Connections June 8 to 11, 2008 IEEE SW Test Workshop 24 WPS Current Limiter Overview • Patent-Pending Power Limiter Circuit • Set for 5 Amps per Probe and uses Standard Probe Card Technology • Limits Maximum Current In The BEST Probe • Limits Maximum Power in the WORST Probe • Voltage Across Contact Resistance Monitored for Complete Protection June 8 to 11, 2008 IEEE SW Test Workshop 25 Summary • Allows for Standard Avalanche Test Methods to be used FULL Power • Expandable to High Power and High Current Parts and Tests • Power MOSFETs, IGBTs, Diodes, Transzorbs • Avalanche, RBSOA, VDSON, RDSON, VCEON, VF-SD(body diode) • All performed with the SAME equipment at the SAME Probe Station • Allows Correlation with Packaged Parts June 8 to 11, 2008 IEEE SW Test Workshop 26 References Tim McDonald, Marco Soldano, Anthony Murry, Teodor Avram “Power MOSFET Avalanche Design Guidelines” IR Application Note AN-1006 Kenneth Dierberger “Understanding The Difference Between Standard MOSFETs and Avalanche Energy Rated MOSFETs” Advanced Power Technology Application Note “Power MOSFET Single-Shot And Repetitive Avalanche Ruggedness Rating” Philips Semiconductor Application Note AN10273-1 Warren Schultz “Power Transistor Safe Operating Area” ON Semiconductor Application Note AN875/D Michael Bairanzade “Understanding Power Transistors Breakdown Parameters” ON Semiconductor Application Note AN1628/D June 8 to 11, 2008 IEEE SW Test Workshop 27