* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

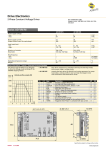

Download XMC4000 - Fail-Safe Features

Buck converter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

Opto-isolator wikipedia , lookup

Phase-locked loop wikipedia , lookup

Time-to-digital converter wikipedia , lookup