Digital Temperature Controller

... *6 Refer to the E5@C Digital Controllers User's Manual (Cat. No. H174) for information on the operation of the standby sequence. *7 Refer to the E5@C Digital Controllers User's Manual (Cat. No.H174) for information on the loop burnout alarm (LBA). *8 Refer to the E5@C Digital Controllers User's Manu ...

... *6 Refer to the E5@C Digital Controllers User's Manual (Cat. No. H174) for information on the operation of the standby sequence. *7 Refer to the E5@C Digital Controllers User's Manual (Cat. No.H174) for information on the loop burnout alarm (LBA). *8 Refer to the E5@C Digital Controllers User's Manu ...

Two Output, Integrated VCO, Low-Jitter Clock Generator.. (Rev. F)

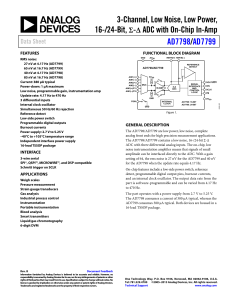

... ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. ...

... ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. ...

Dual 0.275% Comparators and Reference with Programmable Hysteresis ADCMP341/ADCMP343

... 5.5 V, the devices only draw 6.5 μA (typical), making them ideal for low voltage system monitoring and portable applications. Hysteresis is determined using three resistors in a string configuration with the upper and lower tap points connected to the ±INA_U and ±INA_L pins of each comparator, respe ...

... 5.5 V, the devices only draw 6.5 μA (typical), making them ideal for low voltage system monitoring and portable applications. Hysteresis is determined using three resistors in a string configuration with the upper and lower tap points connected to the ±INA_U and ±INA_L pins of each comparator, respe ...

ADCMP341 数据手册DataSheet 下载

... Each of the comparators has one input available externally; the other comparator inputs are connected internally to the 400 mV reference. The ADCMP341 has two noninverting comparators and the ADCMP343 has two inverting comparators. There are two input pins available to each comparator. However, thes ...

... Each of the comparators has one input available externally; the other comparator inputs are connected internally to the 400 mV reference. The ADCMP341 has two noninverting comparators and the ADCMP343 has two inverting comparators. There are two input pins available to each comparator. However, thes ...

PCA9701; PCA9702 1. General description 18 V tolerant SPI 16-bit/8-bit GPI with INT

... HIGH when it is greater than 0.7 VDD and as a LOW when it is less than 0.4 VDD (minimum threshold of 2 V at 5 V node). The PCA9701 can monitor up to 16 switch inputs and the PCA9702 can monitor up to 8 switch inputs. The falling edge of the CS pin samples the input port status and clears the int ...

... HIGH when it is greater than 0.7 VDD and as a LOW when it is less than 0.4 VDD (minimum threshold of 2 V at 5 V node). The PCA9701 can monitor up to 16 switch inputs and the PCA9702 can monitor up to 8 switch inputs. The falling edge of the CS pin samples the input port status and clears the int ...

HIN202, HIN206, HIN207, HIN208, HIN211, HIN213

... voltage doubler and the voltage inverter. Each section is driven by a two phase, internally generated clock to generate +10V and -10V. The nominal clock frequency is 125kHz. During phase one of the clock, capacitor C1 is charged to VCC . During phase two, the voltage on C1 is added to VCC , producin ...

... voltage doubler and the voltage inverter. Each section is driven by a two phase, internally generated clock to generate +10V and -10V. The nominal clock frequency is 125kHz. During phase one of the clock, capacitor C1 is charged to VCC . During phase two, the voltage on C1 is added to VCC , producin ...

Feedback (Negative and Positive) File

... drops below that lower reference level. The result is a clean square-wave output again, despite significant amounts of distortion in the AC input signal. In order for a "glitch" to cause the comparator to switch from one state to another, it would have to be at least as big (tall) as the difference ...

... drops below that lower reference level. The result is a clean square-wave output again, despite significant amounts of distortion in the AC input signal. In order for a "glitch" to cause the comparator to switch from one state to another, it would have to be at least as big (tall) as the difference ...

Transistor Odds and Ends

... current inputs, sequential logic can also depend on the previous “state” of the system. • Circuitry designed to hold a high or low state is known as a flip-flop. • A flip-flop is the smallest unit of RAM – random access memory. • Recall there are two basic categories of RAM: dynamic RAM (DRAM) and s ...

... current inputs, sequential logic can also depend on the previous “state” of the system. • Circuitry designed to hold a high or low state is known as a flip-flop. • A flip-flop is the smallest unit of RAM – random access memory. • Recall there are two basic categories of RAM: dynamic RAM (DRAM) and s ...

EE 382M VLSI–II: Advanced Circuit Design Lecture 12: I/O & ESD

... Differential signaling uses two complementary signals sent on two separate wires. – Able to reject common-mode noise – More expensive to implement from both a wire perspective as well as the ...

... Differential signaling uses two complementary signals sent on two separate wires. – Able to reject common-mode noise – More expensive to implement from both a wire perspective as well as the ...

SN65HVD178x Fault-Protected RS-485

... devices are characterized from –40°C to 125°C. These devices are pin-compatible with the industrystandard SN75176 transceiver, making them drop-in upgrades in most systems. These devices are fully compliant with ANSI TIA/EIA 485-A with a 5-V supply and can operate with a 3.3-V supply with reduced dr ...

... devices are characterized from –40°C to 125°C. These devices are pin-compatible with the industrystandard SN75176 transceiver, making them drop-in upgrades in most systems. These devices are fully compliant with ANSI TIA/EIA 485-A with a 5-V supply and can operate with a 3.3-V supply with reduced dr ...

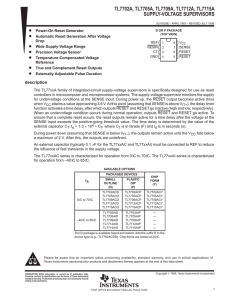

Supply Voltage Supervisors

... for undervoltage conditions at the SENSE input. During power up, the RESET output becomes active (low) when VCC attains a value approaching 3.6 V. At this point (assuming that SENSE is above VIT+), the delay timer function activates a time delay, after which outputs RESET and RESET go inactive (high ...

... for undervoltage conditions at the SENSE input. During power up, the RESET output becomes active (low) when VCC attains a value approaching 3.6 V. At this point (assuming that SENSE is above VIT+), the delay timer function activates a time delay, after which outputs RESET and RESET go inactive (high ...

Digital Tachometer

... When input rpm is either 99999 or more, or 0, settings cannot be performed since these numbers exceed the field adjustment's setting range. In such a case, "EE-2"* is displayed in the main display. When input rpm is 99999 or more, lower and set it again. When input rpm is 0, raise it until the input ...

... When input rpm is either 99999 or more, or 0, settings cannot be performed since these numbers exceed the field adjustment's setting range. In such a case, "EE-2"* is displayed in the main display. When input rpm is 99999 or more, lower and set it again. When input rpm is 0, raise it until the input ...

TPS54120EVM, Low Noise 1A Power Supply Evaluation Module

... The input decoupling capacitor of the SW (C5) is located as close as possible to the IC. PVIN and VIN are connected together in this EVM, and then through vias they are connected to the input voltage trace in the second internal layer. Whereas, the decoupling capacitor ground is connected through vi ...

... The input decoupling capacitor of the SW (C5) is located as close as possible to the IC. PVIN and VIN are connected together in this EVM, and then through vias they are connected to the input voltage trace in the second internal layer. Whereas, the decoupling capacitor ground is connected through vi ...

MAX13481E/MAX13482E/MAX13483E ±15kV ESD-Protected USB Transceivers with External/Internal Pullup Resistors General Description

... Connect VL and VBUS to system power supplies (Table 1). Connect VL to a +1.6V to +3.6V supply. Connect VBUS to a +4.0V to +5.5V supply or to the VBUS connector. Alternatively, these parts can derive power from a single Li+ cell. Connect the battery to VBUS. VTRM remains above +3.0V for VBUS as low a ...

... Connect VL and VBUS to system power supplies (Table 1). Connect VL to a +1.6V to +3.6V supply. Connect VBUS to a +4.0V to +5.5V supply or to the VBUS connector. Alternatively, these parts can derive power from a single Li+ cell. Connect the battery to VBUS. VTRM remains above +3.0V for VBUS as low a ...

LT1993-2

... Amplifier/ADC driver for use in applications from DC to 800MHz. The LT1993-2 has been designed for ease of use, with minimal support circuitry required. Exceptionally low input-referred noise and low distortion products (with either single-ended or differential inputs) make the LT1993-2 an excellent ...

... Amplifier/ADC driver for use in applications from DC to 800MHz. The LT1993-2 has been designed for ease of use, with minimal support circuitry required. Exceptionally low input-referred noise and low distortion products (with either single-ended or differential inputs) make the LT1993-2 an excellent ...

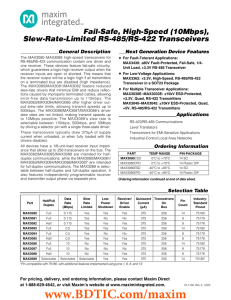

Fail-Safe, High-Speed (10Mbps), Slew-Rate-Limited RS-485/RS-422 Transceivers General Description Next Generation Device Features

... The MAX3080–MAX3089 high-speed transceivers for RS-485/RS-422 communication contain one driver and one receiver. These devices feature fail-safe circuitry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted. This means that the receiver output will be a logic ...

... The MAX3080–MAX3089 high-speed transceivers for RS-485/RS-422 communication contain one driver and one receiver. These devices feature fail-safe circuitry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted. This means that the receiver output will be a logic ...

ADA4938-1 数据手册DataSheet 下载

... The ADA4938 is a low noise, ultralow distortion, high speed differential amplifier. It is an ideal choice for driving high performance ADCs with resolutions up to 16 bits from dc to 27 MHz, or up to 12 bits from dc to 74 MHz. The output commonmode voltage is adjustable over a wide range, allowing th ...

... The ADA4938 is a low noise, ultralow distortion, high speed differential amplifier. It is an ideal choice for driving high performance ADCs with resolutions up to 16 bits from dc to 27 MHz, or up to 12 bits from dc to 74 MHz. The output commonmode voltage is adjustable over a wide range, allowing th ...

The DatasheetArchive - Datasheet Search Engine

... Annex B. They represent the worst case jitter contribution that the transceivers are allowed to make to the overall system jitter without violating the Annex B allocation example. In practice, the typical contribution of the HP transceivers is well below these maximum allowed amounts. Recommended Ha ...

... Annex B. They represent the worst case jitter contribution that the transceivers are allowed to make to the overall system jitter without violating the Annex B allocation example. In practice, the typical contribution of the HP transceivers is well below these maximum allowed amounts. Recommended Ha ...

Circuit Pitfalls

... E-field across channel impart high energies to some carriers – These “hot” carriers may be blasted into the gate oxide where they become trapped – Charge accumulation causes shift in Vt over time – Eventually Vt shifts too far for correct operation Choose VDD to achieve reasonable product lifeti ...

... E-field across channel impart high energies to some carriers – These “hot” carriers may be blasted into the gate oxide where they become trapped – Charge accumulation causes shift in Vt over time – Eventually Vt shifts too far for correct operation Choose VDD to achieve reasonable product lifeti ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.