SP3245E 数据资料DataSheet下载

... pin. The non-inverted output of Receiver 2 (R2OUT) will continue to be active in all modes, including shutdown. ...

... pin. The non-inverted output of Receiver 2 (R2OUT) will continue to be active in all modes, including shutdown. ...

a Dual Fractional-N/Integer-N Frequency Synthesizer ADF4252

... wireless receivers and transmitters. Both the RF and IF synthesizers consist of a low noise digital PFD (phase frequency detector), a precision charge pump, and a programmable reference divider. The RF synthesizer has a ⌺-⌬-based fractional interpolator that allows programmable fractional-N division ...

... wireless receivers and transmitters. Both the RF and IF synthesizers consist of a low noise digital PFD (phase frequency detector), a precision charge pump, and a programmable reference divider. The RF synthesizer has a ⌺-⌬-based fractional interpolator that allows programmable fractional-N division ...

Operational Amplifiers

... z What is the common-mode level at nodes X and Y? Since each of the input transistors carries a current ISS /2, the CM level depends on how close ID3 and ID4 are to this value. z Effect of current mismatches: Mismatches in the PMOS and NMOS current mirrors defining ISS and ID3,4 create a finite erro ...

... z What is the common-mode level at nodes X and Y? Since each of the input transistors carries a current ISS /2, the CM level depends on how close ID3 and ID4 are to this value. z Effect of current mismatches: Mismatches in the PMOS and NMOS current mirrors defining ISS and ID3,4 create a finite erro ...

MAX1117/MAX1118/MAX1119 Single-Supply, Low-Power, 2-Channel, Serial 8-Bit ADCs General Description

... interface. The CNVST and SCLK inputs are used to control the device, while the three-state DOUT pin is used to access the conversion results. The serial interface provides connection to microcontrollers (µCs) with SPI, QSPI, and MICROWIRE serial interfaces at clock rates up to 5MHz. The interface su ...

... interface. The CNVST and SCLK inputs are used to control the device, while the three-state DOUT pin is used to access the conversion results. The serial interface provides connection to microcontrollers (µCs) with SPI, QSPI, and MICROWIRE serial interfaces at clock rates up to 5MHz. The interface su ...

MAX976/MAX978/MAX998 Single/Dual/Quad, SOT23, Single-Supply, High-Speed, Low-Power Comparators ________________General Description

... Note 1: The MAX998EUT specifications are 100% tested at TA = +25°C. Limits over the extended temperature range are guaranteed by design, not production tested. Note 2: Inferred from CMRR test. Either input can be driven to the absolute maximum limit without false output inversion, as long as the oth ...

... Note 1: The MAX998EUT specifications are 100% tested at TA = +25°C. Limits over the extended temperature range are guaranteed by design, not production tested. Note 2: Inferred from CMRR test. Either input can be driven to the absolute maximum limit without false output inversion, as long as the oth ...

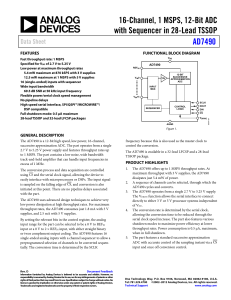

AD7490 16-Channel, 1 MSPS, 12-Bit ADC with Sequencer in 28

... to 1 MSPS. The part contains a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 1 MHz. ...

... to 1 MSPS. The part contains a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 1 MHz. ...

AAT3193-1 数据资料DataSheet下载

... LED enable and serial control input. EN/SET is the ON/OFF control for the LED and the S2Cwire digital input for the AAT3193-1/-2/-3 to control serially the LED brightness according to the maximum current set by RSET. LED ON/OFF and PWM control input. This logic input controls the LED outputs for the ...

... LED enable and serial control input. EN/SET is the ON/OFF control for the LED and the S2Cwire digital input for the AAT3193-1/-2/-3 to control serially the LED brightness according to the maximum current set by RSET. LED ON/OFF and PWM control input. This logic input controls the LED outputs for the ...

PCA9546A 数据资料 dataSheet 下载

... Power-On Reset When power is applied to VCC, an internal power-on reset holds the PCA9546A in a reset condition until VCC has reached VPOR. At this point, the reset condition is released, and the PCA9546A registers and I2C state machine are initialized to their default states, all zeroes, causing al ...

... Power-On Reset When power is applied to VCC, an internal power-on reset holds the PCA9546A in a reset condition until VCC has reached VPOR. At this point, the reset condition is released, and the PCA9546A registers and I2C state machine are initialized to their default states, all zeroes, causing al ...

BU4015B

... 12. Regarding the Input Pin of the IC In the construction of this IC, P-N junctions are inevitably formed creating parasitic diodes or transistors. The operation of these parasitic elements can result in mutual interference among circuits, operational faults, or physical damage. Therefore, condition ...

... 12. Regarding the Input Pin of the IC In the construction of this IC, P-N junctions are inevitably formed creating parasitic diodes or transistors. The operation of these parasitic elements can result in mutual interference among circuits, operational faults, or physical damage. Therefore, condition ...

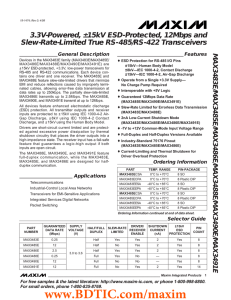

3.3V-Powered, ±15kV ESD-Protected, 12Mbps and Slew-Rate-Limited True RS-485/RS-422 Transceivers MAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E General Description

... Receiver Output Enable. RO is enabled when RE is low; RO is high impedance when RE is high. If RE is high and DE is low, the device will enter a low-power shutdown mode. ...

... Receiver Output Enable. RO is enabled when RE is low; RO is high impedance when RE is high. If RE is high and DE is low, the device will enter a low-power shutdown mode. ...

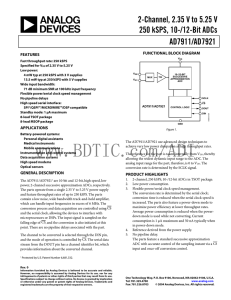

AD7911 数据手册DataSheet下载

... input is also used as the clock source for the AD7911/AD7921’s conversion process. Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7911/AD7921 and framing the serial data transfer. Data Out. Logic output. The conversion result from the AD ...

... input is also used as the clock source for the AD7911/AD7921’s conversion process. Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7911/AD7921 and framing the serial data transfer. Data Out. Logic output. The conversion result from the AD ...

DS1340 I C RTC with Trickle Charger 2

... Frequency Test/Output. This pin is used to output either a 512Hz signal or the value of the OUT bit. When the FT bit is logic 1, the FT/OUT pin toggles at a 512Hz rate. When the FT bit is logic 0, the FT/OUT pin reflects the value of the OUT bit. This open-drain pin requires an external pullup resis ...

... Frequency Test/Output. This pin is used to output either a 512Hz signal or the value of the OUT bit. When the FT bit is logic 1, the FT/OUT pin toggles at a 512Hz rate. When the FT bit is logic 0, the FT/OUT pin reflects the value of the OUT bit. This open-drain pin requires an external pullup resis ...

A 52 Amplifier2.qxp

... Power amplifiers are usually heavier and generate more heat than other components. To avoid damage to the A 52 or other equipment and to reduce risk of fire, you must follow these guidelines: ...

... Power amplifiers are usually heavier and generate more heat than other components. To avoid damage to the A 52 or other equipment and to reduce risk of fire, you must follow these guidelines: ...

Analog Dialogue Volume 43, Number 2, 2009

... size, and cost. Calculating total error is difficult, with multiple components adding varying degrees of error with coefficients that can be of differing polarities. The design does not provide short-circuit detection/protection or any level of fault diagnostics. It does not include a voltage output ...

... size, and cost. Calculating total error is difficult, with multiple components adding varying degrees of error with coefficients that can be of differing polarities. The design does not provide short-circuit detection/protection or any level of fault diagnostics. It does not include a voltage output ...

FSAM75SM60A Motion SPM 2 Series ®

... 1. RPLCPL/RPHCPH /RPFCPF coupling at each Motion SPM® 2 product input is recommended in order to prevent input signals’ oscillation and it should be as close as possible to each Motion SPM 2 product input pin. 2. By virtue of integrating an application specific type HVIC inside the Motion SPM 2 prod ...

... 1. RPLCPL/RPHCPH /RPFCPF coupling at each Motion SPM® 2 product input is recommended in order to prevent input signals’ oscillation and it should be as close as possible to each Motion SPM 2 product input pin. 2. By virtue of integrating an application specific type HVIC inside the Motion SPM 2 prod ...

"Supply-Voltage Supervisors"

... for undervoltage conditions at the SENSE input. During power up, the RESET output becomes active (low) when VCC attains a value approaching 3.6 V. At this point (assuming that SENSE is above VIT+), the delay timer function activates a time delay, after which outputs RESET and RESET go inactive (high ...

... for undervoltage conditions at the SENSE input. During power up, the RESET output becomes active (low) when VCC attains a value approaching 3.6 V. At this point (assuming that SENSE is above VIT+), the delay timer function activates a time delay, after which outputs RESET and RESET go inactive (high ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.