1 Static Characteristics I

... Fig. 1.3 shows a set of output characteristics for the transistor as IC vs VCE for a range of values of IB. A load line can be superimposed on these curves which defines the operating path followed by the output of the transistor for the particular load resistor, RC and supply voltage VCC. This path ...

... Fig. 1.3 shows a set of output characteristics for the transistor as IC vs VCE for a range of values of IB. A load line can be superimposed on these curves which defines the operating path followed by the output of the transistor for the particular load resistor, RC and supply voltage VCC. This path ...

NBSG11 2.5V/3.3V SiGe 1:2 Differential Clock Driver with RSECL* Outputs

... NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functiona ...

... NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functiona ...

1 10 16 A4

... disappear from the display as new data is acquired. It is not always possible to manually Start and Stop data acquisition to catch the abnormal waveform and have it displayed. The History Memory function was designed for such situations. It divides long memory into a number of blocks and automatical ...

... disappear from the display as new data is acquired. It is not always possible to manually Start and Stop data acquisition to catch the abnormal waveform and have it displayed. The History Memory function was designed for such situations. It divides long memory into a number of blocks and automatical ...

NTS0103 1. General description Dual supply translating transceiver; open drain; auto

... (An and Bn), one output enable input (OE) and two supply pins (VCC(A) and VCC(B)). VCC(A) can be supplied at any voltage between 1.65 V and 3.6 V and VCC(B) can be supplied at any voltage between 2.3 V and 5.5 V, making the device suitable for translating between any of the voltage nodes (1.8 V, 2.5 ...

... (An and Bn), one output enable input (OE) and two supply pins (VCC(A) and VCC(B)). VCC(A) can be supplied at any voltage between 1.65 V and 3.6 V and VCC(B) can be supplied at any voltage between 2.3 V and 5.5 V, making the device suitable for translating between any of the voltage nodes (1.8 V, 2.5 ...

ScopeCorder YOKOGAWA DL750

... disappear from the display as new data is acquired. It is not always possible to manually Start and Stop data acquisition to catch the abnormal waveform and have it displayed. The History Memory function was designed for such situations. It divides long memory into a number of blocks and automatical ...

... disappear from the display as new data is acquired. It is not always possible to manually Start and Stop data acquisition to catch the abnormal waveform and have it displayed. The History Memory function was designed for such situations. It divides long memory into a number of blocks and automatical ...

The Comparison of the Input Impedance

... (LISN) are paralleled (25 ). The common mode input impedance of SMPS are derived by equation (2). Similarly, the case of the differential mode input impedance of SMPS adds the parallel “Z shunt ” to SMPS. The Z shunt is the series combination of a 1 ...

... (LISN) are paralleled (25 ). The common mode input impedance of SMPS are derived by equation (2). Similarly, the case of the differential mode input impedance of SMPS adds the parallel “Z shunt ” to SMPS. The Z shunt is the series combination of a 1 ...

TPS77301 数据资料 dataSheet 下载

... Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 200 mV at an output current of 250 mA for 3.3-volt option) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent curre ...

... Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 200 mV at an output current of 250 mA for 3.3-volt option) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent curre ...

12 LVPECL Output, High-Performance Clock Buffer (Rev. B)

... The CDCLVP2106 clock buffer distributes two clock inputs (IN0, IN1) to 12 pairs of differential LVPECL clock outputs (OUT0, OUT11) with minimum skew for clock distribution. Each buffer block consists of one input that feeds two LVPECL clock outputs. The inputs can be LVPECL, LVDS, or LVCMOS/LVTTL. T ...

... The CDCLVP2106 clock buffer distributes two clock inputs (IN0, IN1) to 12 pairs of differential LVPECL clock outputs (OUT0, OUT11) with minimum skew for clock distribution. Each buffer block consists of one input that feeds two LVPECL clock outputs. The inputs can be LVPECL, LVDS, or LVCMOS/LVTTL. T ...

LM139/LM239/LM339/LM2901/LM3302 Low Power Low Offset

... The LM139 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change ...

... The LM139 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change ...

Octal Ultrasound AFE with JESD204B AD9675 Data Sheet FEATURES

... bandwidth reduction. Each channel features a maximum gain of up to 52 dB, a fully differential signal path, and an active input preamplifier termination. The channel is optimized for high dynamic performance and low power in applications where a small package size is critical. The LNA has a single-e ...

... bandwidth reduction. Each channel features a maximum gain of up to 52 dB, a fully differential signal path, and an active input preamplifier termination. The channel is optimized for high dynamic performance and low power in applications where a small package size is critical. The LNA has a single-e ...

LM139/LM239/LM339/LM2901/LM3302 Low Power Low Offset

... The LM139 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change ...

... The LM139 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change ...

ACS1790T - Semtech

... The ACS1790T is a high-performance, low phase noise, programmable frequency synthesizer with ultra-fine dynamic output frequency control. It can be used as a companion to a compatible ToPSync™ device to generate outputs locked to an external reference source or standalone for standard frequency gene ...

... The ACS1790T is a high-performance, low phase noise, programmable frequency synthesizer with ultra-fine dynamic output frequency control. It can be used as a companion to a compatible ToPSync™ device to generate outputs locked to an external reference source or standalone for standard frequency gene ...

MAX7365 1MHz I2C-Interfaced 8 x 7 Key-Switch Controller with GPIO Ports General Description

... of the selected number of debounce cycles following a key event (Table 9). This number ranges from 1–31 debounce cycles. Setting bits D[7:5] sets the FIFObased interrupt when there are 2–14 key events stored in the FIFO. Both interrupts can be configured simultaneously, and INT asserts depending on ...

... of the selected number of debounce cycles following a key event (Table 9). This number ranges from 1–31 debounce cycles. Setting bits D[7:5] sets the FIFObased interrupt when there are 2–14 key events stored in the FIFO. Both interrupts can be configured simultaneously, and INT asserts depending on ...

AN28 - Thermocouple Measurement

... To avoid gain error, high open-loop gain is necessary for single-stage thermocouple amplifiers with 10mV/°C or higher outputs. A type K amplifier, for instance, with 100mV/°C output, needs a closed-loop gain of 2,500. An ordinary op amp with a minimum loop of 50,000 would have an initial gain error of ...

... To avoid gain error, high open-loop gain is necessary for single-stage thermocouple amplifiers with 10mV/°C or higher outputs. A type K amplifier, for instance, with 100mV/°C output, needs a closed-loop gain of 2,500. An ordinary op amp with a minimum loop of 50,000 would have an initial gain error of ...

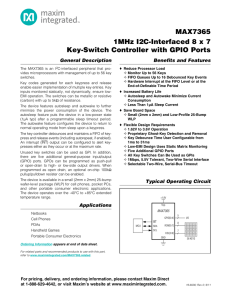

a Low Noise, 90 MHz Variable-Gain Amplifier AD603*

... input noise of 1.3 nV/√Hz. It will be apparent that it is essential to use a low resistance in the ladder network to achieve the very low specified noise level. The signal’s source impedance forms a voltage divider with the AD603’s 100 Ω input resistance. In some applications, the resulting attenuat ...

... input noise of 1.3 nV/√Hz. It will be apparent that it is essential to use a low resistance in the ladder network to achieve the very low specified noise level. The signal’s source impedance forms a voltage divider with the AD603’s 100 Ω input resistance. In some applications, the resulting attenuat ...

VERY LOW POWER, NEGATIVE RAIL INPUT, RAIL-TO-RAIL OUTPUT, FULLY DIFFERENTIAL AMPLIFIER THS4521 THS4522

... range that includes the negative rail. These amplifiers are designed for low-power data acquisition systems and high-density applications where power dissipation is a critical parameter, and provide exceptional performance in audio applications. The family includes single (THS4521), (THS4522), and q ...

... range that includes the negative rail. These amplifiers are designed for low-power data acquisition systems and high-density applications where power dissipation is a critical parameter, and provide exceptional performance in audio applications. The family includes single (THS4521), (THS4522), and q ...

QS10.121 - PULS Power Supply

... built-in large sized output capacitors, these features help start motors, charge capacitors and absorb reverse energy and often allow a unit of a lower wattage class to be used. High immunity to transients and power surges as well as low electromagnetic emission makes usage in nearly every environme ...

... built-in large sized output capacitors, these features help start motors, charge capacitors and absorb reverse energy and often allow a unit of a lower wattage class to be used. High immunity to transients and power surges as well as low electromagnetic emission makes usage in nearly every environme ...

MT-060 TUTORIAL Choosing Between Voltage Feedback (VFB)

... The output offset voltage due to the input bias currents can be nulled by making the effective source resistance equal in both the inverting and non-inverting inputs. This scheme will not work with bias-current compensated VFB op amps which have additional current generators on their inputs. In this ...

... The output offset voltage due to the input bias currents can be nulled by making the effective source resistance equal in both the inverting and non-inverting inputs. This scheme will not work with bias-current compensated VFB op amps which have additional current generators on their inputs. In this ...

LTM8029 - 36VIN, 600mA Step-Down μModule Converter with 5μA Quiescent Current

... that is off when the output is in regulation, allowing an external resistor to pull the PGOOD pin high. Power good is valid when the LTM8029 is enabled and VIN is above 4.5V. The LTM8029 features the ability to skip the off-time in switching cycles when the input voltage approaches the target output ...

... that is off when the output is in regulation, allowing an external resistor to pull the PGOOD pin high. Power good is valid when the LTM8029 is enabled and VIN is above 4.5V. The LTM8029 features the ability to skip the off-time in switching cycles when the input voltage approaches the target output ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.