AD5306 数据手册DataSheet 下载

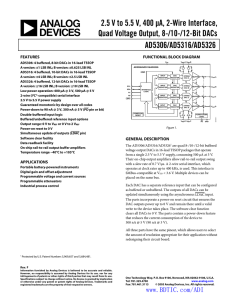

... Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation. Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation. Reference Input Pin for ...

... Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation. Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation. Reference Input Pin for ...

ADC音频放大器系列SSM2302 数据手册DataSheet 下载

... The SSM2302 is a fully integrated, high efficiency, Class-D stereo audio amplifier. It is designed to maximize performance for mobile phone applications. The application circuit requires a minimum of external components and operates from a single 2.5 V to 5.0 V supply. It is capable of delivering 1. ...

... The SSM2302 is a fully integrated, high efficiency, Class-D stereo audio amplifier. It is designed to maximize performance for mobile phone applications. The application circuit requires a minimum of external components and operates from a single 2.5 V to 5.0 V supply. It is capable of delivering 1. ...

LTC2400 - 24-Bit µPower No Latency Delta-Sigma ADC in SO-8

... SDO (Pin 6): Three-State Digital Output. During the data output period, this pin is used for serial data output. When the chip select CS is HIGH (CS = VCC), the SDO pin is in a high impedance state. During the Conversion and Sleep periods this pin can be used as a conversion status output. The conve ...

... SDO (Pin 6): Three-State Digital Output. During the data output period, this pin is used for serial data output. When the chip select CS is HIGH (CS = VCC), the SDO pin is in a high impedance state. During the Conversion and Sleep periods this pin can be used as a conversion status output. The conve ...

Analog FAQ - Penn State School of Electrical Engineering and

... Systems with separate input and output offsets will be considered later. From (3) we see that it not possible to trim gain directly when an unknown offset is present. Offset must be trimmed first. With IP set at 0, the offset trim is adjusted until OP is also 0. Gain may then be trimmed: with an inp ...

... Systems with separate input and output offsets will be considered later. From (3) we see that it not possible to trim gain directly when an unknown offset is present. Offset must be trimmed first. With IP set at 0, the offset trim is adjusted until OP is also 0. Gain may then be trimmed: with an inp ...

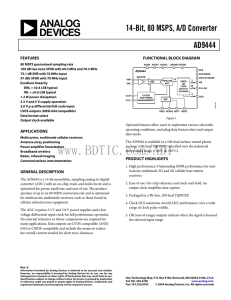

14-Bit, 80 MSPS, A/D Converter AD9444 FEATURES

... Pulse width high is the minimum amount of time that the clock pulse should be left in the Logic 1 state to achieve rated performance. Pulse width low is the minimum time the clock pulse should be left in the low state. At a given clock rate, these specifications define an acceptable clock duty cycle ...

... Pulse width high is the minimum amount of time that the clock pulse should be left in the Logic 1 state to achieve rated performance. Pulse width low is the minimum time the clock pulse should be left in the low state. At a given clock rate, these specifications define an acceptable clock duty cycle ...

MAX9386/MAX9387/MAX9388 Differential 5:1 or 4:1 ECL/PECL Multiplexers with Single/Dual Output Buffers General Description

... Measurements are made with the device in thermal equilibrium. Current into an I/O pin is defined as positive. Current out of an I/O pin is defined as negative. DC parameters production tested at TA = +25°C and guaranteed by design over the full operating temperature range. Single-ended data input op ...

... Measurements are made with the device in thermal equilibrium. Current into an I/O pin is defined as positive. Current out of an I/O pin is defined as negative. DC parameters production tested at TA = +25°C and guaranteed by design over the full operating temperature range. Single-ended data input op ...

MAX5722 12-Bit, Low-Power, Dual, Voltage-Output DAC with Serial Interface General Description

... The MAX5722 contains two 12-bit, voltage-output, lowpower, digital-to-analog converters (DACs). Each DAC employs a resistor string architecture that converts a 12-bit digital input word to an equivalent analog output voltage proportional to the applied reference voltage. The MAX5722 shares one refer ...

... The MAX5722 contains two 12-bit, voltage-output, lowpower, digital-to-analog converters (DACs). Each DAC employs a resistor string architecture that converts a 12-bit digital input word to an equivalent analog output voltage proportional to the applied reference voltage. The MAX5722 shares one refer ...

MAX6381XR25D1+T中文资料

... Note:Insert reset threshold suffix (see Reset Threshold table)after "XR", "XS", or "LT." Insert reset timeout delay (see ResetTimeout Delay table) after "D" to complete the part number.Sample stock is generally held on standard versions only (seeStandard Versions table). Standard versions have an or ...

... Note:Insert reset threshold suffix (see Reset Threshold table)after "XR", "XS", or "LT." Insert reset timeout delay (see ResetTimeout Delay table) after "D" to complete the part number.Sample stock is generally held on standard versions only (seeStandard Versions table). Standard versions have an or ...

CPLD I/O User Guide www.BDTIC.com/XILINX UG445 (v1.0) June 26, 2007

... The CoolRunner XPLA3 has a half latch feature on the I/Os. The half latch is essentially a pull-up that turns on only when the I/O pin voltage is in the linear region (not a 0, not a 1). So, when the voltage at the pin is in the trip-point region or higher, the half latch will be enabled. The idea i ...

... The CoolRunner XPLA3 has a half latch feature on the I/Os. The half latch is essentially a pull-up that turns on only when the I/O pin voltage is in the linear region (not a 0, not a 1). So, when the voltage at the pin is in the trip-point region or higher, the half latch will be enabled. The idea i ...

FDMF6705V - Extra-Small, High-Performance, High- Frequency DrMOS Module FDMF6705V - Extra-S m

... gate drive design. The 3-state gate drive has both logic HIGH level and LOW level, along with a 3-state shutdown window. When the PWM input signal enters and remains within the 3-state window for a defined hold-off time (tD_HOLD-OFF), both GL and GH are pulled LOW. This feature enables the gate driv ...

... gate drive design. The 3-state gate drive has both logic HIGH level and LOW level, along with a 3-state shutdown window. When the PWM input signal enters and remains within the 3-state window for a defined hold-off time (tD_HOLD-OFF), both GL and GH are pulled LOW. This feature enables the gate driv ...

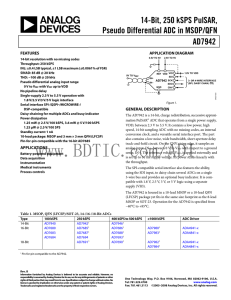

AD7942 数据手册DataSheet下载

... when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provide ...

... when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provide ...

SP3249E 数据资料DataSheet下载

... of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device. VCC.................... ...

... of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device. VCC.................... ...

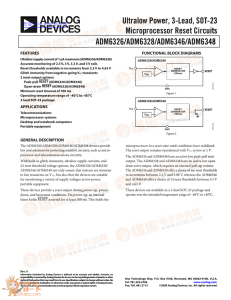

Ultralow Power, 3-Lead, SOT-23 Microprocessor Reset Circuits

... low cost solutions for protecting sensitive circuitry, such as microprocessor and telecommunications circuitry. With built-in glitch immunity, ultralow supply currents, and 24 reset threshold voltage options, the ADM6326/ADM6328/ ADM6346/ADM6348 not only ensure that systems are immune to fast transi ...

... low cost solutions for protecting sensitive circuitry, such as microprocessor and telecommunications circuitry. With built-in glitch immunity, ultralow supply currents, and 24 reset threshold voltage options, the ADM6326/ADM6328/ ADM6346/ADM6348 not only ensure that systems are immune to fast transi ...

LVDS Owner’s Manual Including High-Speed CML and Signal Conditioning 2008 national.com/LVDS

... applications, LVDS continued to evolve over the last decade to meet specific requirements such as Bus LVDS and Multipoint LVDS. For example, the latest LVDS products are capable of data rates in excess of 3 Gbps while still maintaining the low power and noise immunity characteristics. Today, many ap ...

... applications, LVDS continued to evolve over the last decade to meet specific requirements such as Bus LVDS and Multipoint LVDS. For example, the latest LVDS products are capable of data rates in excess of 3 Gbps while still maintaining the low power and noise immunity characteristics. Today, many ap ...

FOD8318 2.5 A Output Current, IGBT Drive Optocoupler

... diode is recommended to be connected between VE and VSS to protect against a reverse voltage greater than 0.5 V. Refer to application information, “6. Active Miller Clamp Function” on page 25. 3. No derating required across temperature range. 4. Derate linearly above 64 °C, free air temperature at a ...

... diode is recommended to be connected between VE and VSS to protect against a reverse voltage greater than 0.5 V. Refer to application information, “6. Active Miller Clamp Function” on page 25. 3. No derating required across temperature range. 4. Derate linearly above 64 °C, free air temperature at a ...

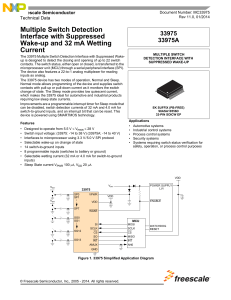

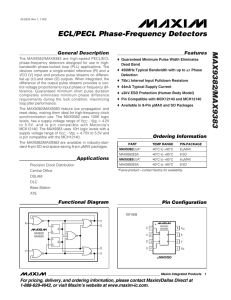

MAX9382/MAX9383 ECL/PECL Phase

... The MAX9382/MAX9383 are high-speed phase or frequency detectors. The MAX9382 is compatible with 100K logic and has a power-supply range of VCC - VEE = 4.2V to 5.5V. The MAX9383 is compatible with 10H logic with a power-supply range of VCC - VEE = 4.75V to 5.5V. Both devices are specified to function ...

... The MAX9382/MAX9383 are high-speed phase or frequency detectors. The MAX9382 is compatible with 100K logic and has a power-supply range of VCC - VEE = 4.2V to 5.5V. The MAX9383 is compatible with 10H logic with a power-supply range of VCC - VEE = 4.75V to 5.5V. Both devices are specified to function ...

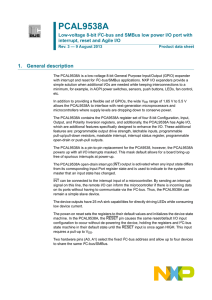

PCAL9538A 1. General description Low-voltage 8-bit I

... The PCAL9538A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...

... The PCAL9538A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...

2102-282 Digital Electronics - IC Design & Application Research Lab.

... Building A (Static) Latch For a latch, use the clock as a decoupling signal, that distinguishes between the transparent and opaque states ...

... Building A (Static) Latch For a latch, use the clock as a decoupling signal, that distinguishes between the transparent and opaque states ...

UM0529

... allows direct powering from the VBUS. The transceivers also support sharing mode when VBUS is not present which allows the D+/D- lines to be shared with other serial protocols. They are also designed to operate down to 1.6 V so that they are compatible with lower system voltages of most portable sys ...

... allows direct powering from the VBUS. The transceivers also support sharing mode when VBUS is not present which allows the D+/D- lines to be shared with other serial protocols. They are also designed to operate down to 1.6 V so that they are compatible with lower system voltages of most portable sys ...

74HC(T) - Nexperia

... gated active LOW-going edge input (nA) or the active HIGH-going edge input (nB). By repeating this process, the output pulse period (nQ = HIGH, nQ = LOW) can be made as long as desired. Alternatively an output delay can be terminated at any time by a LOW-going edge on input nRD, which also inhibits ...

... gated active LOW-going edge input (nA) or the active HIGH-going edge input (nB). By repeating this process, the output pulse period (nQ = HIGH, nQ = LOW) can be made as long as desired. Alternatively an output delay can be terminated at any time by a LOW-going edge on input nRD, which also inhibits ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.