MAX6969 16-Port, 5.5V Constant-Current LED Driver General Description Features

... shifted into a 16-bit shift register using data input DIN and clock input CLK. Input data appears at the DOUT output 16 clock cycles later to allow cascading of multiple MAX6969s. The latch-enable input, LE, loads the 16 bits of shift register data into a 16-bit output latch to set which LEDs are on ...

... shifted into a 16-bit shift register using data input DIN and clock input CLK. Input data appears at the DOUT output 16 clock cycles later to allow cascading of multiple MAX6969s. The latch-enable input, LE, loads the 16 bits of shift register data into a 16-bit output latch to set which LEDs are on ...

Switching System - Market Central Inc

... WARRANTY Market Central warrants to the original purchaser only that the products which are the subject of this Contract will be free of defects in workmanship and materials, under normal service and use, for a period of one (1) year from date of sale. Products which have been changed or altered in ...

... WARRANTY Market Central warrants to the original purchaser only that the products which are the subject of this Contract will be free of defects in workmanship and materials, under normal service and use, for a period of one (1) year from date of sale. Products which have been changed or altered in ...

United States Court of Appeals for the Federal Circuit

... asserts that the claims are silent regarding how the substrate-well junction is reverse-biased and that they only require the substrate to be at a voltage that is negative with respect to the voltage of the well. We disagree, for as noted above, the claims do not simply recite that the substrate vol ...

... asserts that the claims are silent regarding how the substrate-well junction is reverse-biased and that they only require the substrate to be at a voltage that is negative with respect to the voltage of the well. We disagree, for as noted above, the claims do not simply recite that the substrate vol ...

The I2C-bus and how to use it (including specifications)

... master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave. ...

... master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave. ...

Evaluates: MAX8600/MAX8601 MAX8601 Evaluation Kit General Description Features

... The MAX8601 contains an open-drain POK output that goes low when a valid input source is detected at DC or USB. A valid input source is one whose voltage exceeds the rising UVLO threshold of 4V, exceeds the battery voltage by 255mV, and does not exceed 7.5V. After a valid input has been established, ...

... The MAX8601 contains an open-drain POK output that goes low when a valid input source is detected at DC or USB. A valid input source is one whose voltage exceeds the rising UVLO threshold of 4V, exceeds the battery voltage by 255mV, and does not exceed 7.5V. After a valid input has been established, ...

ADS1251 数据资料 dataSheet 下载

... There is an additional benefit in using a lower data output rate. It provides better rejection of signals in the frequency band of interest. For example, with a 50Hz data output rate, a significant signal at 75Hz may alias back into the passband at 25Hz. This is due to the fact that rejection at 75H ...

... There is an additional benefit in using a lower data output rate. It provides better rejection of signals in the frequency band of interest. For example, with a 50Hz data output rate, a significant signal at 75Hz may alias back into the passband at 25Hz. This is due to the fact that rejection at 75H ...

Beam Position Monitor for a Particle Accelerator Final Report Spring

... mode), the first op-amp tracks the input voltage and charges a capacitor to match the input value. When the switch is open (hold mode), the capacitor holds that value until you are ready to process the data, at which point the sampled value is digitized by an A/D converter. There are many design par ...

... mode), the first op-amp tracks the input voltage and charges a capacitor to match the input value. When the switch is open (hold mode), the capacitor holds that value until you are ready to process the data, at which point the sampled value is digitized by an A/D converter. There are many design par ...

Computer Numerical Control for my RF- 30 Mill/Drill

... has the potential of providing excellent isolation between the parallel port and the CNC circuits. Too bad they connected all of the optos to the same ground! They could have saved money and just installed NPN transistors. This design error was not as serious as it might sound. The motor drivers hav ...

... has the potential of providing excellent isolation between the parallel port and the CNC circuits. Too bad they connected all of the optos to the same ground! They could have saved money and just installed NPN transistors. This design error was not as serious as it might sound. The motor drivers hav ...

BDTIC EiceDRIVER 2 E D 3 0 0 C 1 7 -...

... Undervoltage monitoring is implemented for both secondary sides, positive and negative driver supply voltages are monitored. The Signal and Logic side is not monitored. Undervoltage lockout functionality in both driver channels ensures correct IGBT switching operation. If the absolute value of one o ...

... Undervoltage monitoring is implemented for both secondary sides, positive and negative driver supply voltages are monitored. The Signal and Logic side is not monitored. Undervoltage lockout functionality in both driver channels ensures correct IGBT switching operation. If the absolute value of one o ...

October 2007 - Measure Microamps to Amps or

... The gain of the LTC6102 can be set with two external resistors. Gain error is limited only by these external components, not poorly specified internal resistors or saturation voltages. The external input resistor allows a wide choice of gains, as well as control of input and output impedances. For e ...

... The gain of the LTC6102 can be set with two external resistors. Gain error is limited only by these external components, not poorly specified internal resistors or saturation voltages. The external input resistor allows a wide choice of gains, as well as control of input and output impedances. For e ...

MAX9121/MAX9122 Quad LVDS Line Receivers with Integrated Termination and Flow-Through Pinout General Description

... data at speeds up to 500Mbps (250MHz) over controlledimpedance media of approximately 100Ω. The transmission media may be printed circuit (PC) board traces or cables. The MAX9121/MAX9122 accept four LVDS differential inputs and translate them to LVCMOS outputs. The MAX9122 features integrated parall ...

... data at speeds up to 500Mbps (250MHz) over controlledimpedance media of approximately 100Ω. The transmission media may be printed circuit (PC) board traces or cables. The MAX9121/MAX9122 accept four LVDS differential inputs and translate them to LVCMOS outputs. The MAX9122 features integrated parall ...

Evaluates: MAX105/MAX107 MAX105 Evaluation Kit General Description Features

... Each ADC provides six differential outputs (two’s complement code) at 800MHz, which fan out to 12 differential outputs at 400MHz after the on-chip demultiplexer. To interface with lower supply CMOS DSP chips, all outputs provide LVDS-compatible voltage levels. The LVDS outputs will have approximatel ...

... Each ADC provides six differential outputs (two’s complement code) at 800MHz, which fan out to 12 differential outputs at 400MHz after the on-chip demultiplexer. To interface with lower supply CMOS DSP chips, all outputs provide LVDS-compatible voltage levels. The LVDS outputs will have approximatel ...

Fault Diagnosis and Logic Debugging Using

... Recent years have seen an increased use of Boolean Satisfiability (SAT) based tools in the design cycle. Design verification and model checking [4][5], test generation [6], optimization [10] and physical design [12], among others, have been successfully tackled with SAT-based solutions. This is due ...

... Recent years have seen an increased use of Boolean Satisfiability (SAT) based tools in the design cycle. Design verification and model checking [4][5], test generation [6], optimization [10] and physical design [12], among others, have been successfully tackled with SAT-based solutions. This is due ...

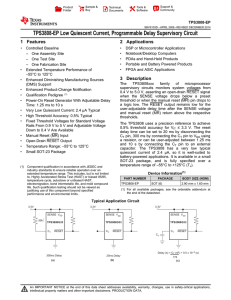

Low Quiescent Current, Programmable Delay Supervisory Circuit

... 8.1 Application Information The following sections describe in detail how to properly use this device depending on the requirements of the final application. 8.1.1 SENSE Input The SENSE input provides a terminal at which any system voltage can be monitored. If the voltage on this pin drops below VIT ...

... 8.1 Application Information The following sections describe in detail how to properly use this device depending on the requirements of the final application. 8.1.1 SENSE Input The SENSE input provides a terminal at which any system voltage can be monitored. If the voltage on this pin drops below VIT ...

BDTIC www.BDTIC.com/infineon Industrial and Multimarket

... The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disc ...

... The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disc ...