MAX6736–MAX6745 Low-Power Dual-/Triple-Voltage SC70 µP Supervisory Circuits General Description

... reset timeout period. RESET is forced low if MR is low for at least the MR minimum input pulse width. It remains low for the MR reset timeout period after MR goes high. The pushpull output is referenced to VCC1. The MAX6736/MAX6738 open-drain outputs require an external pullup resistor. The MAX6740/ ...

... reset timeout period. RESET is forced low if MR is low for at least the MR minimum input pulse width. It remains low for the MR reset timeout period after MR goes high. The pushpull output is referenced to VCC1. The MAX6736/MAX6738 open-drain outputs require an external pullup resistor. The MAX6740/ ...

CR26645650

... The operation of the prototype is controlled with digital signal processor (DSP) ADMC331BST, a low cost single chip DSP microcontroller optimized for standing alone applications. The microcontroller integrates a 26 MHz fixed- point DSP core and a set of control peripherals including seven analog inp ...

... The operation of the prototype is controlled with digital signal processor (DSP) ADMC331BST, a low cost single chip DSP microcontroller optimized for standing alone applications. The microcontroller integrates a 26 MHz fixed- point DSP core and a set of control peripherals including seven analog inp ...

P0024_pdf - Acuity Brands

... 3. To reduce the risk of fire and burns, do not install this lighting system where the exposed bare connectors can be shorted or contact any conductive materials. 4. To reduce the risk of fire and overheating, make sure all connections are tight. 5. Do not install any luminaire closer than 6 inch ...

... 3. To reduce the risk of fire and burns, do not install this lighting system where the exposed bare connectors can be shorted or contact any conductive materials. 4. To reduce the risk of fire and overheating, make sure all connections are tight. 5. Do not install any luminaire closer than 6 inch ...

MAX5109 Nonvolatile, Dual, 8-Bit DACs with 2-Wire Serial Interface General Description

... This device operates from a single +2.7V to +5.25V supply and consumes 200µA per DAC. A software-controlled power-down mode decreases supply current to less than 25µA. A software-controlled mute mode sets each DAC, or both DACs simultaneously, to their respective REFL_ voltages. The MAX5109 also inc ...

... This device operates from a single +2.7V to +5.25V supply and consumes 200µA per DAC. A software-controlled power-down mode decreases supply current to less than 25µA. A software-controlled mute mode sets each DAC, or both DACs simultaneously, to their respective REFL_ voltages. The MAX5109 also inc ...

ppt - Computer Science & Engineering

... consisting of 50% multiply instructions, 20% divide instructions, and the remaining 30% are other instructions. Management wants the machine to run 4 times faster. You can make the divide run at most 3 times faster and the multiply run at most 8 times faster. Can you meet management’s goal by making ...

... consisting of 50% multiply instructions, 20% divide instructions, and the remaining 30% are other instructions. Management wants the machine to run 4 times faster. You can make the divide run at most 3 times faster and the multiply run at most 8 times faster. Can you meet management’s goal by making ...

2.2 - KTH

... The basic assumption in synchronous system is that all the sequential elements in the design sample their input at the same time, marked by a clock signal. In reality, the clock signal does not arrive at the sequential elements at the same time. The difference in time between the reference clock sig ...

... The basic assumption in synchronous system is that all the sequential elements in the design sample their input at the same time, marked by a clock signal. In reality, the clock signal does not arrive at the sequential elements at the same time. The difference in time between the reference clock sig ...

High Speed, ESD-Protected, Full-Duplex, ADM2490E i

... logic side of the interface. Therefore, the part has two main sections: a digital isolation section and a transceiver section (see Figure 21). The driver input signal, which is applied to the TxD pin and referenced to logic ground (GND1), is coupled across an isolation barrier to appear at the trans ...

... logic side of the interface. Therefore, the part has two main sections: a digital isolation section and a transceiver section (see Figure 21). The driver input signal, which is applied to the TxD pin and referenced to logic ground (GND1), is coupled across an isolation barrier to appear at the trans ...

Multi-Cell Li-Ion Battery Management System

... components between ICs. A high-speed serial peripheral interface (SPI) bus operates between each bq76PL536 and the MSP430 microcontroller to provide reliable communications through a high-voltage battery cell stack. The battery management system can communicate with an external host or battery charg ...

... components between ICs. A high-speed serial peripheral interface (SPI) bus operates between each bq76PL536 and the MSP430 microcontroller to provide reliable communications through a high-voltage battery cell stack. The battery management system can communicate with an external host or battery charg ...

SUM 1001

... After application of the supply voltage and the falling below or exceeding of the preselected response value (based on the function selection see Table III), the output relay toggles to the operating position. This takes place either after the preselected response delay or immediately. If the respon ...

... After application of the supply voltage and the falling below or exceeding of the preselected response value (based on the function selection see Table III), the output relay toggles to the operating position. This takes place either after the preselected response delay or immediately. If the respon ...

Fast Frequency Acquisition Phase-Frequency Detectors for GSa/s

... In the second proposed design, pulsed latches are used instead of flip-flops which fundamentally changes the dependence on the reset delay. This is illustrated in Figure 5-a with the same case as before.When CKref arrives during the reset, the edge information propagates to the output as long as CKr ...

... In the second proposed design, pulsed latches are used instead of flip-flops which fundamentally changes the dependence on the reset delay. This is illustrated in Figure 5-a with the same case as before.When CKref arrives during the reset, the edge information propagates to the output as long as CKr ...

C5-2 A 10Gb/s 10mm On-Chip Serial Link in 65nm CMOS Featuring

... using an in-situ BER monitor. Introduction On-chip serial links are attractive for high-speed point-to-point applications as they can achieve 10Gb/s or higher data rates without using power-hungry and floorplan-disrupting repeaters. Several circuit techniques have been proposed to improve the commun ...

... using an in-situ BER monitor. Introduction On-chip serial links are attractive for high-speed point-to-point applications as they can achieve 10Gb/s or higher data rates without using power-hungry and floorplan-disrupting repeaters. Several circuit techniques have been proposed to improve the commun ...

SN65LVEP11 数据资料 dataSheet 下载

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

D373A Electroluminescent Lamp Driver IC

... considered as electrical shielding for any underlying circuitry in the application. The EL driving system is divided into several parts: on-chip logic and control, on-chip high voltage output circuitry, discharge logic circuitry, and off-chip components. The on-chip logic controls the lamp operating ...

... considered as electrical shielding for any underlying circuitry in the application. The EL driving system is divided into several parts: on-chip logic and control, on-chip high voltage output circuitry, discharge logic circuitry, and off-chip components. The on-chip logic controls the lamp operating ...

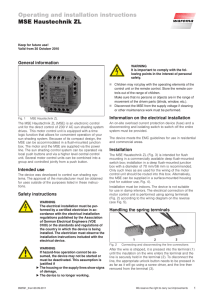

Operating and installation instructions MSE Haustechnik ZL

... - Max. group size of 200 motor control units, see voltage drop diagram. - Central control line length, see voltage drop diagram. - The power line length is limited by the total motor current. The maximum number of drives per circuit depends on their current consumption and the upstream fuse. - Max. ...

... - Max. group size of 200 motor control units, see voltage drop diagram. - Central control line length, see voltage drop diagram. - The power line length is limited by the total motor current. The maximum number of drives per circuit depends on their current consumption and the upstream fuse. - Max. ...

TD350E

... eliminate the need for a negative supply voltage. During turn-off, the gate voltage is monitored and the clamp output is activated when gate voltage goes below 2 V (relative to GND). The clamp voltage is VL+3 V max for a Miller current up to 500 mA. The clamp is disabled when the IN input is trigger ...

... eliminate the need for a negative supply voltage. During turn-off, the gate voltage is monitored and the clamp output is activated when gate voltage goes below 2 V (relative to GND). The clamp voltage is VL+3 V max for a Miller current up to 500 mA. The clamp is disabled when the IN input is trigger ...

All-sky coherent search for continuous gravitational waves in 6–7 Hz

... So our analysis is valid only for NSs with a spin-down f˙ less than 1/ 2Tobs where Tobs = 22.5 hours is the data length. We make SFTs of the 22.5 hours contiguous data by employing lalapps_MakeSFTs in the LIGO scientific collaboration analysis library (LAL) code.1 Each segment is windowed by a Tukey ...

... So our analysis is valid only for NSs with a spin-down f˙ less than 1/ 2Tobs where Tobs = 22.5 hours is the data length. We make SFTs of the 22.5 hours contiguous data by employing lalapps_MakeSFTs in the LIGO scientific collaboration analysis library (LAL) code.1 Each segment is windowed by a Tukey ...

NB3N3020DTGEVB Evaluation Board User's Manual EVAL BOARD USER’S MANUAL

... topside trace gap from the device input pin to the SMA connector by installing R14 (a Zero W resistor). Do not install R16. Do not drive X2. Use −1.3 V offset LVCMOS Clock amplitude signal from 2 MHz to 210 MHz which satisfies datasheet VIH and VIL to drive X1/CLK. Input tr/tf transition edges shoul ...

... topside trace gap from the device input pin to the SMA connector by installing R14 (a Zero W resistor). Do not install R16. Do not drive X2. Use −1.3 V offset LVCMOS Clock amplitude signal from 2 MHz to 210 MHz which satisfies datasheet VIH and VIL to drive X1/CLK. Input tr/tf transition edges shoul ...

AMI_Glossary_v0_3

... Inbound Transaction: A communication that is traveling (inward) to the central control or main office. Incremental: A small positive or negative change in the value of a variable. ...

... Inbound Transaction: A communication that is traveling (inward) to the central control or main office. Incremental: A small positive or negative change in the value of a variable. ...