ADS931 数据资料 dataSheet 下载

... The ADS931 is a high-speed sampling A/D converter that utilizes a pipeline architecture. The fully differential topology and digital error correction guarantee 8-bit resolution. The track-and-hold circuit is shown in Figure 1. The switches are controlled by an internal clock which has a non-overlapp ...

... The ADS931 is a high-speed sampling A/D converter that utilizes a pipeline architecture. The fully differential topology and digital error correction guarantee 8-bit resolution. The track-and-hold circuit is shown in Figure 1. The switches are controlled by an internal clock which has a non-overlapp ...

4.2 Digital Transmission

... Vin= amplitude of the input signal at a particular of instant time Vout= compressed output amplitude A, = parameter define the amount of compression ...

... Vin= amplitude of the input signal at a particular of instant time Vout= compressed output amplitude A, = parameter define the amount of compression ...

Full-Text PDF

... quantized into L-bit digital data. Then, the data is sent to the digital accumulator. At the second TL , the same object is captured by pixel2 and its quantized data is also sent to the digital accumulator. In the same way, the object is exposed N times, and the corresponding quantized data are adde ...

... quantized into L-bit digital data. Then, the data is sent to the digital accumulator. At the second TL , the same object is captured by pixel2 and its quantized data is also sent to the digital accumulator. In the same way, the object is exposed N times, and the corresponding quantized data are adde ...

Understanding ADC Specifications By Len Staller Silicon

... boundaries. The output code will be its lowest (000b) at less than 1/8 of the full-scale (the size of this ADC’s code width). Also, note that the ADC reaches its full-scale output code (111b) at 7/8 of full-scale, not at the full-scale value. Thus, the transition to the maximum digital output does n ...

... boundaries. The output code will be its lowest (000b) at less than 1/8 of the full-scale (the size of this ADC’s code width). Also, note that the ADC reaches its full-scale output code (111b) at 7/8 of full-scale, not at the full-scale value. Thus, the transition to the maximum digital output does n ...

XP95 Input Output Unit.indd

... After the 30 second period, ie, during normal operation, the relay changes state within 0.1 second of receipt of a command. The seven bits which are then transmitted by the control panel correspond to the address (as set on the DIL switch) of the device to be polled. A response message is then sent ...

... After the 30 second period, ie, during normal operation, the relay changes state within 0.1 second of receipt of a command. The seven bits which are then transmitted by the control panel correspond to the address (as set on the DIL switch) of the device to be polled. A response message is then sent ...

ADS900 数据资料 dataSheet 下载

... charge redistributes between CI and CH, completing one track-and-hold cycle. The differential output is a held DC representation of the analog input at the sample time. In the normal mode of operation, the complementary input is tied to the common-mode voltage. In this case, the track-andhold circui ...

... charge redistributes between CI and CH, completing one track-and-hold cycle. The differential output is a held DC representation of the analog input at the sample time. In the normal mode of operation, the complementary input is tied to the common-mode voltage. In this case, the track-andhold circui ...

ADS901 数据资料 dataSheet 下载

... 10-bit resolution. The differential track/hold circuit is shown in Figure 1. The switches are controlled by an internal clock which has a non-overlapping two phase signal, φ1 and φ2. At the sampling time the input signal is sampled on the bottom plates of the input capacitors. In the next clock phas ...

... 10-bit resolution. The differential track/hold circuit is shown in Figure 1. The switches are controlled by an internal clock which has a non-overlapping two phase signal, φ1 and φ2. At the sampling time the input signal is sampled on the bottom plates of the input capacitors. In the next clock phas ...

Notes on Pulse Modulation

... Dynamic Range (DR): It determines the number of PCM bits transmitted per sample. -- Dynamic range is the ratio of the largest possible magnitude to the smallest possible magnitude (other than zero) that can be decoded by the digital-to-analog converter in the receiver. Mathematically, ...

... Dynamic Range (DR): It determines the number of PCM bits transmitted per sample. -- Dynamic range is the ratio of the largest possible magnitude to the smallest possible magnitude (other than zero) that can be decoded by the digital-to-analog converter in the receiver. Mathematically, ...

Selecting A/D Converters

... never deviates by more than ±1/2 LSB from where it should be. That’s a good specification, but note that gain and offset errors have been adjusted prior to making the measurement. Over a finite temperature range, the temperature coefficients of gain and offset must be taken into account. The differe ...

... never deviates by more than ±1/2 LSB from where it should be. That’s a good specification, but note that gain and offset errors have been adjusted prior to making the measurement. Over a finite temperature range, the temperature coefficients of gain and offset must be taken into account. The differe ...

Audio preamplifier vvith no t.i.d. - Keith

... But the return to valve circuits is hardly justified, even though it leads to a decrease in transient intermodulation. As to semiconductor amplifiers the situation for most of their technical parameters is more favourable, i.e. frequency properties, noise characteris tics, and power consumption. Th ...

... But the return to valve circuits is hardly justified, even though it leads to a decrease in transient intermodulation. As to semiconductor amplifiers the situation for most of their technical parameters is more favourable, i.e. frequency properties, noise characteris tics, and power consumption. Th ...

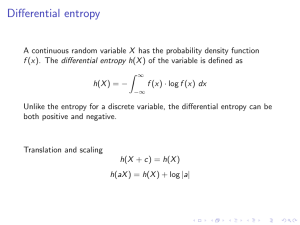

Differential entropy

... The decoder will decode the symbols that the coder kept and set the rest to 0 (the most probable value). On average, the fraction of incorrectly decoded symbols will be (1 − k)(1 − p), which is equal to the distortion ...

... The decoder will decode the symbols that the coder kept and set the rest to 0 (the most probable value). On average, the fraction of incorrectly decoded symbols will be (1 − k)(1 − p), which is equal to the distortion ...

Pulse modulation

... two rightmost bits represent magnitude. • This type of code is called a folded binary code because the codes on the bottom half of the table are a mirror image of the codes on the top half, except for the sign bit. ...

... two rightmost bits represent magnitude. • This type of code is called a folded binary code because the codes on the bottom half of the table are a mirror image of the codes on the top half, except for the sign bit. ...

Rapid single flux quantum technology for SQUID

... to achieve much better sensitivity under optimal conditions. It is seen that in Fig. 9, we have also sharp thresholds coinciding in all three comparators. The reason for their better noise is higher signal-to-delay conversion ratio (which is about two orders of magnitude higher near these thresholds ...

... to achieve much better sensitivity under optimal conditions. It is seen that in Fig. 9, we have also sharp thresholds coinciding in all three comparators. The reason for their better noise is higher signal-to-delay conversion ratio (which is about two orders of magnitude higher near these thresholds ...

Analog to Digital Converters (ADC)

... ◊ Quantization errors are a normal occurrence for ADCs. The input voltage will commonly have a value that is between the LSB voltage step and must be rounded up or down. ◊ For instance, if the resolution is 20mV per bit and a value of 10 mV is applied, the ADC will interpret this as either 0v or 20 ...

... ◊ Quantization errors are a normal occurrence for ADCs. The input voltage will commonly have a value that is between the LSB voltage step and must be rounded up or down. ◊ For instance, if the resolution is 20mV per bit and a value of 10 mV is applied, the ADC will interpret this as either 0v or 20 ...

PCM and Sampling Notes

... In quantization the levels are assigned a binary codeword. All sample values falling between two quantization levels are considered to be located at the centre of the quantization interval. In this manner the quantization process introduces a certain amount of error or distortion into the signal sam ...

... In quantization the levels are assigned a binary codeword. All sample values falling between two quantization levels are considered to be located at the centre of the quantization interval. In this manner the quantization process introduces a certain amount of error or distortion into the signal sam ...

AN100 An overview of data converters

... DAC output, the MSB is left high and the next bit is set. The input is The type of converter chosen for a given application depends upon again compared with the DAC output and the second bit cleared or many things; the accuracy required, the conversion speed left high, based on the same criteria as ...

... DAC output, the MSB is left high and the next bit is set. The input is The type of converter chosen for a given application depends upon again compared with the DAC output and the second bit cleared or many things; the accuracy required, the conversion speed left high, based on the same criteria as ...

EECS 373 Design of Microprocessor-Based Systems

... Signals can be expressed as weighted sums of harmonic functions. Shannon’s Theorem (Nyquist Sampling Theorem) To sample a bandlimited signal x(t) with no loss of information, the sampling rate must be at least twice the frequency of the highest frequency component. Example: Audio signals typically i ...

... Signals can be expressed as weighted sums of harmonic functions. Shannon’s Theorem (Nyquist Sampling Theorem) To sample a bandlimited signal x(t) with no loss of information, the sampling rate must be at least twice the frequency of the highest frequency component. Example: Audio signals typically i ...

Lab 6 - Digital Signals and A/D and D/A Conversion

... access the various A/D and D/A ports on the I/O card. The program LabView is used to control the acquisition of signals from the A/D ports, processing these signals by sampling and filtering, and sending the resulting signals out to the D/A ports. We will use a LabView Virtual Instrument (“Digital A ...

... access the various A/D and D/A ports on the I/O card. The program LabView is used to control the acquisition of signals from the A/D ports, processing these signals by sampling and filtering, and sending the resulting signals out to the D/A ports. We will use a LabView Virtual Instrument (“Digital A ...

Analog to Digital (A/D) Conversion

... • Conversion Rate – The rate at which an A/D converter can make a conversion is critical. In general higher resolutions require greater time of greater cost or both. – Typically specified in samples per second (sometimes MSPS) ...

... • Conversion Rate – The rate at which an A/D converter can make a conversion is critical. In general higher resolutions require greater time of greater cost or both. – Typically specified in samples per second (sometimes MSPS) ...

"The design of sigma-delta modulation analog-to-digital converters,"

... quantization noise at low frequencies while emphasizing the high-frequency noise. Since the signal is sampled at a frequency which is much greater than the Nyquist rate, high-frequency quantization noise can be removed without affecting the signal band by means of a digital low-pass filter operating ...

... quantization noise at low frequencies while emphasizing the high-frequency noise. Since the signal is sampled at a frequency which is much greater than the Nyquist rate, high-frequency quantization noise can be removed without affecting the signal band by means of a digital low-pass filter operating ...

report

... The comparator can be basically defined as a quantizer where in the quantization noise forms the crux of the ADC design. A quantizer is a device that converts a continuous range of input amplitude levels into a finite set of discrete digital code words. Theoretically an analog-to-digital conversion ...

... The comparator can be basically defined as a quantizer where in the quantization noise forms the crux of the ADC design. A quantizer is a device that converts a continuous range of input amplitude levels into a finite set of discrete digital code words. Theoretically an analog-to-digital conversion ...

Analog to Digital (A/D) Conversion

... • Some A/D converters require the input analog signal to be held constant during conversion, (eg. successive approximation devices) • In other cases, peak capture or sampling at a specific point in time necessitates a sampling device. • This function is accomplished by a sample and hold device as sh ...

... • Some A/D converters require the input analog signal to be held constant during conversion, (eg. successive approximation devices) • In other cases, peak capture or sampling at a specific point in time necessitates a sampling device. • This function is accomplished by a sample and hold device as sh ...

Quantization (signal processing)

Quantization, in mathematics and digital signal processing, is the process of mapping a large set of input values to a (countable) smaller set. Rounding and truncation are typical examples of quantization processes. Quantization is involved to some degree in nearly all digital signal processing, as the process of representing a signal in digital form ordinarily involves rounding. Quantization also forms the core of essentially all lossy compression algorithms. The difference between an input value and its quantized value (such as round-off error) is referred to as quantization error. A device or algorithmic function that performs quantization is called a quantizer. An analog-to-digital converter is an example of a quantizer.