A Direct Digital Frequency Synthesizer With Fourth

... output and the second term is the error introduced by phase truncation. As shown, the phase truncation error gives an amplitude. modulated term on the quadrature output of The phase error sequence represented by the truncated bits satisfies the condition that . The phase truncation causes errors onl ...

... output and the second term is the error introduced by phase truncation. As shown, the phase truncation error gives an amplitude. modulated term on the quadrature output of The phase error sequence represented by the truncated bits satisfies the condition that . The phase truncation causes errors onl ...

Less Than One in a Quadrillion—A Test Method

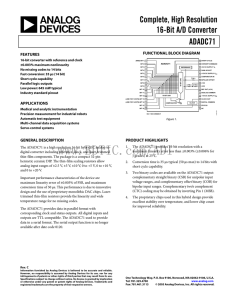

... The integral nonlinearity (INL) of the ADC is the transfer function across the full-scale ADC input range of the actual samples code relative to the ideal output (Kester, 2005). This information is also typically specified and plotted in an ADC data sheet. The maximum deviation to the ideal code is ...

... The integral nonlinearity (INL) of the ADC is the transfer function across the full-scale ADC input range of the actual samples code relative to the ideal output (Kester, 2005). This information is also typically specified and plotted in an ADC data sheet. The maximum deviation to the ideal code is ...

Next Topic: NOISE

... is easily extende/ to distortion of any order. Assume that the intercepts of both stages have beer( normalized to the same plane in the cascade. The intercepts will be designated by 1,, where the subscript n denotes the stage. D" will refer to a distortion power while P" will describe the desired ou ...

... is easily extende/ to distortion of any order. Assume that the intercepts of both stages have beer( normalized to the same plane in the cascade. The intercepts will be designated by 1,, where the subscript n denotes the stage. D" will refer to a distortion power while P" will describe the desired ou ...

Design of a 14-bit fully differential discrete time delta

... shaping technique is also used in ∆Σ converters in addition to oversampling to achieve a high resolution conversion. A significant advantage of the method is that analog signals are converted using simple and high-tolerance analog circuits, usually a 1-bit comparator, and analog signal processing ci ...

... shaping technique is also used in ∆Σ converters in addition to oversampling to achieve a high resolution conversion. A significant advantage of the method is that analog signals are converted using simple and high-tolerance analog circuits, usually a 1-bit comparator, and analog signal processing ci ...

New Logarithmic Two-Step Flash A/D Converter with Digital Error

... multiplication, this operation corresponds to an amplification dependent on the scale offset introduced. The higher the offset the lower the comparator gain needed. If we shift the second ADC scale near the top of the input range and leave some additional transition steps at the top and at the botto ...

... multiplication, this operation corresponds to an amplification dependent on the scale offset introduced. The higher the offset the lower the comparator gain needed. If we shift the second ADC scale near the top of the input range and leave some additional transition steps at the top and at the botto ...

Minimizing Distortion in Operational Transconductance Amplifiers

... x3 and x5 become very small, such that they can usually be ignored. But, this requires that Io Iabc , which also means that Vi Vt ≈ 26mV. At these low input levels, the OTA noise is a much larger fraction of the signal, and for DC coupled circuits, the offset voltage is on the same order as the ...

... x3 and x5 become very small, such that they can usually be ignored. But, this requires that Io Iabc , which also means that Vi Vt ≈ 26mV. At these low input levels, the OTA noise is a much larger fraction of the signal, and for DC coupled circuits, the offset voltage is on the same order as the ...

2011_6_june_Griffith_CSISCS_slides

... • This was not fully modeled during design • Re-evaluation by simulation shows the peaking ...

... • This was not fully modeled during design • Re-evaluation by simulation shows the peaking ...

DN439 - Signal Chain Noise Analysis for RF-to-Digital Receivers

... and Its Specification for Each Section, Are Included ...

... and Its Specification for Each Section, Are Included ...

ABCs of ADCs - Analog-to-Digital Converter Basics

... In an ideal converter, the code-to-code transition points are exactly 1 LSB apart. In an 8-bit ADC, for example, these changes are separated from each other by 1 LSB, or 1/256 of fullscale. The difference between the ideal 1 LSB and the worst case actual input voltage change between output code tran ...

... In an ideal converter, the code-to-code transition points are exactly 1 LSB apart. In an 8-bit ADC, for example, these changes are separated from each other by 1 LSB, or 1/256 of fullscale. The difference between the ideal 1 LSB and the worst case actual input voltage change between output code tran ...

MAX1177 16-Bit, 135ksps, Single-Supply ADC with 0 to 10V Input Range General Description

... The MAX1177 has an input scaler, which allows conversion of input voltages ranging from 0 to 10V, while operating from a single +5V analog supply. The input scaler attenuates and shifts the analog input to match the input range of the internal digital-to-analog converter (DAC). Figure 4 shows the eq ...

... The MAX1177 has an input scaler, which allows conversion of input voltages ranging from 0 to 10V, while operating from a single +5V analog supply. The input scaler attenuates and shifts the analog input to match the input range of the internal digital-to-analog converter (DAC). Figure 4 shows the eq ...

Optimize the Buffer Amplifier/ADC Connection

... third-order intercept point (IP3), an imaginary number that marks the point at which a receiver’s front-end components will be overloaded or saturated into compression. Dynamic range is a compromise, of course, because high sensitivity requires a low noise figure and a high gain. Unfortunately, prac ...

... third-order intercept point (IP3), an imaginary number that marks the point at which a receiver’s front-end components will be overloaded or saturated into compression. Dynamic range is a compromise, of course, because high sensitivity requires a low noise figure and a high gain. Unfortunately, prac ...

Locality Preserving Hashing Kang Zhao, Hongtao Lu and Jincheng Mei

... with good performance is still a challenge. In many cases, the real-world data lies on a low-dimensional manifold embedded in high-dimensional ambient space. To capture meaningful neighbors, a compact hashing representation should be able to uncover the intrinsic geometric structure of the manifold, ...

... with good performance is still a challenge. In many cases, the real-world data lies on a low-dimensional manifold embedded in high-dimensional ambient space. To capture meaningful neighbors, a compact hashing representation should be able to uncover the intrinsic geometric structure of the manifold, ...

High-Speed ADC Sets Input Common-Mode Range

... track each other to ensure a proper matching of dc voltage levels. The COM pin sources 5mA, and can be used as needed to set the dc level of other circuit elements in the system. Because the COM internal buffers are powered down during ADC shutdown, this level-setting approach saves more power than ...

... track each other to ensure a proper matching of dc voltage levels. The COM pin sources 5mA, and can be used as needed to set the dc level of other circuit elements in the system. Because the COM internal buffers are powered down during ADC shutdown, this level-setting approach saves more power than ...

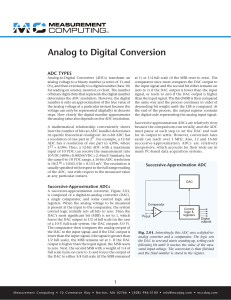

Analog to Digital Conversion

... In a theoretically perfect ADC, any particular analog voltage measured should be represented by a unique digital code, accurate to an infinite number of digits. (See Figure 2.07A.) But in a real ADC, small but finite gaps exist between one digital number and a consecutive digital number, and the amo ...

... In a theoretically perfect ADC, any particular analog voltage measured should be represented by a unique digital code, accurate to an infinite number of digits. (See Figure 2.07A.) But in a real ADC, small but finite gaps exist between one digital number and a consecutive digital number, and the amo ...

Function approximation and fitting. ALICE selected

... Run 1 with standard CPass0/Cpass1 calibration (*) RUN 2 corrections status as of the end of February 1st results from alternative approach (bigger granularity of the maps, better outliers handling) 17th ...

... Run 1 with standard CPass0/Cpass1 calibration (*) RUN 2 corrections status as of the end of February 1st results from alternative approach (bigger granularity of the maps, better outliers handling) 17th ...

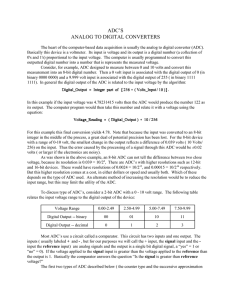

ADC`S ANALOG TO DIGITAL CONVERTERS

... type) are like a systematic approach to a number guessing game ( I am thinking of a number between 0 and 16) in which after each guess the one making the guesses is told if her last guess is high or low. If a young child were playing the game, he might just make random guesses. A slightly older chi ...

... type) are like a systematic approach to a number guessing game ( I am thinking of a number between 0 and 16) in which after each guess the one making the guesses is told if her last guess is high or low. If a young child were playing the game, he might just make random guesses. A slightly older chi ...

- National Grid

... IEC 61000-3-6 and IEC 61000-3-14 (draft) specify that the 99% percentile value of 3 s measurements should be used assessment against the short-term planning levels. However, as discussed in 9.2, portable instruments do not generally have the facility for logging every 3 s value. It is therefore reco ...

... IEC 61000-3-6 and IEC 61000-3-14 (draft) specify that the 99% percentile value of 3 s measurements should be used assessment against the short-term planning levels. However, as discussed in 9.2, portable instruments do not generally have the facility for logging every 3 s value. It is therefore reco ...

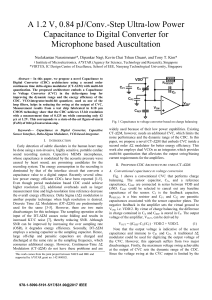

A 1.2 V, 0.84 pJ/Conv.-Step Ultra-low Power Capacitance to Digital

... capacitance value to a digital output. Recently several ultralow power energy efficient CDCs have been reported [1-5]. Even though period modulation based CDC could achieve higher resolution [2], additional overheads such as larger measurement time and high-resolution time reference decrease the ove ...

... capacitance value to a digital output. Recently several ultralow power energy efficient CDCs have been reported [1-5]. Even though period modulation based CDC could achieve higher resolution [2], additional overheads such as larger measurement time and high-resolution time reference decrease the ove ...

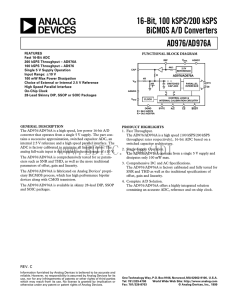

AD976 数据手册DataSheet下载

... quantization levels. The more levels, the lower the quantization noise. The theoretical S/(N+D) for a sine wave input signal can be calculated using the following: S/(N+D) = (6.02N + 1.76) dB ...

... quantization levels. The more levels, the lower the quantization noise. The theoretical S/(N+D) for a sine wave input signal can be calculated using the following: S/(N+D) = (6.02N + 1.76) dB ...

Quantization (signal processing)

Quantization, in mathematics and digital signal processing, is the process of mapping a large set of input values to a (countable) smaller set. Rounding and truncation are typical examples of quantization processes. Quantization is involved to some degree in nearly all digital signal processing, as the process of representing a signal in digital form ordinarily involves rounding. Quantization also forms the core of essentially all lossy compression algorithms. The difference between an input value and its quantized value (such as round-off error) is referred to as quantization error. A device or algorithmic function that performs quantization is called a quantizer. An analog-to-digital converter is an example of a quantizer.