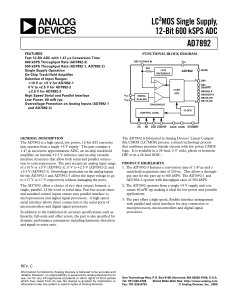

General Description Features and Benefits

... The MAX11905 is a 20-bit, 1.6Msps, single-channel, fully differential SAR ADC with internal reference buffers. The MAX11905 provides excellent static and dynamic performance with best-in-class power consumption that directly scales with throughput. The device has a unipolar differential ±VREF input ...

... The MAX11905 is a 20-bit, 1.6Msps, single-channel, fully differential SAR ADC with internal reference buffers. The MAX11905 provides excellent static and dynamic performance with best-in-class power consumption that directly scales with throughput. The device has a unipolar differential ±VREF input ...

A Single-Slope 80 MS/s ADC Using Two-Step Time to

... element, we instead draw off of recent advances in timeto-digital conversion (TDC) to perform this operation. In particular, we leverage a recently published TDC based on a multipath gated ring oscillator (GRO) structure that achieves better than 10ps of time resolution with a wide dynamic range. To ...

... element, we instead draw off of recent advances in timeto-digital conversion (TDC) to perform this operation. In particular, we leverage a recently published TDC based on a multipath gated ring oscillator (GRO) structure that achieves better than 10ps of time resolution with a wide dynamic range. To ...

Background calibration techniques for multistage pipelined

... Resistor string DAC with slow-but-accurate deltasigma ADC and skip-and-fill algorithm • Bandwidth limitation ...

... Resistor string DAC with slow-but-accurate deltasigma ADC and skip-and-fill algorithm • Bandwidth limitation ...

DACs

... Basically “differential” non-linearity expresses the error in step size as a fraction of LSB The DNL is the maximum of these deviations over the entire transfer function One must choose a DAC with DNL less than 1 LSB. A DNL > 1 LSB will lead to non-monotonic behavior. This means that for certain ste ...

... Basically “differential” non-linearity expresses the error in step size as a fraction of LSB The DNL is the maximum of these deviations over the entire transfer function One must choose a DAC with DNL less than 1 LSB. A DNL > 1 LSB will lead to non-monotonic behavior. This means that for certain ste ...

Analog to Digital Converters (ADC)

... ◊ The Dual Slope method takes time for the conversion to occur. Each additional bit improves resolution but also adds a significant bit to the counter, costing considerable time. This type of ADC is therefore unsuitable for rapidly changing analog input. ◊ Each clocking pulse increments the counter ...

... ◊ The Dual Slope method takes time for the conversion to occur. Each additional bit improves resolution but also adds a significant bit to the counter, costing considerable time. This type of ADC is therefore unsuitable for rapidly changing analog input. ◊ Each clocking pulse increments the counter ...

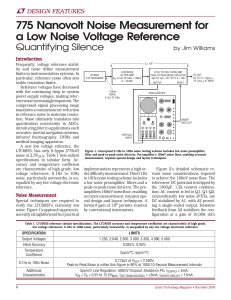

775 Nanovolt Noise Measurement for a Low Noise Voltage Reference

... ated low noise 1.2k resistor, are fully shielded against pick-up. FETs Q1 and Q2 differentially feed A2, forming a simple low noise op amp. Feedback, provided by the 100k-10Ω pair, sets closed loop gain at 10,000. Although Q1 and Q2 have extraordinarily low noise characteristics, their offset and dr ...

... ated low noise 1.2k resistor, are fully shielded against pick-up. FETs Q1 and Q2 differentially feed A2, forming a simple low noise op amp. Feedback, provided by the 100k-10Ω pair, sets closed loop gain at 10,000. Although Q1 and Q2 have extraordinarily low noise characteristics, their offset and dr ...

DCDRew

... DCD is implemented in UMC 0.18 um CMOS technology 3.2mm x 5mm DCD-B uses bump bonding on the UMC technology provided by EuroPractice. DCD has 256 analog channels each housing an input stage and ADCs (1 pipeline or 2 cyclic). ...

... DCD is implemented in UMC 0.18 um CMOS technology 3.2mm x 5mm DCD-B uses bump bonding on the UMC technology provided by EuroPractice. DCD has 256 analog channels each housing an input stage and ADCs (1 pipeline or 2 cyclic). ...

SCADA (Supervisory Control And Data Acquisition)

... consecutive Is or 0s, this indicates that the slope of the DAC output is less than the slope of the analog signal in either the positive or the negative direction. Essentially, the DAC has lost track of exactly where the analog samples are, and the possibility of slope overload occurring is high. Wi ...

... consecutive Is or 0s, this indicates that the slope of the DAC output is less than the slope of the analog signal in either the positive or the negative direction. Essentially, the DAC has lost track of exactly where the analog samples are, and the possibility of slope overload occurring is high. Wi ...

AN118 Improving ADC Resolution by Oversampling and Averaging

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

AN118 Improving ADC Resolution by Oversampling

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

AN118 - Silicon Labs

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

... The effectiveness of oversampling and averaging depends on the characteristics of the dominant noise sources. The key requirement is that the noise Calculating the Oversampling can be modeled as white noise. Please see Requirements To Increase SNR Appendix B for a discussion on the characteristics T ...

The ABCs of ADCs: Understanding How ADC Errors Affect System

... Many design engineers will encounter the subtleties in ADC specifications that often lead to less-than-desired system performance. This article explains how to select an ADC based on the system requirements and describes the various sources of error when making an ADC measurement. Using a 12-bit-res ...

... Many design engineers will encounter the subtleties in ADC specifications that often lead to less-than-desired system performance. This article explains how to select an ADC based on the system requirements and describes the various sources of error when making an ADC measurement. Using a 12-bit-res ...

Embedded Systems - Ulster University

... The result will be stored in one of the ADC1BUFx registers. Since we’re only requesting the analog value of one pin at a time in this manual mode, the result is always stored in the first buffer register or ADC1BUF0. The AD1CHS is the channel select SFR. Of importance to us is that AD1CHS<16:19> con ...

... The result will be stored in one of the ADC1BUFx registers. Since we’re only requesting the analog value of one pin at a time in this manual mode, the result is always stored in the first buffer register or ADC1BUF0. The AD1CHS is the channel select SFR. Of importance to us is that AD1CHS<16:19> con ...

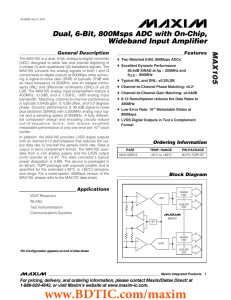

MAX105 Dual, 6-Bit, 800Msps ADC with On-Chip, Wideband Input Amplifier General Description

... The peak-to-peak input voltage required, causing a full-scale digitized output when using a trigonometric curve-fitting algorithm (e.g. FFT). Guaranteed by design and characterization. Common-mode rejection ratio is defined as the ratio of the change in the offset voltage to the change in the common ...

... The peak-to-peak input voltage required, causing a full-scale digitized output when using a trigonometric curve-fitting algorithm (e.g. FFT). Guaranteed by design and characterization. Common-mode rejection ratio is defined as the ratio of the change in the offset voltage to the change in the common ...

docx

... which is to be added by the EDA tool to the signal measured at the sampling latch of a receiver. Usage Rules: If Rx_Noise is Usage Out, then the EDA tool shall use the value returned by Rx AMI_Init if Rx AMI_GetWave is not used. If Rx AMI_GetWave is used, then the EDA tool may apply the value return ...

... which is to be added by the EDA tool to the signal measured at the sampling latch of a receiver. Usage Rules: If Rx_Noise is Usage Out, then the EDA tool shall use the value returned by Rx AMI_Init if Rx AMI_GetWave is not used. If Rx AMI_GetWave is used, then the EDA tool may apply the value return ...

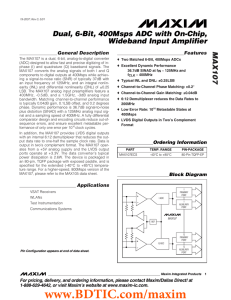

MAX107 Dual, 6-Bit, 400Msps ADC with On-Chip, Wideband Input Amplifier General Description

... The MAX107 is a dual, 6-bit, analog-to-digital converter (ADC) designed to allow fast and precise digitizing of inphase (I) and quadrature (Q) baseband signals. The MAX107 converts the analog signals of both I and Q components to digital outputs at 400Msps while achieving a signal-to-noise ratio (SN ...

... The MAX107 is a dual, 6-bit, analog-to-digital converter (ADC) designed to allow fast and precise digitizing of inphase (I) and quadrature (Q) baseband signals. The MAX107 converts the analog signals of both I and Q components to digital outputs at 400Msps while achieving a signal-to-noise ratio (SN ...

docx

... The standard deviation, in volts, of a white Gaussian random process, which is to be added by the EDA tool to the signal measured at the sampling latch of a receiver. Usage Rules: If Rx_Noise is Usage Out, then the EDA tool shall use the value returned by Rx AMI_Init if Rx AMI_GetWave is not used. I ...

... The standard deviation, in volts, of a white Gaussian random process, which is to be added by the EDA tool to the signal measured at the sampling latch of a receiver. Usage Rules: If Rx_Noise is Usage Out, then the EDA tool shall use the value returned by Rx AMI_Init if Rx AMI_GetWave is not used. I ...

Optimality of Walrand-Varaiya Type Policies and Markov Sources

... 3. Joint source and channel coding, which occurs when the first two problems are examined together, is the process of finding one method that both compresses the source messages and adds redundancy to protect the message being transmitted across the channel. This thesis focuses on the source coding ...

... 3. Joint source and channel coding, which occurs when the first two problems are examined together, is the process of finding one method that both compresses the source messages and adds redundancy to protect the message being transmitted across the channel. This thesis focuses on the source coding ...

1 Abstract - glast lat

... The rest of the amplifier can be expected to add about another 20% of noise, so the measured ENC values at the shaper output are reasonable. As seen in Table 1, the simulated ENC is about 40% greater than the measured. This discrepancy is puzzling, as the difference in integration times can only exp ...

... The rest of the amplifier can be expected to add about another 20% of noise, so the measured ENC values at the shaper output are reasonable. As seen in Table 1, the simulated ENC is about 40% greater than the measured. This discrepancy is puzzling, as the difference in integration times can only exp ...

Integrated Circuit Design of Sigma-Delta Modulator for

... The design of a sigma-delta modulator as part of an analog-to-digital converter for a monolithic electric energy measurement system is presented. The main requirements such applications are a resolution of 16 bits and a bandwidth ranging from 40 Hz to 2 KHz. The design was optimized at system level ...

... The design of a sigma-delta modulator as part of an analog-to-digital converter for a monolithic electric energy measurement system is presented. The main requirements such applications are a resolution of 16 bits and a bandwidth ranging from 40 Hz to 2 KHz. The design was optimized at system level ...

Lecture 03

... Other calculations for amplitudes, voltages, currents, and so forth are equivalent. For a voltage signal, for instance, the ratio of RMS voltages is equivalent to the power ratio: ...

... Other calculations for amplitudes, voltages, currents, and so forth are equivalent. For a voltage signal, for instance, the ratio of RMS voltages is equivalent to the power ratio: ...

Quantization (signal processing)

Quantization, in mathematics and digital signal processing, is the process of mapping a large set of input values to a (countable) smaller set. Rounding and truncation are typical examples of quantization processes. Quantization is involved to some degree in nearly all digital signal processing, as the process of representing a signal in digital form ordinarily involves rounding. Quantization also forms the core of essentially all lossy compression algorithms. The difference between an input value and its quantized value (such as round-off error) is referred to as quantization error. A device or algorithmic function that performs quantization is called a quantizer. An analog-to-digital converter is an example of a quantizer.