* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download AN100 An overview of data converters

Pulse-width modulation wikipedia , lookup

Signal-flow graph wikipedia , lookup

Linear time-invariant theory wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Quantization (signal processing) wikipedia , lookup

Control system wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Two-port network wikipedia , lookup

Power electronics wikipedia , lookup

Television standards conversion wikipedia , lookup

Buck converter wikipedia , lookup

Oscilloscope history wikipedia , lookup

Schmitt trigger wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Integrating ADC wikipedia , lookup

Switched-mode power supply wikipedia , lookup

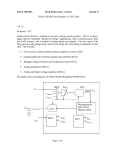

LINEAR PRODUCTS AN100 An overview of data converters December 1991 Philips Semiconductors Philips Semiconductors Application note An overview of data converters AN100 INTRODUCTION Data Transmission • Modem transmitter • Differential line driver • Party line multiplexing of analog signals • Multilevel 2-wire data transmission • Secure communications (constant power dissipation) Large systems are comprised of many different subsystems, all of which must interface to complete the system. All types of circuits, including linear, digital and discrete, are often used in the subsystems. Interface circuits provide the necessary function of tying the parts of a system together. These circuits are usually not purely linear or digital but contain both types of circuit functions. For instance, sense amplifiers are designed for interface between low level memory outputs and bipolar levels, while differential comparators are designed for interface between analog systems and logic systems. Control Systems • Reference level generator for set-point controllers • Positive peak detector • Negative peak detector • Disc drive head positioner • Microfilm head positioner CONVERTERS Digital communications, digital instruments and displays have created a demand for low cost reliable converters. Key factors in this demand are: • The need to communicate with digital computers and equipment Audio Systems for processing and storage of analog signals. • Digital AVC and reverberation • Music distribution • Organ tone generator • Audio tracking A/D • Speech compression and expansion • Audio digitizing and decoding • Severe limitations encountered in reliable analog data transmission over any considerable distance. • The need for more easily readable displays. General application areas for converters include: Data processing, data transmission, graphics and displays, audio systems, control systems and arithmetic operations. SPECIFIC APPLICATIONS Test Systems • Transistor tester (Force IB and IC) • Resistor matching • Programmable power supplies • Programmable pulse generators • Programmable current source • Function generators (ROM drive) DIGITAL WORD INPUT REF NOTES: Output = Ref. x digital word Output Ref. x Arithmetic Operations • Analog division by a digital word • Analog quotient of 2 digital words • Analog product of 2 digital words – squaring • Addition and subtraction with analog output • Magnitude comparison of 2 digital words • Digital quotient of 2 analog variables • Arithmetic operations with words from different logic families B1 2 B2 4 BN 2N SL00665 Figure 1. Conversion of a Digitally Coded Signal Input Into an Analog Signal Output –VREF I0 I4 8R I3 4R I2 2R I1 R RF – + Graphics and Displays • Polar-to-rectangular conversion • CRT character generation • Chart recorder driver • CRT displays 1991 Dec ANALOG OUTPUT D/A VOUT SL00666 Figure 2. Binary-Weighted Ladder Employing Voltage Switching 2 Philips Semiconductors Application note An overview of data converters AN100 transients in nodal parasite capacitances (See Figure 3). DAC Building Blocks The actual implementation of a D/A system contains four separate parts: A reference quantity; a set of binary switches to simulate binary coefficients B1 . . . BN; a weighting network; and an output summing means. KEY SPECIFICATIONS Speed ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ The conversion process should represent the input signal with the highest fidelity and minimal lag in time (real-time applications). IOUT EO 10 –VBIAS 8 6 I1 I2 2R 2R 2R I 4 I3 4 I4 2R 2 R R DIGITAL INPUT R IREF 000 001 E V– NOTE: I OUT I ∆K REF x b1 b2 2 b3 4 b4 8 010 011 100 101 110 111 SL00670 Figure 6. Gain Error SL00667 Figure 3. R-2R Ladder Network Employing Current Switching F.S. ANALOG OUTPUT IDEAL Binary-Weighted Ladder Employing Voltage Switching LINEARITY ERROR The disadvantages of a binary-weighted ladder employing voltage switching include: a wide range of resistor values which are used in weighting the network, and nodal capacitances which are charged/discharged during conversion (See Figure 2). NON–IDEAL 0 0 0 EO 0 0 1 0 1 0 0 1 1 1 0 0 1 0 0 1 1 0 1 1 1 DIGITAL INPUT SL00671 Figure 7. Relative Accuracy 1 LIMIT Settling Time Settling time is a measure of a converter’s speed and is defined as the elapsed time after a code transition for DAC output to reach final value within specified limits, usually ± LSB (See Figure 4). t 0 ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ ÉÉÉÉÉÉÉÉ SETTLING TIME Errors Offset Error – The output current or voltage of a DAC with zero code input. (See Figure 5). Offset can and usually is trimmed to zero with an offset zero adjust circuit. SL00668 Figure 4. Settling Time 10 8 6 5 4 EO Gain Error – Deviation in output voltage from correct level when the input calls for a full-scale output. This error may be trimmed to zero (See Figure 6). Relative Accuracy – The maximum deviation of the DAC output relative to an ideal straight line drawn from zero scale to full-scale (See Figure 7). ∆ EO ALL O’s ∆ O 0 000 001 010 011 100 101 110 111 Differential Non-Linearity – Incremental error from any ideal LSB analog output change when the digital input is changed 1 LSB (See Figure 9). DIGITAL INPUT E Monotonicity – As the input code is incremented from one code to the next in sequence, the analog output will either increase or remain constant (See Figure 9). SL00669 Figure 5. Offset Error Stability R-2R Ladder Network Employing Current Switching Stability is a measure of the independence of converter parameters with respect to variations in external conditions such as temperature and supply voltage. The advantages of this type of network include: no need for a wide range of resistor values, and current switching eliminates 1991 Dec 3 Philips Semiconductors Application note An overview of data converters AN100 Temperature Coefficient – The effects of temperature changes of the output. Specified as % full-scale change per degree C. ANALOG OUTPUT Supply Rejection – Ability to resist changes in the output with supply changes, specified as % full-scale change per volt of supply change. STEP SIZE ERROR 0 0 0 0 0 1 0 1 0 DIFFERENTIAL NON–LINEAR DIGITAL 0 1 1 1 1 INPUT 1 0 0 1 1 1 0 1 0 1 Long Term Stability – Measure of how stable the output is over a long period of time. SL00672 Figure 8. Differential Non-Linearity A/D CONVERTER CIRCUITS FS Analog-to-Digital conversion schemes generally fall into one of three categories: ANALOG OUTPUT 1/2 LSB DIFF NON–LINEAR 11/2 LSB 1/2 LSB 1. Feedback • Counting • Tracking (up-down) • Successive approximation 11/2 LSB 11/2 LSB DIFF 2. Integrating • Single slope • Dual slope • Triple slope 000 001 010 011 100 101 110 111 DIGITAL CODE SL00673 3. Parallel (Flash) Figure 9. Non-Monotonic (Must be > ± 1/2 LSB Non-Linear) INPUT REF COMPARATOR N–BIT DAC – + MSB n n OUTPUT BUFFER CONVERSION COMPLETE LSB START CONTROL LOGIC SAR CLOCK SL00674 Figure 10. Block Diagram of a Successive Approximation A/D Converter DAC output, the MSB is left high and the next bit is set. The input is The type of converter chosen for a given application depends upon again compared with the DAC output and the second bit cleared or many things; the accuracy required, the conversion speed left high, based on the same criteria as for the MSB. This process necessary, the necessary immunity to noise, and cost are some of continues until all bits have been determined. these considerations. The analog input should not change appreciably during the conversion time. If it did change during this time, the converted output would not be a true indication of the analog input. For this reason, it is common practice to use a sample-and-hold circuit at the converter analog input to hold the input value constant during the conversion process. A sample-and-hold circuit is not necessary if the signal at the input of the converter varies slowly enough and has a noise level low enough so that the input will not change a significant amount during the conversion. The allowable input The successive approximation technique is the one most widely used, mainly because of its excellent tradeoffs in resolution, speed, accuracy, and cost. Figure 10 shows a simplified block diagram of a successive approximation A/D converter. Upon receiving the start signal, the successive approximation register (SAR) is cleared and the most significant bit (MSB) of that register is set. The SAR output is connected to the input of the DAC, the output of which is compared with the unknown input. If the input is less than the DAC output, the MSB is cleared and the next bit is set; if the input is greater than the 1991 Dec 4 Philips Semiconductors Application note An overview of data converters AN100 change during this conversion is generally accepted as the value of LSB (for n-bit accuracy). Gain Error Accuracy and speed are determined primarily by the properties of the DAC and the comparator. Linearity is determined primarily by the linearity of the DAC. If the DAC is non-monotonic, one or more codes will be missing from the A/D converter’s output range. Relative Accuracy A Gain Error is shown in Figure 14. Relative Accuracy is the deviation of an actual bit transition from the ideal transition value at any level over the range of the ADC (% FS). See Figure 15. Figure 11 is the transfer function of a 3-bit binary coded A/D converter with a 0 to +10V input range. A 3-bit ADC is shown for simplicity, but the principle applies to ADCs of any resolution. Note that there is a LSB offset at the input such that the first count occurs when the input is equal to LSB. The center of the range for the first step occurs, therefore, when the input is equal to the value of one LSB, and the error at the switch point is limited to LSB. This error is known as the quantization error as it is derived from the smallest input quantity that can be resolved. If an ADC has a specified error of LSB maximum, this means that any transition point can be as far as LSB from where it should be. 111 OUTPUT CODE 110 101 100 011 010 • Analog input signal range and resolution required • Linearity requirement and stability • Conversion speed required • Monotonicity requirement: Can missing codes be tolerated? • Character of input signal: Is it noisy, sampled, filtered, slowly 8.75 10.00 7.50 6.25 5.00 INPUT VOLTAGE SL00675 Figure 11. Transfer Function of an Ideal 3-bit ADC With a 0 to 10V Input Range 111 110 101 ANALOG OUTPUT 100 011 010 001 000 varying? • Transfer characteristics (type of coding) V(1/2 LSB) A/D CONVERTER TERMS + 1/2 LSB IDEAL TRANSFER FUNCTION 10V – V (LSB) EIN 1.25 2.5 3.75 5.06.25 7.5 8.75 10 ANALOG INPUT ERROR FUNCTION Resolution Resolution is the input change required to increment the output between the two adjacent codes. This term also refers to the number of bits in the output word and, hence, the number of discrete output codes the input analog signal can be broken into. Expressed in “bits” resolution. – 1/2 LSB Figure 12. Quantizing Errors Transfer Characteristic The Transfer Characteristic is the relationship of the output digital word (code) to the input analog signal, i.e., Binary, BCD. Conversion Speed The Conversion Speed is the speed at which an ADC can make repetitive data conversions. Quantizing Error Quantizing Error is an inherent error in the conversion process due to finite resolution (discrete output). See Figure 12. Offset Error An Offset Error is shown in Figure 13. 1991 Dec 3.75 CONSIDERATIONS FOR A/D CONVERTERS 2.50 1.25 001 5 SL00676 Philips Semiconductors Application note An overview of data converters AN100 111 111 DIGITAL 101 OUTPUT 100 IDEAL NON–IDEAL 110 OFFSET ERROR 110 DIGITAL OUTPUT F.S. L.S.B. 101 PERFECT ADC 100 011 011 ADC WITH OFFSET 010 010 001 001 1 2 3 E 4 5 6 7 8 INPUT 000 EIN 1 1/2 L.S.B. 9 2 3 4 5 6 7 IDEAL SL00677 INPUT LINEARITY PLUS QUANTIZATION ERRORS –L.S.B. Figure 13. Offset Error L.S.B. IDEAL PERFECT ADC HIGH GAIN E2 101 E1 DIGITAL 100 OUTPUT 011 INPUT LOW GAIN LINEARITY ERROR –L.S.B. SL00679 Figure 15. Relative Accuracy 010 001 INPUT VOLTAGE EIN 000 111 1 2 3 4 5 6 7 8 9 10 110 101 DIGITAL 100 OUTPUT 011 ANALOG INPUT HIGH GAIN E + 1 LSB ERROR FUNCTION 10 –L.S.B. EIN 110 9 ERROR ANALOG INPUT + 1 LSB ERROR FUNCTION – 1 LSB 111 8 PERFECT ADC E1 E2 – 1 LSB 010 001 EIN 1 2 3 4 5 6 7 8 9 10 ANALOG INPUT (SHOWS A MISSING CODE AT 101) EIN SL00680 Figure 16. Missing Codes LOW GAIN Monotonicity SL00678 Hysteresis Error Monotonicity is when the output code either increases or remains the same for increasing analog input signals. The opposite is true in the reverse direction. A Hysteresis Error is the code transition voltage dependence relative to the direction from which the transition is approached. Missing Codes Figure 14. Gain Error 1991 Dec A Missing Code is a code combination that is skipped. See Figure 16. 6