DYNAMIC LOGIC

... The first gate in the chain needs a foot switch Precharge is rippling – short-circuit current A solution is to delay the clock for each stage EE415 VLSI Design ...

... The first gate in the chain needs a foot switch Precharge is rippling – short-circuit current A solution is to delay the clock for each stage EE415 VLSI Design ...

Design of Signed Multiplier using T-Flip Flop

... vital role when compared to the critical arithmetic functional units. The performance of the multipliers depends on the throughput and the variable latency. The negative bias instability effect of the pMOS transistor will increase the threshold voltage and it reduces the speed. Similarly the positiv ...

... vital role when compared to the critical arithmetic functional units. The performance of the multipliers depends on the throughput and the variable latency. The negative bias instability effect of the pMOS transistor will increase the threshold voltage and it reduces the speed. Similarly the positiv ...

A LOW POWER AND FAST CMOS ARITHMETIC LOGIC UNIT NUR

... One of the important parts of a digital computer is an arithmetic logic unit (ALU). ALU is designed to do the arithmetic and logic operations, including bit shifting operations which are the basic processes that need to be done for almost any data that is being processed by central processing unit ( ...

... One of the important parts of a digital computer is an arithmetic logic unit (ALU). ALU is designed to do the arithmetic and logic operations, including bit shifting operations which are the basic processes that need to be done for almost any data that is being processed by central processing unit ( ...

CMOS VLSI Design CMOS VLSI Design 4th Ed.

... discharged, it cannot be charged again until the next precharge operation. Inputs to the gate can make at most one transition during evaluation. Output can be in the high impedance state during and after evaluation (PDN off), state is stored on CL ...

... discharged, it cannot be charged again until the next precharge operation. Inputs to the gate can make at most one transition during evaluation. Output can be in the high impedance state during and after evaluation (PDN off), state is stored on CL ...

11sm04-lin.pdf

... input file to the numerical simulator is generated to contain all the simulation points, and two dimensional simulations are performed in batch-mode using a numerically based extractor [23] to evaluate the unit length capacitance and resistance values. The numerical data are then fitted to an analyt ...

... input file to the numerical simulator is generated to contain all the simulation points, and two dimensional simulations are performed in batch-mode using a numerically based extractor [23] to evaluate the unit length capacitance and resistance values. The numerical data are then fitted to an analyt ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... Economist designed a netruly full adder quaternary circuit pattern 3 power provide lines and multi-Vt transistors .Ricardo has designed quaternary device (MUX) 4:1 with 4quaternary inputs and one quaternary output and used this MUX as a building block to construct full adder projected technique bles ...

... Economist designed a netruly full adder quaternary circuit pattern 3 power provide lines and multi-Vt transistors .Ricardo has designed quaternary device (MUX) 4:1 with 4quaternary inputs and one quaternary output and used this MUX as a building block to construct full adder projected technique bles ...

TUTORIAL CADENCE DESIGN ENVIRONMENT

... support all the stages of IC design and verification from a single environment. These tools are completely general, supporting different fabrication technologies. When a particular technology is selected, a set of configuration and technology-related files are employed for customizing the Cadence en ...

... support all the stages of IC design and verification from a single environment. These tools are completely general, supporting different fabrication technologies. When a particular technology is selected, a set of configuration and technology-related files are employed for customizing the Cadence en ...

Xcell27

... optimized to allow minimal interconnect delays; this routing is faster and more predictable than that of non-segmented architectures. Vectorbased routing results in short, predictable delays that are not sensitive to minor changes in placement. This allows synthesis tools to ...

... optimized to allow minimal interconnect delays; this routing is faster and more predictable than that of non-segmented architectures. Vectorbased routing results in short, predictable delays that are not sensitive to minor changes in placement. This allows synthesis tools to ...

Qucs Help Documentation

... window opens and a sliding bar reports simulation progress. Normally, all this happens so fast that you only see a short flickering on the PC display (this depends on the speed of your PC). After finishing a simulation successfully Qucs opens a data display window. This replaces the schematic entry ...

... window opens and a sliding bar reports simulation progress. Normally, all this happens so fast that you only see a short flickering on the PC display (this depends on the speed of your PC). After finishing a simulation successfully Qucs opens a data display window. This replaces the schematic entry ...

Chap007-2011

... Introduce CMOS logic concepts Explore the voltage transfer characteristics of CMOS inverters Learn to design basic and complex CMOS logic gates Discuss the static and dynamic power in CMOS logic Present expressions for dynamic performance of CMOS logic devices Present noise margins for CMOS logic In ...

... Introduce CMOS logic concepts Explore the voltage transfer characteristics of CMOS inverters Learn to design basic and complex CMOS logic gates Discuss the static and dynamic power in CMOS logic Present expressions for dynamic performance of CMOS logic devices Present noise margins for CMOS logic In ...

Chap006-2011

... Brief History of Digital Electronics • Digital electronics can be found in many applications in the form of microprocessors, microcontrollers, PCs, DSPs, and an uncountable number of other systems. • The design of digital circuits has progressed from resistortransistor logic (RTL) and diode-transis ...

... Brief History of Digital Electronics • Digital electronics can be found in many applications in the form of microprocessors, microcontrollers, PCs, DSPs, and an uncountable number of other systems. • The design of digital circuits has progressed from resistortransistor logic (RTL) and diode-transis ...

... Since the battery technology available does not advance at the same rate as the microelectronics technology, IC designers have encountered more constraints: high speed, small silicon area, and at the same time, low power dissipation. Hence, the research of establishing high performance adder cells i ...

Introduction to Embedded System Design Using Field

... Many people have contributed in the process of writing this text. First and foremost, I wish to thank my PhD supervisors Professor Pramod Agarwal and Professor M.K. Vasantha at IIT Roorkee, for the training they provided during my research. Lots of impetus for being steadfast in my resolve to finish ...

... Many people have contributed in the process of writing this text. First and foremost, I wish to thank my PhD supervisors Professor Pramod Agarwal and Professor M.K. Vasantha at IIT Roorkee, for the training they provided during my research. Lots of impetus for being steadfast in my resolve to finish ...

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

... leading alternative for standard voltage-mode style of digital systems. However, in a very typical binary system of numeration based mostly VLSI circuit regarding seventy p.c of chip space is occupied by interconnections that occupy an oversized portion of physical space even once it's not in use. t ...

... leading alternative for standard voltage-mode style of digital systems. However, in a very typical binary system of numeration based mostly VLSI circuit regarding seventy p.c of chip space is occupied by interconnections that occupy an oversized portion of physical space even once it's not in use. t ...

Circuit Pitfalls

... • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets real world ...

... • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets real world ...

Lecture 18

... • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets real world ...

... • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets real world ...

... B. P. Harish, Navakanta Bhat, and Mahesh B. Patil Abstract—A generalized methodology for modeling the effects of process variations on circuit delay performance is proposed by directly relating the variations in process parameters to variations in delay metric of a digital circuit. The 2-input NAND ...

Rosetta Demostrator Project MASC, Adelaide University

... Portions of this work are from the book, Digital Design: An Embedded Systems Approach Using VHDL, by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved. ...

... Portions of this work are from the book, Digital Design: An Embedded Systems Approach Using VHDL, by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved. ...

Design of a New External Signal Controlled Polymorphic

... combined to form a building block called polymorphic gates that changes its functionality as a response to controls such as temperature, power supply voltage (Vdd), light, an external signal, etc. For example, there is a logic gate that operates as AND when the temperature is 300 K and as OR when th ...

... combined to form a building block called polymorphic gates that changes its functionality as a response to controls such as temperature, power supply voltage (Vdd), light, an external signal, etc. For example, there is a logic gate that operates as AND when the temperature is 300 K and as OR when th ...

Answers

... 4. (10 points) Draw a logic circuit using the smallest possible number of simple gates (AND, OR and inverters, only) for the logic expression UX ′ + X(V + Z′) + (V′ + U)X′Z′. ...

... 4. (10 points) Draw a logic circuit using the smallest possible number of simple gates (AND, OR and inverters, only) for the logic expression UX ′ + X(V + Z′) + (V′ + U)X′Z′. ...

Practical statistical simulation for efficient circuit design

... parameters for the devices of the same type, say HBTs, of different size or geometries were not linked. As a result, it takes many parameters to vary each of these devices statistically on an individual basis, and some nonphysical statistical states can occur. A simulation approach based on individu ...

... parameters for the devices of the same type, say HBTs, of different size or geometries were not linked. As a result, it takes many parameters to vary each of these devices statistically on an individual basis, and some nonphysical statistical states can occur. A simulation approach based on individu ...

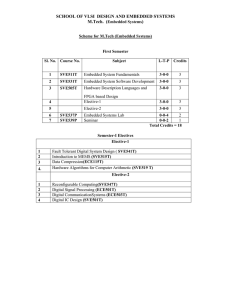

SCHOOL OF VLSI DESIGN AND EMBEDDED SYSTEMS

... SCHOOL OF VLSI DESIGN AND EMBEDDED SYSTEMS M.Tech. (Embedded Systems) ...

... SCHOOL OF VLSI DESIGN AND EMBEDDED SYSTEMS M.Tech. (Embedded Systems) ...

Anx 30 B - B.Sc. ECS _Col_ 08-09

... Paper VIII : Digital and Cellular Communications Pract. III Digital Electronics Lab. Pract. IV Radio, TV and Instrumentation Lab Allied : IV Object Oriented Programming using C++ ...

... Paper VIII : Digital and Cellular Communications Pract. III Digital Electronics Lab. Pract. IV Radio, TV and Instrumentation Lab Allied : IV Object Oriented Programming using C++ ...

0724.PSpice Tutorial for Customer - TI E2E Community

... with part symbol creation (from a schematic) 1. Now let’s assume that we don’t have THS1234.LIB netlist. Rather, we have a schematic view called THS1234 that consists of R, C and the port information. We then want to create a symbol from this schematic, place the symbol on a test bench and run simul ...

... with part symbol creation (from a schematic) 1. Now let’s assume that we don’t have THS1234.LIB netlist. Rather, we have a schematic view called THS1234 that consists of R, C and the port information. We then want to create a symbol from this schematic, place the symbol on a test bench and run simul ...