Timing Considerations with VHDL

... Timing issues are most important in circuits that involve long paths through combinational logic elements with registers at inputs and outputs of these paths. As an example, we will use the adder/subtractor circuit shown in Figure 1. It can add, subtract, and accumulate n-bit numbers using the 2’s c ...

... Timing issues are most important in circuits that involve long paths through combinational logic elements with registers at inputs and outputs of these paths. As an example, we will use the adder/subtractor circuit shown in Figure 1. It can add, subtract, and accumulate n-bit numbers using the 2’s c ...

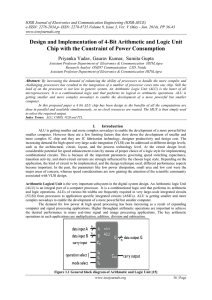

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

... to give us an idea of earlier work and shed light on different optimization techniques. Past work related to multiple-input floating gate CMOS applications has been reviewed to give us an idea about its operation, design and simulation issues. But et al [1] have designed a low power 10-transistor fu ...

... to give us an idea of earlier work and shed light on different optimization techniques. Past work related to multiple-input floating gate CMOS applications has been reviewed to give us an idea about its operation, design and simulation issues. But et al [1] have designed a low power 10-transistor fu ...

Features

... representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unl ...

... representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unl ...

Acrobat Distiller, Job 62 - Genetic Programming Inc.

... number of required mathematical functions does not warrant converting an analog signal into a digital signal, performing the mathematical function in the digital domain, and then converting the result back to the analog domain. The design of computational circuits is difficult even for mundane mathe ...

... number of required mathematical functions does not warrant converting an analog signal into a digital signal, performing the mathematical function in the digital domain, and then converting the result back to the analog domain. The design of computational circuits is difficult even for mundane mathe ...

2 CMOS VLSI Design

... Collisions with particles create electron-hole pairs in substrate – These carriers are collected on dynamic nodes, disturbing the voltage Minimize soft errors by having plenty of charge on dynamic nodes Tolerate errors through ECC (Error Correcting Code), redundancy CMOS VLSI Design ...

... Collisions with particles create electron-hole pairs in substrate – These carriers are collected on dynamic nodes, disturbing the voltage Minimize soft errors by having plenty of charge on dynamic nodes Tolerate errors through ECC (Error Correcting Code), redundancy CMOS VLSI Design ...

Analog Integrated Circuit Sizing and Layout Dependent Effects: A

... According to Kruiskamp and Leenaerts [1], circuit topology selection is to select device set out of hundreds of combinations. Each set behaves as one stage of the whole design at the schematic level. For instance, an operational amplifier (OPAMP) is composed of an input stage, a gain stage, and an o ...

... According to Kruiskamp and Leenaerts [1], circuit topology selection is to select device set out of hundreds of combinations. Each set behaves as one stage of the whole design at the schematic level. For instance, an operational amplifier (OPAMP) is composed of an input stage, a gain stage, and an o ...

PPT

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

PPT

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

PPT

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

... Gate array - regular patterns of gate transistors that can be used in many designs built into chip - only the interconnections between gates are specific to a design ...

Circuit Pitfalls

... Principle: Diffusion Input Noise Sensitivity – If D < -Vt, transmission gate turns on – Most likely because of power supply noise or coupling on D Solution: Buffer D locally ...

... Principle: Diffusion Input Noise Sensitivity – If D < -Vt, transmission gate turns on – Most likely because of power supply noise or coupling on D Solution: Buffer D locally ...

Lecture 16: Pitfalls & Reliability

... Principle: Diffusion Input Noise Sensitivity – If D < -Vt, transmission gate turns on – Most likely because of power supply noise or coupling on D Solution: Buffer D locally ...

... Principle: Diffusion Input Noise Sensitivity – If D < -Vt, transmission gate turns on – Most likely because of power supply noise or coupling on D Solution: Buffer D locally ...

High-Speed Board Design Tutorial What Is High Speed? High-Speed Board Design Tutorial

... − Waves Reflect Unless Terminated − Voltage Is Superposition of Waves ...

... − Waves Reflect Unless Terminated − Voltage Is Superposition of Waves ...

PPT - Electrical and Computer Engineering

... Fan-in – the number of inputs available on a gate Fan-out – the number of standard loads driven by a gate output Logic Levels – the signal value ranges for 1 and 0 on the inputs and 1 and 0 on the outputs (see Figure 1-1) Noise Margin – the maximum external noise voltage superimposed on a normal inp ...

... Fan-in – the number of inputs available on a gate Fan-out – the number of standard loads driven by a gate output Logic Levels – the signal value ranges for 1 and 0 on the inputs and 1 and 0 on the outputs (see Figure 1-1) Noise Margin – the maximum external noise voltage superimposed on a normal inp ...

COMPUTER AIDED DESIGN OF ELECTRONIC DEVICES

... Computer-aided design (CAD) is the use of computer systems to assist in the creation, modification, analysis, or optimization of a design. CAD software is used to increase the productivity of the designer, improve the quality of design, improve communications through documentation, and to create a d ...

... Computer-aided design (CAD) is the use of computer systems to assist in the creation, modification, analysis, or optimization of a design. CAD software is used to increase the productivity of the designer, improve the quality of design, improve communications through documentation, and to create a d ...

CPLD Basics

... Easier to visualize and understand a circuit and its logic flow. Easier for some specific, moderately complex logic such as shift registers and counters. Easy to re-create an existing or previously designed logic diagram directly as a logic diagram in the CPLD software. User can create new g ...

... Easier to visualize and understand a circuit and its logic flow. Easier for some specific, moderately complex logic such as shift registers and counters. Easy to re-create an existing or previously designed logic diagram directly as a logic diagram in the CPLD software. User can create new g ...

week6

... The RASSP E&F Program welcomes and encourages any feedback that you may have including any changes that you may make to improve or update the material. You can contact us at [email protected] or http://rassp.scra.org/module-request/FEEDBACK/feedback-on-modules.html Modern VLSI Design 3e: Chapt ...

... The RASSP E&F Program welcomes and encourages any feedback that you may have including any changes that you may make to improve or update the material. You can contact us at [email protected] or http://rassp.scra.org/module-request/FEEDBACK/feedback-on-modules.html Modern VLSI Design 3e: Chapt ...

A Novel Table-Based Approach for Design of FinFET Circuits

... The use of LUTs to simulate circuits was first proposed by Chawla et al. [1], where the goal was to obtain timing information in digital circuits. Shima et al. [2] developed a 3-D LUT approach for simulating analog circuits. The use of splines that guarantee monotonic interpolated data for table loo ...

... The use of LUTs to simulate circuits was first proposed by Chawla et al. [1], where the goal was to obtain timing information in digital circuits. Shima et al. [2] developed a 3-D LUT approach for simulating analog circuits. The use of splines that guarantee monotonic interpolated data for table loo ...

University Bremerhaven Embedded System Design Example (Class

... Processing System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

... Processing System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

An overview of FPGAs: the solution to countless design

... Density is a factor as designers don't want to overspecify and thus pay for more FPGA gates than needed, but also want to allow some "insurance" in case the project needs to expand beyond the original estimate, or want to use the same FPGA across multiple end products. Speed is a parameter which ind ...

... Density is a factor as designers don't want to overspecify and thus pay for more FPGA gates than needed, but also want to allow some "insurance" in case the project needs to expand beyond the original estimate, or want to use the same FPGA across multiple end products. Speed is a parameter which ind ...

S. Hassoun and D. Marculescu, “Towards GALS Design

... Hassoun’s interests focus mainly on: Synthesis (subsections R1-R7 below), Timing Analysis (R8-R9), and Physical Design (R10). Of special interest is the synergy between these areas, such as optimal pipelining when constructing physical routes, and timing-driven synthesis. Other interests include emu ...

... Hassoun’s interests focus mainly on: Synthesis (subsections R1-R7 below), Timing Analysis (R8-R9), and Physical Design (R10). Of special interest is the synergy between these areas, such as optimal pipelining when constructing physical routes, and timing-driven synthesis. Other interests include emu ...

EECS 420 – Electromagnetics II Lab

... dialogue box circled in blue (solid line). Place the following components for your simulation: Syntax of the following list is “Library: Part Type (part name)” a. Need two “Lumped-Components: Resistor (R)” – should have already placed these in the previous step. b. Need one “Sources-Freq Domain: DC ...

... dialogue box circled in blue (solid line). Place the following components for your simulation: Syntax of the following list is “Library: Part Type (part name)” a. Need two “Lumped-Components: Resistor (R)” – should have already placed these in the previous step. b. Need one “Sources-Freq Domain: DC ...

EE414 Lecture Notes (electronic)

... - once a design is defined at the gate level, there are many options to implement the design - each option is an engineering trade-off between 1) Cost 2) Schedule 3) Performance ...

... - once a design is defined at the gate level, there are many options to implement the design - each option is an engineering trade-off between 1) Cost 2) Schedule 3) Performance ...

A Parallel Circuit Simulator for Iterative Power Grids Optimization

... on one VLSI chip. However, the power supply voltage is lowering along with shrinking of the device size. On the other hand, the power consumption is increasing because the number of transistors and the clock frequency increase. Therefore, IR-drop and electro-migration (EM) in the power grids make fu ...

... on one VLSI chip. However, the power supply voltage is lowering along with shrinking of the device size. On the other hand, the power consumption is increasing because the number of transistors and the clock frequency increase. Therefore, IR-drop and electro-migration (EM) in the power grids make fu ...

Microwind - Saraju P. Mohanty

... • Microwind is a tool for designing and simulating circuits at layout level. The tool features full editing facilities (copy, cut, past, duplicate, move), various views (MOS characteristics, 2D cross section, 3D process viewer), and an analog simulator. • DSCH is a software for logic design. Based o ...

... • Microwind is a tool for designing and simulating circuits at layout level. The tool features full editing facilities (copy, cut, past, duplicate, move), various views (MOS characteristics, 2D cross section, 3D process viewer), and an analog simulator. • DSCH is a software for logic design. Based o ...

What is a chip?

... FPGA is. The layout of the internal chip constructs are fixed and cannot be modified without a “re-spin” of the ASIC. This makes ASICs much less flexible than FPGAs. ASICs are very dense chips, which typically translates to high scalability with less real-estate requirement on a line card. While ASI ...

... FPGA is. The layout of the internal chip constructs are fixed and cannot be modified without a “re-spin” of the ASIC. This makes ASICs much less flexible than FPGAs. ASICs are very dense chips, which typically translates to high scalability with less real-estate requirement on a line card. While ASI ...