Performance Verification of Low Noise, Low Dropout Regulators

... The low noise LDOs use Figure A1’s scheme, with special attention to minimizing noise transmission within the loop and from unregulated input. The internal voltage reference’s noise is filtered by CBYP. Additionally, the error amplifier’s frequency response is shaped to minimize noise contribution w ...

... The low noise LDOs use Figure A1’s scheme, with special attention to minimizing noise transmission within the loop and from unregulated input. The internal voltage reference’s noise is filtered by CBYP. Additionally, the error amplifier’s frequency response is shaped to minimize noise contribution w ...

TPS40060 Wide Input Synchronous Buck

... Soft-start programming pin. A capacitor connected from this pin to ground programs the soft-start time. The capacitor is charged with an internal current source of 2.3 µA. The resulting voltage ramp on the SS pin is used as a second non-inverting input to the error amplifier. The output voltage begi ...

... Soft-start programming pin. A capacitor connected from this pin to ground programs the soft-start time. The capacitor is charged with an internal current source of 2.3 µA. The resulting voltage ramp on the SS pin is used as a second non-inverting input to the error amplifier. The output voltage begi ...

MAX1809 3A, 1MHz, DDR Memory Termination Supply General Description Features

... The MAX1809 uses a unique current-mode, constantoff-time, PWM control scheme that allows the output to source or sink current. This feature allows energy to return to the input power supply that otherwise would be wasted. The programmable constant-off-time architecture sets switching frequencies up ...

... The MAX1809 uses a unique current-mode, constantoff-time, PWM control scheme that allows the output to source or sink current. This feature allows energy to return to the input power supply that otherwise would be wasted. The programmable constant-off-time architecture sets switching frequencies up ...

2A SIMPLE SWITCHER Power Module w/20V Max Input Voltage for

... Such as Input UVLO and Output Short Circuit Single Exposed Pad and Standard Pinout for Easy Mounting and Manufacturing Fast Transient Response for FPGAs and ASICs Low Output Voltage Ripple Pin-to-Pin Compatible With Family Devices: – LMZ14203EXT/2EXT/1EXT (42-V Maximum 3 A, 2 A, 1 A) – LMZ14203/2/1 ...

... Such as Input UVLO and Output Short Circuit Single Exposed Pad and Standard Pinout for Easy Mounting and Manufacturing Fast Transient Response for FPGAs and ASICs Low Output Voltage Ripple Pin-to-Pin Compatible With Family Devices: – LMZ14203EXT/2EXT/1EXT (42-V Maximum 3 A, 2 A, 1 A) – LMZ14203/2/1 ...

BUF602 数据资料 dataSheet 下载

... (1000MHz) and high slew rate (8000V/µs) make it ideal for buffering very high-frequency signals. For AC-coupled applications, an optional mid-point reference (VREF) is provided, reducing the number of external components required and the necessary supply current to provide that reference. ...

... (1000MHz) and high slew rate (8000V/µs) make it ideal for buffering very high-frequency signals. For AC-coupled applications, an optional mid-point reference (VREF) is provided, reducing the number of external components required and the necessary supply current to provide that reference. ...

SN74LVC1404 OSCILLATOR DRIVER FOR CRYSTAL OSCILLATOR OR CERAMIC RESONATOR FEATURES

... After the selection of proper component values, the oscillator circuit should be tested, using these components, to ensure that the oscillator circuit shows required performance over the recommended operating conditions. • Without a crystal, the oscillator circuit should not oscillate. To check this ...

... After the selection of proper component values, the oscillator circuit should be tested, using these components, to ensure that the oscillator circuit shows required performance over the recommended operating conditions. • Without a crystal, the oscillator circuit should not oscillate. To check this ...

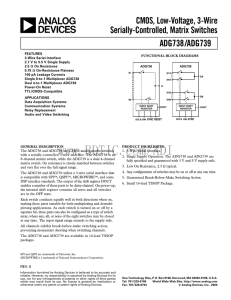

a CMOS, Low-Voltage, 3-Wire Serially-Controlled, Matrix Switches ADG738/ADG739

... 3. Low On Resistance, 2.5 Ω typical. 4. Any configuration of switches may be on or off at any one time. 5. Guaranteed Break-Before-Make Switching Action. 6. Small 16-lead TSSOP Package. ...

... 3. Low On Resistance, 2.5 Ω typical. 4. Any configuration of switches may be on or off at any one time. 5. Guaranteed Break-Before-Make Switching Action. 6. Small 16-lead TSSOP Package. ...

Stability Analysis of a Matrix Converter Drive

... Therefore, the grid current (Is) is affected by input voltage (Vf) and the MC input current (Ii). The filter should eliminate the switching harmonics of Ii to increase the quality of the grid current. Fig. 8 shows the frequency response of the transfer function between the input and the grid current ...

... Therefore, the grid current (Is) is affected by input voltage (Vf) and the MC input current (Ii). The filter should eliminate the switching harmonics of Ii to increase the quality of the grid current. Fig. 8 shows the frequency response of the transfer function between the input and the grid current ...

Generation of Different Types of Voltage Sag Using Matlab/Simulink

... sags. The symmetrical component classification is more general and gives a direct link with measured voltages but is harder to understand and a translation to the ABC classification may be suitable for many applications. In addition, the ABC classification was developed to analyze the propagation of ...

... sags. The symmetrical component classification is more general and gives a direct link with measured voltages but is harder to understand and a translation to the ABC classification may be suitable for many applications. In addition, the ABC classification was developed to analyze the propagation of ...

PowerPoint-presentation

... A non periodic (varying) signal time domain is spread in the frequency domain. A completely random signal (white noise) have a uniform frequency spectra ...

... A non periodic (varying) signal time domain is spread in the frequency domain. A completely random signal (white noise) have a uniform frequency spectra ...

比较器系列ADCMP572 数据手册DataSheet 下载

... carefully selected for minimum inductance and ESR. Parasitic layout inductance should be avoided to maximize the effectiveness of the bypass at high frequencies. ...

... carefully selected for minimum inductance and ESR. Parasitic layout inductance should be avoided to maximize the effectiveness of the bypass at high frequencies. ...

UCC2818A-Q1 数据资料 dataSheet 下载

... Designed in Texas Instrument’s BiCMOS process, the UCC2818A offers new features such as lower start-up current, lower power dissipation, overvoltage protection, a shunt UVLO detect circuitry, a leading-edge modulation technique to reduce ripple current in the bulk capacitor and an improved, low-offs ...

... Designed in Texas Instrument’s BiCMOS process, the UCC2818A offers new features such as lower start-up current, lower power dissipation, overvoltage protection, a shunt UVLO detect circuitry, a leading-edge modulation technique to reduce ripple current in the bulk capacitor and an improved, low-offs ...

OPA684 Low-Power, Current Feedback OPERATIONAL AMPLIFIER With Disable FEATURES

... The OPA684 provides a new level of performance in low-power, wideband, current-feedback (CFB) amplifiers. This CFBplus amplifier is the first to use an internally closed-loop input buffer stage that enhances performance significantly over earlier low-power CFB amplifiers. While retaining the benefit ...

... The OPA684 provides a new level of performance in low-power, wideband, current-feedback (CFB) amplifiers. This CFBplus amplifier is the first to use an internally closed-loop input buffer stage that enhances performance significantly over earlier low-power CFB amplifiers. While retaining the benefit ...

ADG3123 数据手册DataSheet 下载

... Pin VSS set the logic levels available at the outputs on the Y side of the device. Pin VDDA and Pin VDDB set the high output level for Pin Y1 to Pin Y6 and for Pin Y7 to Pin Y8, respectively. The VSS pin sets the low output level for all channels. The ADG3123 can provide output voltages levels down ...

... Pin VSS set the logic levels available at the outputs on the Y side of the device. Pin VDDA and Pin VDDB set the high output level for Pin Y1 to Pin Y6 and for Pin Y7 to Pin Y8, respectively. The VSS pin sets the low output level for all channels. The ADG3123 can provide output voltages levels down ...

THS4509-Q1

... To allow for dc coupling to analog-to-digital converters (ADCs), its unique output common-mode control circuit maintains the output common-mode voltage within 3-mV offset (typ) from the set voltage, when set within 0.5 V of mid-supply, with less than 4-mV differential offset voltage. The common-mode ...

... To allow for dc coupling to analog-to-digital converters (ADCs), its unique output common-mode control circuit maintains the output common-mode voltage within 3-mV offset (typ) from the set voltage, when set within 0.5 V of mid-supply, with less than 4-mV differential offset voltage. The common-mode ...

LLC Half-Bridge Controller for Multi-String LED

... Gate drive outputs operate 180° out of phase with a fixed 500 ns of dead time. They typically drive either primary end of a gate drive transformer. At start-up or during a fault recovery, initiating the LLC converter begins with GD2 turning on first. ...

... Gate drive outputs operate 180° out of phase with a fixed 500 ns of dead time. They typically drive either primary end of a gate drive transformer. At start-up or during a fault recovery, initiating the LLC converter begins with GD2 turning on first. ...

low power folded cascode cmos operational amplifier with common

... circuits [9-10]. There are three techniques that have been used in implementing CMFB circuits [10] which are differential difference amplifier (DDA) CMFB, switch capacitor CMFB and resistor-averaged CMFB. For this op-amp architecture, the differential difference amplifier (DDA) CMFB technique is app ...

... circuits [9-10]. There are three techniques that have been used in implementing CMFB circuits [10] which are differential difference amplifier (DDA) CMFB, switch capacitor CMFB and resistor-averaged CMFB. For this op-amp architecture, the differential difference amplifier (DDA) CMFB technique is app ...

AD7688 数据手册DataSheet下载

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

MAX3157 High CMRR RS-485 Transceiver with ±50V Isolation General Description

... hybrid microcircuit. A single +5V supply on the logic side powers both sides of the interface, with external ±50V capacitors transferring power from the logic side to the isolated side. Each MAX3157 contains one transmitter and one receiver and is guaranteed to operate at data rates up to 250kbps. D ...

... hybrid microcircuit. A single +5V supply on the logic side powers both sides of the interface, with external ±50V capacitors transferring power from the logic side to the isolated side. Each MAX3157 contains one transmitter and one receiver and is guaranteed to operate at data rates up to 250kbps. D ...