CBC early test report - Mark Raymond

... Figure 3.1.3 shows a measurement of three of the bias generator voltage dependences on I2C register setting. VPC and VPLUS are implemented by mirroring a current into a resistor, and the voltage range covered is consistent with what is expected from simulation. VPAFB is not a simple voltage setting ...

... Figure 3.1.3 shows a measurement of three of the bias generator voltage dependences on I2C register setting. VPC and VPLUS are implemented by mirroring a current into a resistor, and the voltage range covered is consistent with what is expected from simulation. VPAFB is not a simple voltage setting ...

Bipolar +/-10V Analog Output from a Unipolar Voltage Output DAC

... errors that are contributed by the DAC8560. The DAC8560 is modeled by an ideal voltage source sweeping from 0 V to 2.50 V along with a non-inverting amplifier with gain to simulate the effects of the DAC8560 typical gain error of ±0.05% FSR. Additionally, a series voltage source of 5 mV is included ...

... errors that are contributed by the DAC8560. The DAC8560 is modeled by an ideal voltage source sweeping from 0 V to 2.50 V along with a non-inverting amplifier with gain to simulate the effects of the DAC8560 typical gain error of ±0.05% FSR. Additionally, a series voltage source of 5 mV is included ...

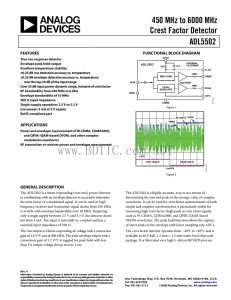

450 MHz to 6000 MHz Crest Factor Detector ADL5502

... Modulation Filter Pin. Connection for an external capacitor to lower the corner frequency of the modulation filter. Supply Voltage Pin. Operational range 2.5 V to 3.3 V. Signal Input Pin. Internally ac-coupled after internal termination resistance. Nominal 500 Ω input impedance. ...

... Modulation Filter Pin. Connection for an external capacitor to lower the corner frequency of the modulation filter. Supply Voltage Pin. Operational range 2.5 V to 3.3 V. Signal Input Pin. Internally ac-coupled after internal termination resistance. Nominal 500 Ω input impedance. ...

AD7787 数据手册DataSheet下载

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

AN-2093 LMZ23610/8/6 and LMZ22010/8/6

... Current sharing is easy to evaluate. The next steps should be implemented only while the power to the device is off. Select which board will be the master. This is usually the board closer to the load. Connect the master board as described above in Test Connections. Insert the slave board into the s ...

... Current sharing is easy to evaluate. The next steps should be implemented only while the power to the device is off. Select which board will be the master. This is usually the board closer to the load. Connect the master board as described above in Test Connections. Insert the slave board into the s ...

74LCX162374 Low Voltage 16-Bit D-Type Flip-Flop with 5V Tolerant Inputs and Outputs

... The LCX162374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte ...

... The LCX162374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte ...

4.5-V to 52-V Input, Current

... Minimum On-Time and Off-Time Considerations The TPS40210 has a minimum off time of approximately 200 ns and a minimum on time of 300 ns. These two constraints place limitations on the operating frequency that can be used for a given input-to-output conversion ratio. See Figure 3 for the maximum freq ...

... Minimum On-Time and Off-Time Considerations The TPS40210 has a minimum off time of approximately 200 ns and a minimum on time of 300 ns. These two constraints place limitations on the operating frequency that can be used for a given input-to-output conversion ratio. See Figure 3 for the maximum freq ...

HIGH-SPEED FULLY DIFFERENTIAL I/O AMPLIFIERS THS4120 THS4121 FEATURES

... Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS412x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacit ...

... Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS412x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacit ...

Operational Amplifiers

... Even though real op-amps deviate from these ideal conditions, the ideal op-amp rules are very useful and are used extensively in circuit design and analysis. In the following sections we will see how to use these rules and the typical errors associated with these assumptions. Note that when using th ...

... Even though real op-amps deviate from these ideal conditions, the ideal op-amp rules are very useful and are used extensively in circuit design and analysis. In the following sections we will see how to use these rules and the typical errors associated with these assumptions. Note that when using th ...

Installation Considerations for Multi

... motor output cables with substantial line to ground capacitance as shown in Fig. 3. This creates the potential for large zero sequence cable charging currents during switching instants of the VFD output waveform. Previous generation six step drive inverters used Bipolar Junction Transistor (BJT) sem ...

... motor output cables with substantial line to ground capacitance as shown in Fig. 3. This creates the potential for large zero sequence cable charging currents during switching instants of the VFD output waveform. Previous generation six step drive inverters used Bipolar Junction Transistor (BJT) sem ...

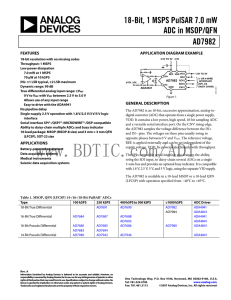

AD7982 数据手册DataSheet下载

... when CNV is low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input ...

... when CNV is low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input ...

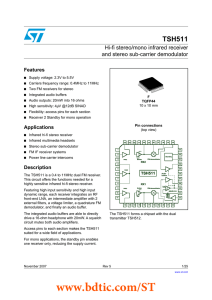

TSH511

... TSH511. The sensitive LNA, directly connected to the photo diode, does not require an external pre-amplifier. After filtering, the amplified signals are limited and demodulated with quadrature demodulators. The two integrated audio buffers directly drive the stereo headphones. The audio power reache ...

... TSH511. The sensitive LNA, directly connected to the photo diode, does not require an external pre-amplifier. After filtering, the amplified signals are limited and demodulated with quadrature demodulators. The two integrated audio buffers directly drive the stereo headphones. The audio power reache ...

Complex Waveforms

... In previous work, a.c. supplies have been assumed to be sinusoidal, this being a form of alternating quantity commonly encountered in electrical engineering. However, many supply waveforms are not sinusoidal. For example, sawtooth generators produce ramp waveforms, and rectangular waveforms may be p ...

... In previous work, a.c. supplies have been assumed to be sinusoidal, this being a form of alternating quantity commonly encountered in electrical engineering. However, many supply waveforms are not sinusoidal. For example, sawtooth generators produce ramp waveforms, and rectangular waveforms may be p ...

OPA2830

... The OPA2830 is a dual, low-power, single-supply, wideband, voltage-feedback amplifier designed to operate on a single +3V or +5V supply. Operation on ±5V or +10V supplies is also supported. The input range extends below ground and to within 1.8V of the positive supply. Using complementary common-emi ...

... The OPA2830 is a dual, low-power, single-supply, wideband, voltage-feedback amplifier designed to operate on a single +3V or +5V supply. Operation on ±5V or +10V supplies is also supported. The input range extends below ground and to within 1.8V of the positive supply. Using complementary common-emi ...

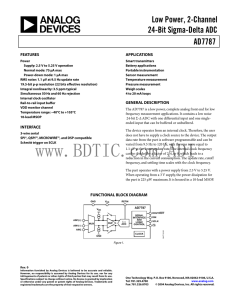

Low Power, Buffered 24-Bit Sigma-Delta ADC AD7791

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

Summer-students-2009-part1 - Indico

... Credits and sources of information I have “stolen” a lot from the previous summer student lectures from Christophe de la Taille and Jorgen Christiansen and from colleagues from the PH electronics group (PH-ESE) Useful and more complete information can be found in the following ...

... Credits and sources of information I have “stolen” a lot from the previous summer student lectures from Christophe de la Taille and Jorgen Christiansen and from colleagues from the PH electronics group (PH-ESE) Useful and more complete information can be found in the following ...

Low-Cost, Integrated, Analog Front-End for Weigh

... chains share a 16-bit, delta-sigma converter that operates at a data rate of up to 860 SPS. This device also integrates a reference and a low-dropout regulator (LDO) that generates a 1.7-V supply that can be used as the excitation source for the load cells, thus simplifying ratiometric measurements. ...

... chains share a 16-bit, delta-sigma converter that operates at a data rate of up to 860 SPS. This device also integrates a reference and a low-dropout regulator (LDO) that generates a 1.7-V supply that can be used as the excitation source for the load cells, thus simplifying ratiometric measurements. ...