AD9751 数据手册DataSheet 下载

... The AD9751 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

... The AD9751 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

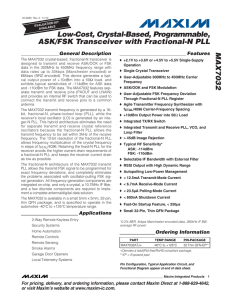

MAX7032 Low-Cost, Crystal-Based, Programmable, ASK/FSK Transceiver with Fractional-N PLL General Description

... data in the 300MHz to 450MHz frequency range with data rates up to 33kbps (Manchester encoded) or 66kbps (NRZ encoded). This device generates a typical output power of +10dBm into a 50Ω load, and exhibits typical sensitivities of -114dBm for ASK data and -110dBm for FSK data. The MAX7032 features se ...

... data in the 300MHz to 450MHz frequency range with data rates up to 33kbps (Manchester encoded) or 66kbps (NRZ encoded). This device generates a typical output power of +10dBm into a 50Ω load, and exhibits typical sensitivities of -114dBm for ASK data and -110dBm for FSK data. The MAX7032 features se ...

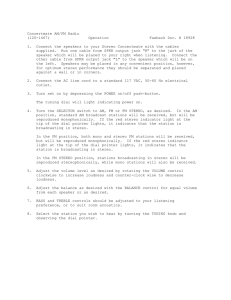

HMC839LP6CE - Analog Devices

... The HMC839LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL) with an Integrated Voltage Controlled Oscillator (VCO). The PLL consists of an integrated low noise VCO with a tri-band output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector ...

... The HMC839LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL) with an Integrated Voltage Controlled Oscillator (VCO). The PLL consists of an integrated low noise VCO with a tri-band output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector ...

Joint Identification of Optical and Electro

... as their frequency responses are design parameters, so that the gain in dynamics can be traded off with control amplitudes. Mathematical details of optimal equalizer design will be described elsewhere. Fig. 5 shows the resulting combined impulse response of equalizers and galvos (red), which are the ...

... as their frequency responses are design parameters, so that the gain in dynamics can be traded off with control amplitudes. Mathematical details of optimal equalizer design will be described elsewhere. Fig. 5 shows the resulting combined impulse response of equalizers and galvos (red), which are the ...

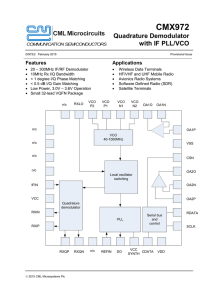

Document

... The AD536A is available in two accuracy grades (J, K) for commercial temperature range (0°C to +70°C) applications, and one grade (S) rated for the –55°C to +125°C extended range. The AD536AK offers a maximum total error of ± 2 mV ± 0.2% of reading, and the AD536AJ and AD536AS have maximum errors of ...

... The AD536A is available in two accuracy grades (J, K) for commercial temperature range (0°C to +70°C) applications, and one grade (S) rated for the –55°C to +125°C extended range. The AD536AK offers a maximum total error of ± 2 mV ± 0.2% of reading, and the AD536AJ and AD536AS have maximum errors of ...

ADS1253 数据资料 dataSheet 下载

... The digital filter of the ADS1253, referred to as a sinc5 filter, computes the digital result based on the most recent outputs from the delta-sigma modulator. At the most basic level, the digital filter can be thought of as simply averaging the modulator results in a weighted form and presenting thi ...

... The digital filter of the ADS1253, referred to as a sinc5 filter, computes the digital result based on the most recent outputs from the delta-sigma modulator. At the most basic level, the digital filter can be thought of as simply averaging the modulator results in a weighted form and presenting thi ...

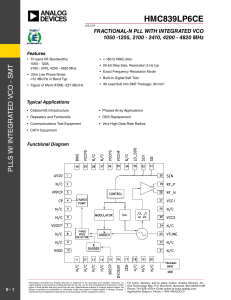

Quadrature Demodulator with IF PLL/VCO

... The CMX972 has a single-ended LO input. The demodulator LO can come from either the on-chip VCO/PLL or from an external source (RXLO pin), see section 5.3. Users should be aware that the presence of high levels of harmonics in the signals applied to the RXLO input might degrade quadrature accuracy. ...

... The CMX972 has a single-ended LO input. The demodulator LO can come from either the on-chip VCO/PLL or from an external source (RXLO pin), see section 5.3. Users should be aware that the presence of high levels of harmonics in the signals applied to the RXLO input might degrade quadrature accuracy. ...

Three Phase Power Calculations File

... Three phase systems uses lesser amount of wire than single phase systems for the same line voltage VL and same power delivered. ...

... Three phase systems uses lesser amount of wire than single phase systems for the same line voltage VL and same power delivered. ...

Three Phase Power Calculations File

... Three phase systems uses lesser amount of wire than single phase systems for the same line voltage VL and same power delivered. ...

... Three phase systems uses lesser amount of wire than single phase systems for the same line voltage VL and same power delivered. ...

Lecture 8

... —the OSPL90 is the output level of a hearing aid when the input level is 90 dB SPL and the gain control is full-on. REFERENCE TEST SETTING (RTS) —The reference-test setting is the position of the gain control necessary to yield the reference-test gain. REFERENCE TEST GAIN - The reference-test gain i ...

... —the OSPL90 is the output level of a hearing aid when the input level is 90 dB SPL and the gain control is full-on. REFERENCE TEST SETTING (RTS) —The reference-test setting is the position of the gain control necessary to yield the reference-test gain. REFERENCE TEST GAIN - The reference-test gain i ...

fvco VREF

... deactivation of the charge current pump occurs less fre quently and the time to achieve phase lock is greater. In some instances, the amount of time to achieve phase lock can be ...

... deactivation of the charge current pump occurs less fre quently and the time to achieve phase lock is greater. In some instances, the amount of time to achieve phase lock can be ...

Digital Radiography Image Parameters SNR, MTF, NPS, NEQ, DQE

... A detector that has a DQE value of twice that of another is said to be twice as efficient and therefore only requires half the amount of X-ray dose to produce an image with the same SNR. Hence, in theory, the higher the DQE of the detector the lower the patient exposure dose. Another general propert ...

... A detector that has a DQE value of twice that of another is said to be twice as efficient and therefore only requires half the amount of X-ray dose to produce an image with the same SNR. Hence, in theory, the higher the DQE of the detector the lower the patient exposure dose. Another general propert ...

DESIGN OF A PHASE LOCKED LOOP BASED CLOCKING CIRCUIT

... As I approach the finishing stages of my graduate career, looking back there are countless individuals who have helped make this journey special and memorable. Graduate school is full of numerous uncertainties, various roadblocks in terms of design and implementation of ideas; thus it is a journey t ...

... As I approach the finishing stages of my graduate career, looking back there are countless individuals who have helped make this journey special and memorable. Graduate school is full of numerous uncertainties, various roadblocks in terms of design and implementation of ideas; thus it is a journey t ...

AD9755 数据手册DataSheet 下载

... The AD9755 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

... The AD9755 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

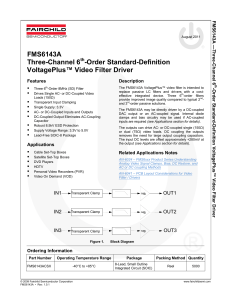

FMS6143A —Three-Channel 6th-Order

... Output Considerations The FMS6143A outputs are DC offset from the input by 150mV; therefore, VOUT = 2 x VIN DC + 150mV. This offset is required to obtain optimal performance from the output driver and is held at the minimum value to decrease the standing DC current into the load. Since the FMS6143A ...

... Output Considerations The FMS6143A outputs are DC offset from the input by 150mV; therefore, VOUT = 2 x VIN DC + 150mV. This offset is required to obtain optimal performance from the output driver and is held at the minimum value to decrease the standing DC current into the load. Since the FMS6143A ...

XE42 - 200 Series (HCACMOS), 5 V

... 5.0 V HCACMOS, + 50 PPM over -55 C to +125 C, Tristate Output, 883B Screening and 24.000 MHz ...

... 5.0 V HCACMOS, + 50 PPM over -55 C to +125 C, Tristate Output, 883B Screening and 24.000 MHz ...

AN2512

... The circuit for input voltage limiting is connected between the input EMI filter and the bulk capacitor C4. Such a circuitry includes a Power MOSFET and a self driven control section. The MOSFET Q1 is a standard N-Channel 500 V 3.3 Ω in D-PAK package, mounted on a small copper area to improve therma ...

... The circuit for input voltage limiting is connected between the input EMI filter and the bulk capacitor C4. Such a circuitry includes a Power MOSFET and a self driven control section. The MOSFET Q1 is a standard N-Channel 500 V 3.3 Ω in D-PAK package, mounted on a small copper area to improve therma ...