Audiometers, Calibration

... Output values obtained at SLM are compared to standards for each frequency tested (Table 4.1) ...

... Output values obtained at SLM are compared to standards for each frequency tested (Table 4.1) ...

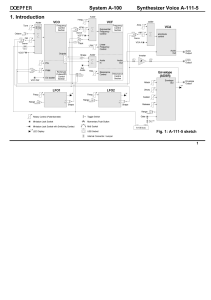

DOEPFER System A-100 Synthesizer Voice A-111

... filter is played as sine wave oscillator (see below). If half tracking is selected the filter frequency follows partly the VCO frequency (if the VCO goes up two octaves the filter frequency is increased by one octave). This position is chosen if an intermediate behaviour between full and no tracking ...

... filter is played as sine wave oscillator (see below). If half tracking is selected the filter frequency follows partly the VCO frequency (if the VCO goes up two octaves the filter frequency is increased by one octave). This position is chosen if an intermediate behaviour between full and no tracking ...

ADS801 数据资料 dataSheet 下载

... The analog input of the ADS801 can be configured in various ways and driven with different circuits, depending on the nature of the signal and the level of performance desired. The ADS801 has an internal reference that sets the full-scale input range of the A/D converter. The differential input rang ...

... The analog input of the ADS801 can be configured in various ways and driven with different circuits, depending on the nature of the signal and the level of performance desired. The ADS801 has an internal reference that sets the full-scale input range of the A/D converter. The differential input rang ...

Electronics 2 - Philadelphia University Jordan

... Between the two inputs. Both inputs. Differential amplifiers is called single ended if the input signal is applied to: One input with other input is connected to ground. Between the two inputs. Both inputs. Differential amplifiers is called common mode if the input signal is applied to ...

... Between the two inputs. Both inputs. Differential amplifiers is called single ended if the input signal is applied to: One input with other input is connected to ground. Between the two inputs. Both inputs. Differential amplifiers is called common mode if the input signal is applied to ...

Introduction to Digital Logic Design

... • From manufacturing point of view, using only one type of gates to implement the circuit is very advantageous. Why? Regular -> Simple -> easy to design -> cheap • Gates are the basic building blocks of all digital systems. They are implemented using electronics components (transistors, diodes, resi ...

... • From manufacturing point of view, using only one type of gates to implement the circuit is very advantageous. Why? Regular -> Simple -> easy to design -> cheap • Gates are the basic building blocks of all digital systems. They are implemented using electronics components (transistors, diodes, resi ...

A v - NCNU Moodle 課程

... The general area of electronics began about a century ago and used in the radio and radar communications during g the two world wars. Early systems incorporated “vacuum tubes,” amplifying devices that operated with the flow of electrons between plates in a vacuum chamber. 真空管 However, the fini ...

... The general area of electronics began about a century ago and used in the radio and radar communications during g the two world wars. Early systems incorporated “vacuum tubes,” amplifying devices that operated with the flow of electrons between plates in a vacuum chamber. 真空管 However, the fini ...

AR2111 Radio-on-a-Chip for 2.4 GHz Wireless LAN

... The AR2111 is packaged in a 48-pin leadless plastic chip carrier (LPCC). The LPCC can be sourced from any one of two package drawings. The external dimensions are identical from all sources. The LPCC package drawings and dimensions are provided in Figure 4-1 and Figure 4-2 and ...

... The AR2111 is packaged in a 48-pin leadless plastic chip carrier (LPCC). The LPCC can be sourced from any one of two package drawings. The external dimensions are identical from all sources. The LPCC package drawings and dimensions are provided in Figure 4-1 and Figure 4-2 and ...

ADS802 数据资料 dataSheet 下载

... pipelining. It uses a fully differential architecture and digital error correction to ensure 12-bit resolution. The differential track-and-hold circuit is shown in Figure 1. The switches are controlled by an internal clock that has a non-overlapping 2phase signal, φ1 and φ2. At the sampling time, th ...

... pipelining. It uses a fully differential architecture and digital error correction to ensure 12-bit resolution. The differential track-and-hold circuit is shown in Figure 1. The switches are controlled by an internal clock that has a non-overlapping 2phase signal, φ1 and φ2. At the sampling time, th ...

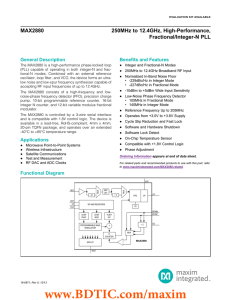

MAX2880 General Description Benefits and Features

... The MAX2880 is a high-performance phase-locked loop (PLL) capable of operating in both integer-N and fractional-N modes. Combined with an external reference oscillator, loop filter, and VCO, the device forms an ultralow noise and low-spur frequency synthesizer capable of accepting RF input frequenci ...

... The MAX2880 is a high-performance phase-locked loop (PLL) capable of operating in both integer-N and fractional-N modes. Combined with an external reference oscillator, loop filter, and VCO, the device forms an ultralow noise and low-spur frequency synthesizer capable of accepting RF input frequenci ...

AN-6024 — FMS6xxx Product Series Understanding Analog Video Signal Clamps, Bias, Description

... The DC restore approach can also be implemented with back-porch clamping, as in the FMS6403 and FMS6407 programmed to HD mode, which keeps a constant blanking level, even with large variations in the absolute sync amplitude. The first disadvantage with this approach is the necessity for an input cap ...

... The DC restore approach can also be implemented with back-porch clamping, as in the FMS6403 and FMS6407 programmed to HD mode, which keeps a constant blanking level, even with large variations in the absolute sync amplitude. The first disadvantage with this approach is the necessity for an input cap ...

a LC MOS 4-Channel, 12-Bit Simultaneous Sampling Data Acquisition System

... Conversion is initiated on the rising edge of CONVST. All four input track/holds go from track to hold on this edge. Conversion is first performed on the Channel 1 input voltage, then Channel 2 is converted and so on. The four results are stored in on-chip registers. When all four conversions have b ...

... Conversion is initiated on the rising edge of CONVST. All four input track/holds go from track to hold on this edge. Conversion is first performed on the Channel 1 input voltage, then Channel 2 is converted and so on. The four results are stored in on-chip registers. When all four conversions have b ...

Differential Clock/Data Multiplexer ICS831721I

... NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached ...

... NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached ...

A 7.2 GSa/s, 14 bit or 12 GSa/s, 12 bit Signal Generator on a Chip in

... Interpolation ratios of 12, 24 and 48 are possible, with available signal bandwidth of 480 MHz, 240 MHz and 120 MHz respectively. In the latter mode (interpolation ratio of 48), two distinct signals can be interpolated concurrently. The interpolator is designed as a sequence of interpolation stages ...

... Interpolation ratios of 12, 24 and 48 are possible, with available signal bandwidth of 480 MHz, 240 MHz and 120 MHz respectively. In the latter mode (interpolation ratio of 48), two distinct signals can be interpolated concurrently. The interpolator is designed as a sequence of interpolation stages ...

ZXLD1615 ADJUSTABLE DC-DC BOOST CONVERTER WITH INTERNAL SWITCH IN TSOT23-5 DESCRIPTION

... Suitable coils for use with the ZXLD1615 are shown in the table below: ...

... Suitable coils for use with the ZXLD1615 are shown in the table below: ...

Document

... limited by both XL and R. This current I is the same in XL and R, since they are in series. Each has its own series voltage drop, equal to IR for the resistance and IXl for the reactance. ...

... limited by both XL and R. This current I is the same in XL and R, since they are in series. Each has its own series voltage drop, equal to IR for the resistance and IXl for the reactance. ...

Center Boosted Sinusoidal Pulse Width Modulation for Three Phase

... High power electronic devices are being used increasingly to control and facilitate the flow of electric power in modern industries. These devices are able to enhance the voltage profile, which impacts dynamic performance and stability of the system improved by the way of operating (ON and OFF) the ...

... High power electronic devices are being used increasingly to control and facilitate the flow of electric power in modern industries. These devices are able to enhance the voltage profile, which impacts dynamic performance and stability of the system improved by the way of operating (ON and OFF) the ...

– NV Series – – Microphone Preamplifier – – DI –

... frequencies and a tilt upwards of the highs. This effect is highly dependant on the particular microphone, and the only way to know for sure is to try it. Keep in mind that the impedance change is accomplished by changing the step-up ratio of the input transformer, so a gain change happens as well. ...

... frequencies and a tilt upwards of the highs. This effect is highly dependant on the particular microphone, and the only way to know for sure is to try it. Keep in mind that the impedance change is accomplished by changing the step-up ratio of the input transformer, so a gain change happens as well. ...

DS92LV16 16-Bit Bus LVDS Serializer/Deserializer - 25

... ROUT[0:15], LOCK, and RCLK signals will drive a minimum of three CMOS input gates (15pF total load) at a 80 MHz clock rate. This drive capacity allows bussing outputs of multiple Deserializers and multiple destination ASIC inputs. REN controls TRI-STATE of the all outputs. The Deserializer input pin ...

... ROUT[0:15], LOCK, and RCLK signals will drive a minimum of three CMOS input gates (15pF total load) at a 80 MHz clock rate. This drive capacity allows bussing outputs of multiple Deserializers and multiple destination ASIC inputs. REN controls TRI-STATE of the all outputs. The Deserializer input pin ...

Filters and Impedance Matching

... E7G10 -- What absolute voltage gain can be expected from the circuit in Figure E7-4 when R1 is 1800 ohms and RF is 68 kilohms? A. 1 B. 0.03 C. 38 D. 76 ...

... E7G10 -- What absolute voltage gain can be expected from the circuit in Figure E7-4 when R1 is 1800 ohms and RF is 68 kilohms? A. 1 B. 0.03 C. 38 D. 76 ...

CAT661 - High Frequency 100 mA CMOS Charge Pump, Inverter

... discharge currents are increased, and the frequency is increased by approximately 6 times. Increasing the frequency will decrease the output impedance and ripple currents. This can be an advantage at high load currents. Increasing the frequency raises quiescent current but allows smaller capacitance ...

... discharge currents are increased, and the frequency is increased by approximately 6 times. Increasing the frequency will decrease the output impedance and ripple currents. This can be an advantage at high load currents. Increasing the frequency raises quiescent current but allows smaller capacitance ...