HMC853LC3

... General Description The HMC853LC3 is a D-Type Flip-Flop designed to support data transmission rates of up to 28 Gbps, and clock frequencies as high as 28 GHz. During normal operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative ...

... General Description The HMC853LC3 is a D-Type Flip-Flop designed to support data transmission rates of up to 28 Gbps, and clock frequencies as high as 28 GHz. During normal operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative ...

ICS83947I - Integrated Device Technology

... The 83947I is a low skew, 1-to-9 LVCMOS Fanout Buffer. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The effective fanout can be increased from 9 to 18 byutilizing the ability of the outputs to drive two series terminated lines. ...

... The 83947I is a low skew, 1-to-9 LVCMOS Fanout Buffer. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The effective fanout can be increased from 9 to 18 byutilizing the ability of the outputs to drive two series terminated lines. ...

Optical Pulse Distortion Measurement Limitations in Linear Time

... Clearly, the impulse response matrix of a network is the most useful quantity to obtain because it reflects all of the network's linear properties, including pulse distortion induced by PMD and chromatic dispersion. Within the limitations of discrete inverse Fourier transforms [8], the sequence Cn w ...

... Clearly, the impulse response matrix of a network is the most useful quantity to obtain because it reflects all of the network's linear properties, including pulse distortion induced by PMD and chromatic dispersion. Within the limitations of discrete inverse Fourier transforms [8], the sequence Cn w ...

Tasks - Hrvatski savez informatičara

... inputs and one output. Each of the inputs is connected to either a starting wire xj or to the output of another element cj . Of course, there are no cycles in a logic circuit and, moreover, it holds that the input of cj can be connected to the output of ci only when it holds i < j. Each starting wir ...

... inputs and one output. Each of the inputs is connected to either a starting wire xj or to the output of another element cj . Of course, there are no cycles in a logic circuit and, moreover, it holds that the input of cj can be connected to the output of ci only when it holds i < j. Each starting wir ...

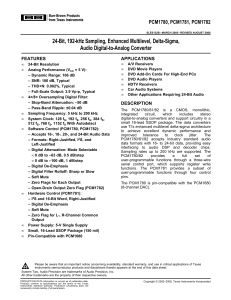

ADS2806 数据资料 dataSheet 下载

... The analog inputs of the ADS2806 are very high impedance and should be driven through an R-C network designed to pass the highest frequency of interest. This prevents highfrequency noise in the input from affecting SFDR and SNR. The ADS2806 can be used in a wide variety of applications and deciding ...

... The analog inputs of the ADS2806 are very high impedance and should be driven through an R-C network designed to pass the highest frequency of interest. This prevents highfrequency noise in the input from affecting SFDR and SNR. The ADS2806 can be used in a wide variety of applications and deciding ...

True-time delay line with separate carrier tuning

... all-optically controlled and continuously tunable signal delaying [8,12–16]. However, the slow light-induced TTDs suffer from the limitation that the product between the maximum delay time and the signal bandwidth is constant. As a result, only modest time delay can be expected for broadband baseban ...

... all-optically controlled and continuously tunable signal delaying [8,12–16]. However, the slow light-induced TTDs suffer from the limitation that the product between the maximum delay time and the signal bandwidth is constant. As a result, only modest time delay can be expected for broadband baseban ...

LT5571 - 620MHz – 1100MHz High Linearity Direct Quadrature Modulator.

... RFID, GSM, EDGE, CDMA, CDMA2000, and other systems. It may also be configured as an image reject upconverting mixer by applying 90° phase-shifted signals to the I and Q inputs. The high impedance I/Q baseband inputs consist of voltage-to-current converters that in turn drive double-balanced mixers. T ...

... RFID, GSM, EDGE, CDMA, CDMA2000, and other systems. It may also be configured as an image reject upconverting mixer by applying 90° phase-shifted signals to the I and Q inputs. The high impedance I/Q baseband inputs consist of voltage-to-current converters that in turn drive double-balanced mixers. T ...

Bass Amp schematic

... Long-tail pair derived from design by Randall Aiken. Added transformer feedback proportionally similar to that on the November, feedback resistor adjusted to keep Ri/ (Ri+Rf) same as November (see Aiken for details). If you want to be exact, use 110K. I used 120K to keep down number of different val ...

... Long-tail pair derived from design by Randall Aiken. Added transformer feedback proportionally similar to that on the November, feedback resistor adjusted to keep Ri/ (Ri+Rf) same as November (see Aiken for details). If you want to be exact, use 110K. I used 120K to keep down number of different val ...

SP6887 4 CHANNEL REGULATED CHARGE PUMP WLED DRIVER

... a DC Voltage to RSET Pin The example circuit in Figure 1 uses a 14.7k resistor and an analog input DC voltage, VSET, which varies from 1.2V to 0V to control LED current from 1mA to 30mA. Table 3 shows the resulting output. If necessary, the analog VSET voltage can be sourced from a voltage higher th ...

... a DC Voltage to RSET Pin The example circuit in Figure 1 uses a 14.7k resistor and an analog input DC voltage, VSET, which varies from 1.2V to 0V to control LED current from 1mA to 30mA. Table 3 shows the resulting output. If necessary, the analog VSET voltage can be sourced from a voltage higher th ...

LM2889 TV Video Modulator

... Q23. A current regulator consisting of devices Q17 – Q21 is used to achieve good RF stability over temperature and ...

... Q23. A current regulator consisting of devices Q17 – Q21 is used to achieve good RF stability over temperature and ...

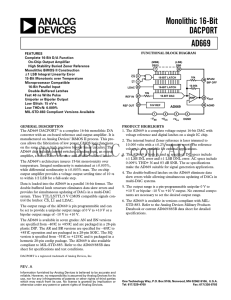

AD669 数据手册DataSheet 下载

... the Analog Circuit Connections section. *Same as AD669AN/AR specification. Specifications subject to change without notice. Specifications in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max ...

... the Analog Circuit Connections section. *Same as AD669AN/AR specification. Specifications subject to change without notice. Specifications in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max ...

IOSR Journal of Electronics and Communication Engineering (IOSRJECE)

... MOS (Metal Oxide Semiconductor) technology is more susceptible to ESD [1-4] but some of the newer high speed components can be ruined with low voltages. Damage to components can, and usually do, occur when the part is in the ESD path. Many components in the circuits are very robust, can handle the d ...

... MOS (Metal Oxide Semiconductor) technology is more susceptible to ESD [1-4] but some of the newer high speed components can be ruined with low voltages. Damage to components can, and usually do, occur when the part is in the ESD path. Many components in the circuits are very robust, can handle the d ...

Get low-noise, low-ripple, high

... 1 + R1/R2). The noise contribution from components later in the signal path is insignificant when compared to the noise at the error-amplifier inputs. In fact, when modestsized feedback resistors are used, most of the regulator’s noise comes from the amplified bandgap reference. As shown in Figure 1 ...

... 1 + R1/R2). The noise contribution from components later in the signal path is insignificant when compared to the noise at the error-amplifier inputs. In fact, when modestsized feedback resistors are used, most of the regulator’s noise comes from the amplified bandgap reference. As shown in Figure 1 ...

HMC723LC3C 数据资料DataSheet下载

... General Description The HMC723LC3C is a D-type Flip Flop designed to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. During normal operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negativ ...

... General Description The HMC723LC3C is a D-type Flip Flop designed to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. During normal operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negativ ...

Digital Examination2 - Philadelphia University Jordan

... Programmed AND array & fixed OR array. Fixed AND array & programmed OR array. Programmed AND & OR arrays. 59- Digital signal vary between two levels; Smoothly (linearly). Continuously (Sine signal). Abruptly (In discrete manner). 60- One of the digital family can be utilized in VLSI circ ...

... Programmed AND array & fixed OR array. Fixed AND array & programmed OR array. Programmed AND & OR arrays. 59- Digital signal vary between two levels; Smoothly (linearly). Continuously (Sine signal). Abruptly (In discrete manner). 60- One of the digital family can be utilized in VLSI circ ...

New CMOS Realization of Voltage Differencing Buffered Amplifier

... voltage-mode biquad filter configurations are presented for VDBA application. Each proposed filter employs two active elements and two or three passive components. Filters, having three inputs and single output, can realize voltagemode low-pass, band-pass, high-pass, band-stop, and allpass filters. ...

... voltage-mode biquad filter configurations are presented for VDBA application. Each proposed filter employs two active elements and two or three passive components. Filters, having three inputs and single output, can realize voltagemode low-pass, band-pass, high-pass, band-stop, and allpass filters. ...

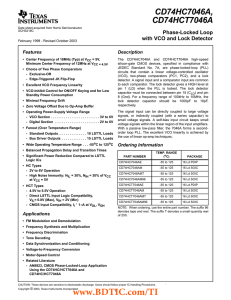

CD74HCT7046A 数据资料 dataSheet 下载

... and COMPIN over the full frequency range of the VCO. Moreover, the power dissipation due to the low-pass filter is reduced because both p-type and n-type drivers are “OFF” for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the ...

... and COMPIN over the full frequency range of the VCO. Moreover, the power dissipation due to the low-pass filter is reduced because both p-type and n-type drivers are “OFF” for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the ...

AM Principles_Lecture2

... • A differential amplifier makes a good amplitude modulator. The modulating signal is used to vary the common mode current in the transistors that amplify the carrier. • Most integrated circuit (IC) amplitude modulators are based upon the differential amplifier modulator. ...

... • A differential amplifier makes a good amplitude modulator. The modulating signal is used to vary the common mode current in the transistors that amplify the carrier. • Most integrated circuit (IC) amplitude modulators are based upon the differential amplifier modulator. ...

EQ34877880

... 1.2V. The main advantage of flash adc is that it is one of the fastest adc. The reference voltage source is implemented using band gap reference circuit and verified the performance by varying temperature from -100 C to 70 0 C. ...

... 1.2V. The main advantage of flash adc is that it is one of the fastest adc. The reference voltage source is implemented using band gap reference circuit and verified the performance by varying temperature from -100 C to 70 0 C. ...