Low Power, 350 MHz Voltage Feedback Amplifiers AD8038/AD8039

... is the voltage between the supply pins (VS) multiplied by the quiescent current (IS). Assuming the load (RL) is referenced to midsupply, then the total drive power is VS/2 × IOUT, some of which is dissipated in the package and some in the load (VOUT × IOUT). The difference between the total drive po ...

... is the voltage between the supply pins (VS) multiplied by the quiescent current (IS). Assuming the load (RL) is referenced to midsupply, then the total drive power is VS/2 × IOUT, some of which is dissipated in the package and some in the load (VOUT × IOUT). The difference between the total drive po ...

TLC548 数据资料 dataSheet 下载

... charging of internal capacitors to the level of the analog input voltage. 3. Three more I/O CLOCK cycles are then applied to the I/O CLOCK terminal and the sixth, seventh, and eighth conversion bits are shifted out on the falling edges of these clock cycles. 4. The final (the eighth) clock cycle is ...

... charging of internal capacitors to the level of the analog input voltage. 3. Three more I/O CLOCK cycles are then applied to the I/O CLOCK terminal and the sixth, seventh, and eighth conversion bits are shifted out on the falling edges of these clock cycles. 4. The final (the eighth) clock cycle is ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331,

... Unfortunately, all the power control techniques deliberately distort sinusoidal wave form of power frequency and generate unwanted interfering signals. Obviously, they all are often cited as one of the main source of conducted emission (CE). Usually the power supplies which are using controlling tec ...

... Unfortunately, all the power control techniques deliberately distort sinusoidal wave form of power frequency and generate unwanted interfering signals. Obviously, they all are often cited as one of the main source of conducted emission (CE). Usually the power supplies which are using controlling tec ...

Tactile Sensor with Automatic Gain Control

... same frequency and by applying an appropriate low pass filter. Then, the AGC changes the amplitude for each base function for the input signal. By introducing a simple feedback loop into the AGC, the feedback system always tries to keep the output from each sub-sensor unit to a reference value, irres ...

... same frequency and by applying an appropriate low pass filter. Then, the AGC changes the amplitude for each base function for the input signal. By introducing a simple feedback loop into the AGC, the feedback system always tries to keep the output from each sub-sensor unit to a reference value, irres ...

Sensor fusion for improved control of piezoelectric tube scanners

... piezoelectric tube scanners (and piezoelectric actuators in general). When employed in an actuating role, piezoelectric transducers display a significant hysteresis in the transfer function from an applied voltage to strain or displacement [1]. Due to hysteresis, ideal scanning signals can result in ...

... piezoelectric tube scanners (and piezoelectric actuators in general). When employed in an actuating role, piezoelectric transducers display a significant hysteresis in the transfer function from an applied voltage to strain or displacement [1]. Due to hysteresis, ideal scanning signals can result in ...

AD9762 数据手册DataSheet 下载

... series of high performance, low power CMOS digital-to-analog converters (DACs). The TxDAC family which consists of pin compatible 8-, 10-, 12-, and 14-bit DACs is specifically optimized for the transmit signal path of communication systems. All of the devices share the same interface options, small ...

... series of high performance, low power CMOS digital-to-analog converters (DACs). The TxDAC family which consists of pin compatible 8-, 10-, 12-, and 14-bit DACs is specifically optimized for the transmit signal path of communication systems. All of the devices share the same interface options, small ...

Analog Electronics Citcuit Lab manual for B. tech 5th sem.

... voltage output (Vo) adjust the pot meter R4 to get the overall gain of 10. 4. To observe the frequency response of the first stage disconnects the second stage by removing the right lead of Cc, which is connected, to the base of second transistor. 5. Find the maximum voltage output by varying the fr ...

... voltage output (Vo) adjust the pot meter R4 to get the overall gain of 10. 4. To observe the frequency response of the first stage disconnects the second stage by removing the right lead of Cc, which is connected, to the base of second transistor. 5. Find the maximum voltage output by varying the fr ...

a AN-555 APPLICATION NOTE

... designed to accept inputs from any generic word generator. However, when running the DAC at high sample rates, the quality of the digital data can have an impact on the performance of the DAC. As an example, if the edges of the digital information are slow, or the edges of the various bits are skewe ...

... designed to accept inputs from any generic word generator. However, when running the DAC at high sample rates, the quality of the digital data can have an impact on the performance of the DAC. As an example, if the edges of the digital information are slow, or the edges of the various bits are skewe ...

Technote 7 Using Op Amps Successfully

... GBW = ∞ BW = ∞ or Delay = 0 and GBW = ∞ Unlimited input voltage range. Differential response only Immune to PS offset and variations Output due to signal only ...

... GBW = ∞ BW = ∞ or Delay = 0 and GBW = ∞ Unlimited input voltage range. Differential response only Immune to PS offset and variations Output due to signal only ...

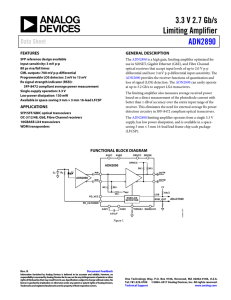

ADN2890ACPZ-RL Datasheet

... line in order to minimize the mismatch in the 50 Ω transmission line at the capacitor’s pads. It is recommended that the transmission lines not change layers through vias, if possible. For supply decoupling, the 1 nF decoupling capacitor should be placed on the same layer as the ADN2890 as close as ...

... line in order to minimize the mismatch in the 50 Ω transmission line at the capacitor’s pads. It is recommended that the transmission lines not change layers through vias, if possible. For supply decoupling, the 1 nF decoupling capacitor should be placed on the same layer as the ADN2890 as close as ...

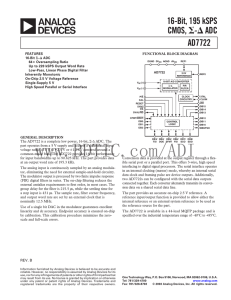

16-Bit, 195 kSPS CMOS, AD7722 -

... Synchronization Logic Input. SYNC is an asynchronous input. When using more than one AD7722 operated from a common master clock, SYNC allows each ADC’s Σ-∆ modulator to simultaneously sample its analog input and update its output data register. A rising edge resets the AD7722 digital filter sequence ...

... Synchronization Logic Input. SYNC is an asynchronous input. When using more than one AD7722 operated from a common master clock, SYNC allows each ADC’s Σ-∆ modulator to simultaneously sample its analog input and update its output data register. A rising edge resets the AD7722 digital filter sequence ...

AF04701186190

... 6.7dB and third order Input intercept point -1db, power consumption of 3.86mW at 1.8V supply voltage. The 50Ω matched impedance condition is applicable. Result shows a good potential of this CMOS mixer and justify its use for low-power wireless communications. Keywords—Mixer, Gilbert Cell, RFIC, CMO ...

... 6.7dB and third order Input intercept point -1db, power consumption of 3.86mW at 1.8V supply voltage. The 50Ω matched impedance condition is applicable. Result shows a good potential of this CMOS mixer and justify its use for low-power wireless communications. Keywords—Mixer, Gilbert Cell, RFIC, CMO ...

OPA354-Q1 OPA2354-Q1

... The specified input common-mode voltage range of the OPA354 extends 100 mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair, as shown in Figure 1. The N-channel pair is active for input volt ...

... The specified input common-mode voltage range of the OPA354 extends 100 mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair, as shown in Figure 1. The N-channel pair is active for input volt ...