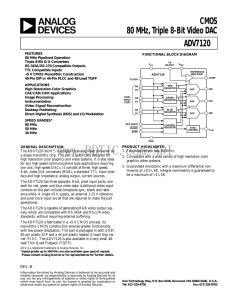

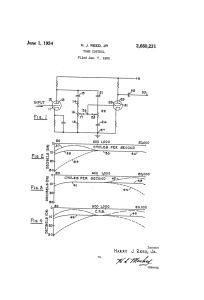

pat2680231_reed.pdf

... order of 800 cycles per second. Then, in effectkinds. I n general, any device which has an elecing tone control, it is usual to provide an attenuating network which attenuates the fretrical output with a range of frequencies in the aud.ible region may employ a tone control. Also 10 quencies at the m ...

... order of 800 cycles per second. Then, in effectkinds. I n general, any device which has an elecing tone control, it is usual to provide an attenuating network which attenuates the fretrical output with a range of frequencies in the aud.ible region may employ a tone control. Also 10 quencies at the m ...

iraudamp4a

... increase slightly when all channels are driven (ACD) with the self oscillator, especially below the 5 W range. Residual noise typically increases by a third or more (see “Specifications – Audio Performance”) compared to a single-channel driven (SCD) configuration. Locking the oscillator frequency re ...

... increase slightly when all channels are driven (ACD) with the self oscillator, especially below the 5 W range. Residual noise typically increases by a third or more (see “Specifications – Audio Performance”) compared to a single-channel driven (SCD) configuration. Locking the oscillator frequency re ...

ABSTRACT - The University of Maryland

... I would like to acknowledge people who have contributed to the projects and helped me during my Ph.D. study and research. The first two persons I want to thank are my current and previous advisor, Professor Neil Goldsman and Professor Pamela Abshire. I want to thank them not only because of their br ...

... I would like to acknowledge people who have contributed to the projects and helped me during my Ph.D. study and research. The first two persons I want to thank are my current and previous advisor, Professor Neil Goldsman and Professor Pamela Abshire. I want to thank them not only because of their br ...

chapter 13 Transceiver Design Example

... Explain why the outputs of the two ÷ 2 circuits in the previous architecture with a VCO and a divider for the two bands are multiplexed. That is, why not apply the fVCO=4 output to the ÷ N stage in the 11a mode as well? Driving the ÷ N stage by fVCO=4 is indeed desirable as it eases the design of th ...

... Explain why the outputs of the two ÷ 2 circuits in the previous architecture with a VCO and a divider for the two bands are multiplexed. That is, why not apply the fVCO=4 output to the ÷ N stage in the 11a mode as well? Driving the ÷ N stage by fVCO=4 is indeed desirable as it eases the design of th ...

ADV7120 数据手册DataSheet 下载

... All video data and control inputs are latched into the ADV7120 on the rising edge of CLOCK, as previously described in the “Digital Inputs” section. It is recommended that the CLOCK input to the ADV7120 be driven by a TTL buffer (e.g., ...

... All video data and control inputs are latched into the ADV7120 on the rising edge of CLOCK, as previously described in the “Digital Inputs” section. It is recommended that the CLOCK input to the ADV7120 be driven by a TTL buffer (e.g., ...

MM74HCT273 Octal D-Type Flip-Flop with Clear MM74HCT273 Oct a

... These positive edge-triggered flip-flops have a common clock and clear-independent Q outputs. Data on a D input, having the specified set-up and hold time, is transferred to the corresponding Q output on the positive-going transition of the clock pulse. The asynchronous clear forces all outputs LOW ...

... These positive edge-triggered flip-flops have a common clock and clear-independent Q outputs. Data on a D input, having the specified set-up and hold time, is transferred to the corresponding Q output on the positive-going transition of the clock pulse. The asynchronous clear forces all outputs LOW ...

Si5345/44/42 - Silicon Labs

... These jitter attenuating clock multipliers combine fourth-generation DSPLL and MultiSynth™ technologies to enable any-frequency clock generation and jitter attenuation for applications requiring the highest level of jitter performance. These devices are programmable via a serial interface with in-ci ...

... These jitter attenuating clock multipliers combine fourth-generation DSPLL and MultiSynth™ technologies to enable any-frequency clock generation and jitter attenuation for applications requiring the highest level of jitter performance. These devices are programmable via a serial interface with in-ci ...

Low Voltage Micropower Quad Operational Amplifier OP490

... of supply current. In many battery-powered circuits, the OP490 can be continuously operated for hundreds of hours before requiring battery replacement, reducing equipment downtime and operating costs. High performance portable equipment and instruments frequently use lithium cells because of their l ...

... of supply current. In many battery-powered circuits, the OP490 can be continuously operated for hundreds of hours before requiring battery replacement, reducing equipment downtime and operating costs. High performance portable equipment and instruments frequently use lithium cells because of their l ...

Document

... by signal variation in amplitude and/or rise time Jitter effect - timing fluctuations caused by noise and/or statistical fluctuations in the detector (intrinsic noise) two identical signal will not always trigger at the same point (time stamp) time variation dependent on the amplitude of fluctuati ...

... by signal variation in amplitude and/or rise time Jitter effect - timing fluctuations caused by noise and/or statistical fluctuations in the detector (intrinsic noise) two identical signal will not always trigger at the same point (time stamp) time variation dependent on the amplitude of fluctuati ...

TDA7200 ASK/FSK Single Conversion Receiver Version 1.0

... contained fully on chip. The Limiter output differential signal is fed to the linear phase detector as is the output of the 10.7 MHz center frequency VCO. The demodulator gain is typically 200µV/kHz. The passive loop filter output that is comprised fully on chip is fed to both the VCO and the modula ...

... contained fully on chip. The Limiter output differential signal is fed to the linear phase detector as is the output of the 10.7 MHz center frequency VCO. The demodulator gain is typically 200µV/kHz. The passive loop filter output that is comprised fully on chip is fed to both the VCO and the modula ...

SIMULATION OF LCC RESONANT CIRCUITS PURPOSE POWER ELECTRONICS ECE562 COLORADO STATE UNIVERSITY

... Question: How does the output power compare to the input power? Doesn’t this violate the “Conservation of Energy” concept? Answer: No, it doesn’t. Power can only be dissipated in R, since L, Cp and Cs are considered non-lossy, or ideal. In Figure 10, the input current peaks at -19.215 dB(Amps) = 109 ...

... Question: How does the output power compare to the input power? Doesn’t this violate the “Conservation of Energy” concept? Answer: No, it doesn’t. Power can only be dissipated in R, since L, Cp and Cs are considered non-lossy, or ideal. In Figure 10, the input current peaks at -19.215 dB(Amps) = 109 ...

ADS5204 数据资料 dataSheet 下载

... (1) Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero to full-scale. The point used as zero occurs ½LSB before the first code transition. The full-scale point is defined as a level ½LSB beyond the last code transition. The deviation is measured from th ...

... (1) Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero to full-scale. The point used as zero occurs ½LSB before the first code transition. The full-scale point is defined as a level ½LSB beyond the last code transition. The deviation is measured from th ...

Document

... opamps with strictly capacitive loads can have large output resistance → Operational Transconductance Amplifiers (OTA) often also called opamp the output may be single ended (referenced to ground) or differential single or symmetrical supply voltages ...

... opamps with strictly capacitive loads can have large output resistance → Operational Transconductance Amplifiers (OTA) often also called opamp the output may be single ended (referenced to ground) or differential single or symmetrical supply voltages ...

Chapter 17 Engineering Electric Circuits: AC Electric Circuits Homework # 145

... 03. What is the period of oscillation of an LC circuit consisting of a 15.0-mH coil and a 150.0-mF capacitor? 04. An LC circuit, with a 65.0-mF capacitor, oscillates at a 60.0-Hz frequency. What is the inductance of the inductor? 05. Circuit 1 is an LC circuit that has an inductance of L 1 and a cap ...

... 03. What is the period of oscillation of an LC circuit consisting of a 15.0-mH coil and a 150.0-mF capacitor? 04. An LC circuit, with a 65.0-mF capacitor, oscillates at a 60.0-Hz frequency. What is the inductance of the inductor? 05. Circuit 1 is an LC circuit that has an inductance of L 1 and a cap ...

a general approach for optimizing dynamic response for buck

... buck, push−pull, half−bridge and full−bridge using either voltage or current mode control techniques. These converters exhibit a relatively low phase shift below the pole contributed by the output filter, so no phase boost is required from the compensation network stage. Type−I compensation network ...

... buck, push−pull, half−bridge and full−bridge using either voltage or current mode control techniques. These converters exhibit a relatively low phase shift below the pole contributed by the output filter, so no phase boost is required from the compensation network stage. Type−I compensation network ...