AD642 - IHS.com

... current-to-voltage converting amplifier. This possibility necessitates some form of input protection. Many electrometer type devices, especially CMOS designs, can require elaborate Zener protection schemes which often compromise overall performance. The AD642 requires input protection only if the so ...

... current-to-voltage converting amplifier. This possibility necessitates some form of input protection. Many electrometer type devices, especially CMOS designs, can require elaborate Zener protection schemes which often compromise overall performance. The AD642 requires input protection only if the so ...

ADS5272 数据资料 dataSheet 下载

... Simultaneous Sample-and-Hold 71.1dBFS SNR at 5MHz IF 3.3V Digital/Analog Supply Serialized LVDS Outputs Integrated Frame and Bit Patterns Option to Double LVDS Clock Output Currents Four Current Modes for LVDS Pin- and Format-Compatible Family TQFP-80 PowerPAD™ Package ...

... Simultaneous Sample-and-Hold 71.1dBFS SNR at 5MHz IF 3.3V Digital/Analog Supply Serialized LVDS Outputs Integrated Frame and Bit Patterns Option to Double LVDS Clock Output Currents Four Current Modes for LVDS Pin- and Format-Compatible Family TQFP-80 PowerPAD™ Package ...

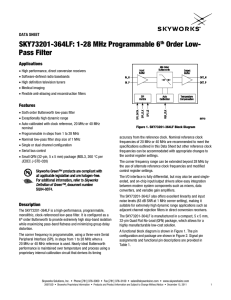

SKY73201-364LF 数据资料DataSheet下载

... specifications outlined in this Data Sheet but other reference clock frequencies can be accommodated with appropriate changes to the control register settings. The corner frequency range can be extended beyond 28 MHz by the use of alternate reference clock frequencies and modified control register s ...

... specifications outlined in this Data Sheet but other reference clock frequencies can be accommodated with appropriate changes to the control register settings. The corner frequency range can be extended beyond 28 MHz by the use of alternate reference clock frequencies and modified control register s ...

05-SignalEncodingTechniques

... between two types of errors or noise. When the analog waveform is changing very slowly, there will be quantizing noise. This noise increases as is increased. when the analog waveform is changing more rapidly than the staircase can follow, there is slope overload noise ...

... between two types of errors or noise. When the analog waveform is changing very slowly, there will be quantizing noise. This noise increases as is increased. when the analog waveform is changing more rapidly than the staircase can follow, there is slope overload noise ...

SR Latch Circuit

... A synchronous sequential circuit is a circuit that changes state only at discrete instants of time. The most frequently encountered is the clocked sequential circuit. Typically, synchronization is achieved by a timing device called a master-clock generator. ...

... A synchronous sequential circuit is a circuit that changes state only at discrete instants of time. The most frequently encountered is the clocked sequential circuit. Typically, synchronization is achieved by a timing device called a master-clock generator. ...

lab4_beam_vibration

... After setting the parameters on the front panel of the VI, the beam is impacted lightly and run the VI. After sampling the signal from the strain gage conditioner for a pre-determined length of time the sampled signal is displayed along with the values for n, , and . The second VI “phaseAngle815 ...

... After setting the parameters on the front panel of the VI, the beam is impacted lightly and run the VI. After sampling the signal from the strain gage conditioner for a pre-determined length of time the sampled signal is displayed along with the values for n, , and . The second VI “phaseAngle815 ...

Electronics Lab Manual

... controls the collector current of a common emitter amplifier. A small increase in base current results in a relatively large increase in collector current. Similarly, a small decrease in base current causes large decrease in collector current. The emitter-base junction must be forward biased and the ...

... controls the collector current of a common emitter amplifier. A small increase in base current results in a relatively large increase in collector current. Similarly, a small decrease in base current causes large decrease in collector current. The emitter-base junction must be forward biased and the ...

1 - Telecommunications Industry Association

... measurement. If the value obtained is lower than the most restrictive limit specified for that frequency range, then the signal levels in 8 kHz bands in that range will be lower than that specified for the most restrictive 8 kHz band. However, the main procedure of Section 9.16.5 should be used when ...

... measurement. If the value obtained is lower than the most restrictive limit specified for that frequency range, then the signal levels in 8 kHz bands in that range will be lower than that specified for the most restrictive 8 kHz band. However, the main procedure of Section 9.16.5 should be used when ...

Receiver Dynamic Range: Part 1

... describe the upper limit of dynamic range for desired signals only. Measuring the 1-dB compression point due to blocking can be accomplished by combining a small, desired sinusoid with a large, undesired sinusoid, and applying them to the receiver input. The desired sinusoid is at the receiver’s tun ...

... describe the upper limit of dynamic range for desired signals only. Measuring the 1-dB compression point due to blocking can be accomplished by combining a small, desired sinusoid with a large, undesired sinusoid, and applying them to the receiver input. The desired sinusoid is at the receiver’s tun ...

Page 43, Foundation Electronics, Kemp

... For each of the specifications below draw out the Karnaugh map and produce a circuit using NAND gates only to satisfy requirements. 30. The shuttle has a voting system whereby 3 computers vote on what to do. The final decision always goes with the majority so that if one computer goes down the other ...

... For each of the specifications below draw out the Karnaugh map and produce a circuit using NAND gates only to satisfy requirements. 30. The shuttle has a voting system whereby 3 computers vote on what to do. The final decision always goes with the majority so that if one computer goes down the other ...

Lesson T5B - Math and Gain

... Practice by performing the following conversions (fill in the blanks): ...

... Practice by performing the following conversions (fill in the blanks): ...

AD7663 数据手册DataSheet下载

... When SER/PAR is HIGH, EXT/INT is LOW and RDC/SDIN is LOW, which is the Serial Master Read after Convert Mode. These inputs, part of the Serial Port, are used to slow down, if desired, the internal serial clock that clocks the data output. In the other serial modes, these pins are high impedance outp ...

... When SER/PAR is HIGH, EXT/INT is LOW and RDC/SDIN is LOW, which is the Serial Master Read after Convert Mode. These inputs, part of the Serial Port, are used to slow down, if desired, the internal serial clock that clocks the data output. In the other serial modes, these pins are high impedance outp ...

Microphones - Music Technology 2

... S Same principles but doesn’t require external power, referred to ...

... S Same principles but doesn’t require external power, referred to ...

Paper Title (use style: paper title)

... response, with resonant frequency around 250 kHz, unlike the 39-40 kHz transducers that have a bandwidth of a 2..5 kHz. This characteristic must be taken in consideration when the transmitter-air-receiver system will be modeled. The directivity graph has been obtained using ultrasounds with 280 kHz ...

... response, with resonant frequency around 250 kHz, unlike the 39-40 kHz transducers that have a bandwidth of a 2..5 kHz. This characteristic must be taken in consideration when the transmitter-air-receiver system will be modeled. The directivity graph has been obtained using ultrasounds with 280 kHz ...

- Sacramento

... This project demonstrates design of seven components that make up the radar: oscillator, power divider, high gain amplifier, low noise amplifier, transmitter antenna, receiver antenna, a mixer, and a low pass filter. Figure 1 shows a block diagram of the radar. All of the radars mentioned in the pre ...

... This project demonstrates design of seven components that make up the radar: oscillator, power divider, high gain amplifier, low noise amplifier, transmitter antenna, receiver antenna, a mixer, and a low pass filter. Figure 1 shows a block diagram of the radar. All of the radars mentioned in the pre ...

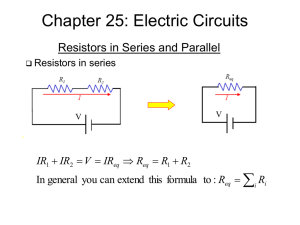

Chapter 3 - Loop Analysis(PowerPoint Format)

... • The KVL equations are written in terms of loop currents, common to all elements in a loop. • The result will be a system of equations in which the unknowns are these loop currents. • The solution of these equations will, therefore, yield values for the loop currents. ...

... • The KVL equations are written in terms of loop currents, common to all elements in a loop. • The result will be a system of equations in which the unknowns are these loop currents. • The solution of these equations will, therefore, yield values for the loop currents. ...

emt212_ch.2 op-amp application and frequency

... goes from a lower to higher value than when it goes from a higher to a lower value. The two reference levels are referred to as the upper trigger point (UTP) and the lower trigger ...

... goes from a lower to higher value than when it goes from a higher to a lower value. The two reference levels are referred to as the upper trigger point (UTP) and the lower trigger ...