Tutorial 3 - Lehrstuhl für Technische Elektronik

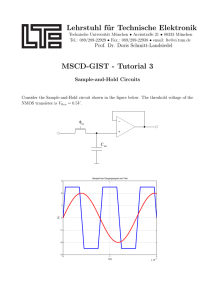

... Consider the Sample-and-Hold circuit shown in the figure below. The threshold voltage of the NMOS transistor is Vth,n = 0.5V . ...

... Consider the Sample-and-Hold circuit shown in the figure below. The threshold voltage of the NMOS transistor is Vth,n = 0.5V . ...

Electronics Summary Reminder: Voltage Division Example of

... It takes time to charge/ discharge a capacitor Time to charge/discharge is related exponentially to RC It takes energy to charge a capacitor Energy stored in a capacitor is (1/2)CV2 ...

... It takes time to charge/ discharge a capacitor Time to charge/discharge is related exponentially to RC It takes energy to charge a capacitor Energy stored in a capacitor is (1/2)CV2 ...

ECE 4340/5340 VLSI Design I, Final Exam

... 1) Find the maximum voltage across the capacitor Cs after write “1” operation. Include body effect..VDD=5V. 2) Assuming zero leakage current in the circuit, find the voltage at the bit line during read ‘1’ operation after the bit line is first pre charged to VDD/2. 3) If the transistor has a leakage ...

... 1) Find the maximum voltage across the capacitor Cs after write “1” operation. Include body effect..VDD=5V. 2) Assuming zero leakage current in the circuit, find the voltage at the bit line during read ‘1’ operation after the bit line is first pre charged to VDD/2. 3) If the transistor has a leakage ...

CMOS & TTL gates, Electrical characteristics and timing

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

Sequential MOS Logic Circuits

... •Sequential Circuit •Behavior of Bistable Elements •SR Latch Circuit •Clocked Latch and Flip Flop Circuits ...

... •Sequential Circuit •Behavior of Bistable Elements •SR Latch Circuit •Clocked Latch and Flip Flop Circuits ...

Lab #3

... The total area of the design will be approximated by adding up the gate area (W*L) for all the transistors in the circuit. The figure of merit for the design will be (voltage gain)/(power*gate_area). For the resistors, the material’s sheet resistance is 250Ohm/square with the minimum width and lengt ...

... The total area of the design will be approximated by adding up the gate area (W*L) for all the transistors in the circuit. The figure of merit for the design will be (voltage gain)/(power*gate_area). For the resistors, the material’s sheet resistance is 250Ohm/square with the minimum width and lengt ...

EE121Lec02 - My FIT (my.fit.edu)

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

Automotive Qualified AUIRS2117S and AUIRS2118S Deliver

... signal and CMOS Schmitt-triggered inputs with pull-down. • The AUIRS2118S features output signals out of phase with the input signal and CMOS Schmitt-triggered inputs with pull-up. • The new ICs feature proprietary high-voltage integrated circuit (HVIC) and latch immune CMOS technologies to offer ru ...

... signal and CMOS Schmitt-triggered inputs with pull-down. • The AUIRS2118S features output signals out of phase with the input signal and CMOS Schmitt-triggered inputs with pull-up. • The new ICs feature proprietary high-voltage integrated circuit (HVIC) and latch immune CMOS technologies to offer ru ...

Homework 4:Power, Scaling, Wires and Logic (ms

... out on a contiguous diffusion strip. d) Size the PMOS transistors such that the resistance of the PMOS network is always equal or smaller than a single minimum-size PMOS device, yet is minimal in area. ...

... out on a contiguous diffusion strip. d) Size the PMOS transistors such that the resistance of the PMOS network is always equal or smaller than a single minimum-size PMOS device, yet is minimal in area. ...

Power Fundamentals: Linear Regulator Fundamentals

... – Requires that the input voltage be higher than the output voltage based on the load current and the On Resistance of the pass element: • VIN > RDS(on) x IOUT – Requires that the output voltage be higher than the VGS requirement of the pass element – Requires careful selection of the output capacit ...

... – Requires that the input voltage be higher than the output voltage based on the load current and the On Resistance of the pass element: • VIN > RDS(on) x IOUT – Requires that the output voltage be higher than the VGS requirement of the pass element – Requires careful selection of the output capacit ...

Static CMOS Gates

... Both inputs tied together: effective WN=2W, WP=2W, VS shifts to the left. Both input A=ground, sweep VB: effective WN=W, WP=4W, VS shifts to the right. ...

... Both inputs tied together: effective WN=2W, WP=2W, VS shifts to the left. Both input A=ground, sweep VB: effective WN=W, WP=4W, VS shifts to the right. ...

Carbon nanotube logic device operates on subnanowatt

... extremely low power consumption, the p-type and ntype transistors need to have precisely tuned and well-separated threshold voltages, which are the voltage levels that determine whether the device is ON or OFF. So far, this issue of the threshold voltages has not been addressed, and the researchers ...

... extremely low power consumption, the p-type and ntype transistors need to have precisely tuned and well-separated threshold voltages, which are the voltage levels that determine whether the device is ON or OFF. So far, this issue of the threshold voltages has not been addressed, and the researchers ...

Jordan University of Science and Technology Abstract: Authors: Low

... order to suppress the stand-by leakage-current, while low threshold voltage MOSFET transistors are applied on the cross-coupled critical path which in fact is the speed bottle neck of the ?ip-?ip. This happened in order to increase the speed of operation of the circuit and to reduce the power dissip ...

... order to suppress the stand-by leakage-current, while low threshold voltage MOSFET transistors are applied on the cross-coupled critical path which in fact is the speed bottle neck of the ?ip-?ip. This happened in order to increase the speed of operation of the circuit and to reduce the power dissip ...

latch_up - WordPress.com

... enough space so that R1 /R2 and R3 /R4 and the various s are small enough to prevent latchup. ...

... enough space so that R1 /R2 and R3 /R4 and the various s are small enough to prevent latchup. ...

Basic CMOS concepts

... values. Both pull-up and pull-down cannot be active at the same time (it makes no sense to set the output to 1 and 0 for the same inputs!!). Similarly, both the pull-up and the pull-down cannot be off at the same time (logic functions have always a defined output –either 0 or 1). Nevertheless, we wi ...

... values. Both pull-up and pull-down cannot be active at the same time (it makes no sense to set the output to 1 and 0 for the same inputs!!). Similarly, both the pull-up and the pull-down cannot be off at the same time (logic functions have always a defined output –either 0 or 1). Nevertheless, we wi ...

A Low-Power CMOS Output Buffer A low

... split-path (LBFS) CMOS buffer is proposed.By using the feedback-controlled split-path method, the short-circuit current of the output inverter stage is eliminated. The dynamic power dissipation of the LBFS CMOS buffer can be reduced by limited the gate voltage swing of the output inverter. Moreover, ...

... split-path (LBFS) CMOS buffer is proposed.By using the feedback-controlled split-path method, the short-circuit current of the output inverter stage is eliminated. The dynamic power dissipation of the LBFS CMOS buffer can be reduced by limited the gate voltage swing of the output inverter. Moreover, ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.