A Sub-1-V CMOS Bandgap using Forward Body Bias of the PMOS

... be used at variable source potentials, e.g. for differential input stages. Forward biasing the source-bulk junction with a fixed voltage over the full temperature range would lead to temperature dependant parasitic substrate current. The temperature dependant parasitic current is not a problem if th ...

... be used at variable source potentials, e.g. for differential input stages. Forward biasing the source-bulk junction with a fixed voltage over the full temperature range would lead to temperature dependant parasitic substrate current. The temperature dependant parasitic current is not a problem if th ...

What is the logic function of the following gate? Consider the

... 10. Consider the circuit below, left. Modules A and B have a delay of 20nsec and 65nsec at 5V and switch 30pF and 112pF, respectively. Each register has a delay of 4nsec and switches 0.2pF. Adding a pipeline register between A and B allows for reduction of the supply voltage while maintaining the t ...

... 10. Consider the circuit below, left. Modules A and B have a delay of 20nsec and 65nsec at 5V and switch 30pF and 112pF, respectively. Each register has a delay of 4nsec and switches 0.2pF. Adding a pipeline register between A and B allows for reduction of the supply voltage while maintaining the t ...

n-well - ECE "HUB"

... Self-heating effect: Thermal insulation is provided by the oxide surface. Heat dissipation is not efficient. This happens only when there is logic switching in the device. ...

... Self-heating effect: Thermal insulation is provided by the oxide surface. Heat dissipation is not efficient. This happens only when there is logic switching in the device. ...

Paper Title (use style: paper title)

... Dynamically adjusting the power-clock voltage to comply with constant-current charging results in adiabaticcharging effect[2]. The power clock supply charges the load capacitor adiabatically during the time it is ramping up and allows the load capacitor energy to recycle back when it is ramping down ...

... Dynamically adjusting the power-clock voltage to comply with constant-current charging results in adiabaticcharging effect[2]. The power clock supply charges the load capacitor adiabatically during the time it is ramping up and allows the load capacitor energy to recycle back when it is ramping down ...

Low Power Design and Simulation of 7T SRAM Cell using

... same chip, very effectively in leakage problem. The highthreshold transistors can partially decreased sub threshold leakage current, while the low-threshold transistors are used for high performance and Stability. Multiple-threshold voltages can be achieved by the following methods. V-C. Multiple ch ...

... same chip, very effectively in leakage problem. The highthreshold transistors can partially decreased sub threshold leakage current, while the low-threshold transistors are used for high performance and Stability. Multiple-threshold voltages can be achieved by the following methods. V-C. Multiple ch ...

Interfacing to MM74HC High-Speed CMOS Logic Interfacing to

... pulls up, it can go no higher than two diode voltage drops below VCC due to Q2 and D2. So when operating with a 5V supply, the TTL output cannot go much higher than about 3.5V. Figure 1 shows an LSTTL gate, which has an output structure formed by Q2 and Q4. As the LSTTL output goes high, these two t ...

... pulls up, it can go no higher than two diode voltage drops below VCC due to Q2 and D2. So when operating with a 5V supply, the TTL output cannot go much higher than about 3.5V. Figure 1 shows an LSTTL gate, which has an output structure formed by Q2 and Q4. As the LSTTL output goes high, these two t ...

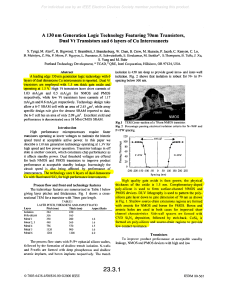

Intel 130nm CMOS

... High performance microprocessors require faster P+iPW spacing. transistorsoperatingat lower voltagesto maintain the historic speed trend at acceptable active power. In this paper we describea 130nm generationtechnology operatingat 1.3V for high speedand low power operation.Transistor leakagein off s ...

... High performance microprocessors require faster P+iPW spacing. transistorsoperatingat lower voltagesto maintain the historic speed trend at acceptable active power. In this paper we describea 130nm generationtechnology operatingat 1.3V for high speedand low power operation.Transistor leakagein off s ...

Document

... With optimized dual-phase-shift modulation strategies, zero voltage switching (ZVS) is achieved for both the primary- and secondary-side power MOSFETs in a wide load range. The reverse recovery problem of rectifying diodes is eliminated as well. Leakage inductances of the transformers are utilized f ...

... With optimized dual-phase-shift modulation strategies, zero voltage switching (ZVS) is achieved for both the primary- and secondary-side power MOSFETs in a wide load range. The reverse recovery problem of rectifying diodes is eliminated as well. Leakage inductances of the transformers are utilized f ...

Low-distortion low-voltage operational transconductance amplifier

... Introduction: Recent research shows a high demand for highly linear operational transconductance amplifiers (OTAs) with an aim to reduce total harmonic distortion (THD) [1–4]. However, most of these linearisation techniques may present important drawbacks such as reduced effective transconductance an ...

... Introduction: Recent research shows a high demand for highly linear operational transconductance amplifiers (OTAs) with an aim to reduce total harmonic distortion (THD) [1–4]. However, most of these linearisation techniques may present important drawbacks such as reduced effective transconductance an ...

Transistors

... • Physically implanted channel: An n-channel depletion type MOSFET has an n-type silicon region connecting the n+ source and drain regions at the top of the p-type substrate. • The channel depth and its conductivity can be controlled by Vgs in exactly the same manner as in the enhancement-type devic ...

... • Physically implanted channel: An n-channel depletion type MOSFET has an n-type silicon region connecting the n+ source and drain regions at the top of the p-type substrate. • The channel depth and its conductivity can be controlled by Vgs in exactly the same manner as in the enhancement-type devic ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.