ES_LPC2420 Errata sheet LPC2420 Rev. 7.1 — 1 July 2012 Errata sheet

... Full-/low-speed signaling uses bit stuffing throughout the packet without exception. If the receiver sees seven consecutive ones anywhere in the packet, then a bit stuffing error has occurred and the packet should be ignored. The time interval just before an EOP is a special case. The last data bit ...

... Full-/low-speed signaling uses bit stuffing throughout the packet without exception. If the receiver sees seven consecutive ones anywhere in the packet, then a bit stuffing error has occurred and the packet should be ignored. The time interval just before an EOP is a special case. The last data bit ...

- Lion Precision

... called by the equivalent name Peak-to-Valley) is critically important to understanding the absolute sensor performance. Analog methods of measuring these values include special meters and visual interpretation of an oscilloscope display. In the digitized world, these values are calculated by capturi ...

... called by the equivalent name Peak-to-Valley) is critically important to understanding the absolute sensor performance. Analog methods of measuring these values include special meters and visual interpretation of an oscilloscope display. In the digitized world, these values are calculated by capturi ...

Evaluation Board User Guide UG-293

... the board, DVDD. This should also have a 1 A current capability and can be combined with DRVDD with little or no degradation in performance. To operate the evaluation board using the SPI and alternate clock options, a separate 3.3 V analog supply is needed in addition to the other supplies. This 3.3 ...

... the board, DVDD. This should also have a 1 A current capability and can be combined with DRVDD with little or no degradation in performance. To operate the evaluation board using the SPI and alternate clock options, a separate 3.3 V analog supply is needed in addition to the other supplies. This 3.3 ...

Chapter 4 Inverter speed and propagation delay - Ping-Pong

... propagation delay can be defined at other voltage levels. Also defined in this figure is the rise and fall times, tr and tf, respectively. The rise and fall times are usually measured between the 10% and 90% levels, or between the 20% and 80% levels as in the figure. A simplified illustration of the ...

... propagation delay can be defined at other voltage levels. Also defined in this figure is the rise and fall times, tr and tf, respectively. The rise and fall times are usually measured between the 10% and 90% levels, or between the 20% and 80% levels as in the figure. A simplified illustration of the ...

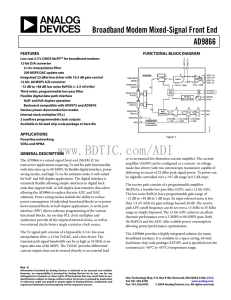

AD9865

... (RxPGA), a tunable low-pass filter (LPF), and a 10-bit ADC. The low noise RxPGA has a programmable gain range of −12 dB to +48 dB in 1 dB steps. Its input referred noise is less than 3 nV/rtHz for gain settings beyond 36 dB. The receive path LPF cutoff frequency can be set over a 15 MHz to 35 MHz ra ...

... (RxPGA), a tunable low-pass filter (LPF), and a 10-bit ADC. The low noise RxPGA has a programmable gain range of −12 dB to +48 dB in 1 dB steps. Its input referred noise is less than 3 nV/rtHz for gain settings beyond 36 dB. The receive path LPF cutoff frequency can be set over a 15 MHz to 35 MHz ra ...

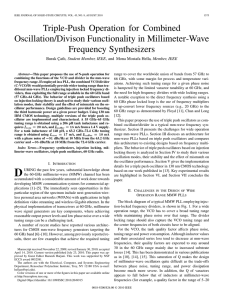

Triple-Push Operation for Combined Oscillation/Divison

... “divided” signal is already present at the output of the fundamental oscillator. For example, in the case of the shown 3-push 60 GHz oscillator, a 20 GHz signal is available from the core oscillators which enables the direct use of just static dividers with wide operation range compared to Miller or ...

... “divided” signal is already present at the output of the fundamental oscillator. For example, in the case of the shown 3-push 60 GHz oscillator, a 20 GHz signal is available from the core oscillators which enables the direct use of just static dividers with wide operation range compared to Miller or ...

NI USB-6001/6002/6003 User Guide

... DIFF/RSE MUX—The mode selector multiplexer selects between differential mode (DIFF) and referenced single-ended (RSE) measurement mode. ...

... DIFF/RSE MUX—The mode selector multiplexer selects between differential mode (DIFF) and referenced single-ended (RSE) measurement mode. ...

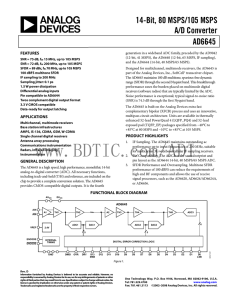

AD9866

... The Tx signal path consists of a bypassable 2×/4× low-pass interpolation filter, a 12-bit TxDAC, and a line driver. The transmit path signal bandwidth can be as high as 34 MHz at an input data rate of 80 MSPS. The TxDAC provides differential current outputs that can be steered directly to an externa ...

... The Tx signal path consists of a bypassable 2×/4× low-pass interpolation filter, a 12-bit TxDAC, and a line driver. The transmit path signal bandwidth can be as high as 34 MHz at an input data rate of 80 MSPS. The TxDAC provides differential current outputs that can be steered directly to an externa ...

Aerospace Anodizing Total Quality Improvement (TQI) Activation

... the proven success in San Diego along with other quality aerospace process facilities in Southern California. We will now share our tartaric / oxalic / citric blended addition, for all Type IC, II, IIB and III hard anodize, as Type 123. This will be the way of the future – and for now, the future is ...

... the proven success in San Diego along with other quality aerospace process facilities in Southern California. We will now share our tartaric / oxalic / citric blended addition, for all Type IC, II, IIB and III hard anodize, as Type 123. This will be the way of the future – and for now, the future is ...

AD7470 数据手册DataSheet下载

... The conversion process and data acquisition are controlled using standard control inputs, allowing easy interfacing to microprocessors or DSPs. The input signal is sampled on the falling edge of CONVST, and conversion is also initiated at this point. BUSY goes high at the start of conversion and goe ...

... The conversion process and data acquisition are controlled using standard control inputs, allowing easy interfacing to microprocessors or DSPs. The input signal is sampled on the falling edge of CONVST, and conversion is also initiated at this point. BUSY goes high at the start of conversion and goe ...

Integrated Circuits Lab-EE0313

... The differential amplifier eliminates the need for an emitter bye-pass capacitor. So, differential amplifier is used as an input stage in op-amp ICs ...

... The differential amplifier eliminates the need for an emitter bye-pass capacitor. So, differential amplifier is used as an input stage in op-amp ICs ...

a 1.75 MSPS, 4 mW 10-Bit/12-Bit Parallel ADCs AD7470/AD7472

... The conversion process and data acquisition are controlled using standard control inputs, allowing easy interfacing to microprocessors or DSPs. The input signal is sampled on the falling edge of CONVST, and conversion is also initiated at this point. BUSY goes high at the start of conversion and goe ...

... The conversion process and data acquisition are controlled using standard control inputs, allowing easy interfacing to microprocessors or DSPs. The input signal is sampled on the falling edge of CONVST, and conversion is also initiated at this point. BUSY goes high at the start of conversion and goe ...

AD5222 数据手册DataSheet 下载

... active inputs are clock (CLK), CS and up/down (U/D). While the MODE, and DACSEL pins control common updates or individual updates. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/DOWN counter register, Figure 30. Standard logic ...

... active inputs are clock (CLK), CS and up/down (U/D). While the MODE, and DACSEL pins control common updates or individual updates. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/DOWN counter register, Figure 30. Standard logic ...

AD6645-MIL 数据手册DataSheet下载

... Digital output logic levels: DVCC = 3.3 V, CLOAD = 10 pF. Capacitive loads >10 pF degrades performance. ...

... Digital output logic levels: DVCC = 3.3 V, CLOAD = 10 pF. Capacitive loads >10 pF degrades performance. ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.