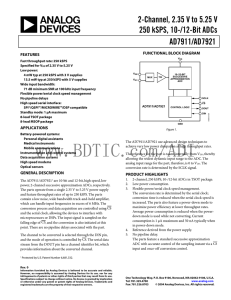

AD7911 数据手册DataSheet下载

... the AD7911/AD7921 and framing the serial data transfer. Data Out. Logic output. The conversion result from the AD7911/AD7921 is provided on this output as a serial data stream. The bits are clocked out on the falling edge of the SCLK signal. For the AD7921, the data stream consists of two leading ze ...

... the AD7911/AD7921 and framing the serial data transfer. Data Out. Logic output. The conversion result from the AD7911/AD7921 is provided on this output as a serial data stream. The bits are clocked out on the falling edge of the SCLK signal. For the AD7921, the data stream consists of two leading ze ...

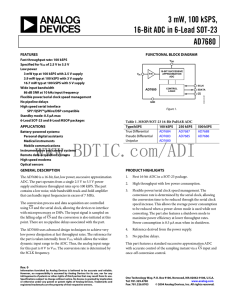

3 mW, 100 kSPS, 16-Bit ADC in 6-Lead SOT-23 AD7680

... The conversion process and data acquisition are controlled using CS and the serial clock, allowing the devices to interface with microprocessors or DSPs. The input signal is sampled on the falling edge of CS and the conversion is also initiated at this point. There are no pipeline delays associated ...

... The conversion process and data acquisition are controlled using CS and the serial clock, allowing the devices to interface with microprocessors or DSPs. The input signal is sampled on the falling edge of CS and the conversion is also initiated at this point. There are no pipeline delays associated ...

1.6 V, Micropower 12-Bit ADC AD7466-KGD Known Good Die FEATURES

... track-and-hold amplifier, which can handle input frequencies in excess of 3 MHz. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the device to interface with microprocessors or DSPs. The input signal is sampled on the falling edge of CS, and the con ...

... track-and-hold amplifier, which can handle input frequencies in excess of 3 MHz. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the device to interface with microprocessors or DSPs. The input signal is sampled on the falling edge of CS, and the con ...

AN-873: Lock Detect on the ADF4xxx Family of

... When the phase error at the PFD inputs on five or more consecutive cycles is inside the 15 ns window, it considers the PLL to be in lock and outputs a logic high. When the phase error drifts outside of the loss of lock threshold (30 ns) on any subsequent PFD cycle, it registers an out-of-lock condit ...

... When the phase error at the PFD inputs on five or more consecutive cycles is inside the 15 ns window, it considers the PLL to be in lock and outputs a logic high. When the phase error drifts outside of the loss of lock threshold (30 ns) on any subsequent PFD cycle, it registers an out-of-lock condit ...

LTC2400 - 24-Bit µPower No Latency Delta-Sigma ADC in SO-8

... an order of magnitude. The part remains in the sleep state as long as CS is logic HIGH. The conversion result is held indefinitely in a static shift register while the converter is in the sleep state. Once CS is pulled low, the device begins outputting the conversion result. There is no latency in t ...

... an order of magnitude. The part remains in the sleep state as long as CS is logic HIGH. The conversion result is held indefinitely in a static shift register while the converter is in the sleep state. Once CS is pulled low, the device begins outputting the conversion result. There is no latency in t ...

Analog-to-Digital Conversion via Time

... Conventional voltage-mode analog-to-digital converters use voltage amplifiers, voltage comparators, and switch capacitor networks to perform their signal processing. When compared to digital circuitry, these analog circuit blocks consume significant power, occupy large silicon areas, and operate at ...

... Conventional voltage-mode analog-to-digital converters use voltage amplifiers, voltage comparators, and switch capacitor networks to perform their signal processing. When compared to digital circuitry, these analog circuit blocks consume significant power, occupy large silicon areas, and operate at ...

Overview C-Series: Low Noise, Fast, Blue-Sensitive Silicon

... A third option for simultaneous readout of the standard and fast outputs provides a DC coupled standard output signal, and preserves the ability to read out the fast output. The decoupling capacitor from the cathode to 0V is critical to provide a return path for the fast output. This circuit is used ...

... A third option for simultaneous readout of the standard and fast outputs provides a DC coupled standard output signal, and preserves the ability to read out the fast output. The decoupling capacitor from the cathode to 0V is critical to provide a return path for the fast output. This circuit is used ...

SEL-451-Based Autosynchronizer Data Sheet

... systems. The SEL-451-5-based A25A is sold as a configuration and documentation disc. The user separately purchases the SEL-451-5 Protection, Automation, and Bay Control System Relay per the Model Option Table requirements detailed in this data sheet. Alternatively, the user can contact SEL Engineeri ...

... systems. The SEL-451-5-based A25A is sold as a configuration and documentation disc. The user separately purchases the SEL-451-5 Protection, Automation, and Bay Control System Relay per the Model Option Table requirements detailed in this data sheet. Alternatively, the user can contact SEL Engineeri ...

Journal of Applied Science and Agriculture

... An A/D converter is the circuit which converts a continuous analog signal into a discrete digital signal. The power consumption of the A/D converter accounts for a large part of power consumption of the digital devices. Among others, a flash type A/D converter is widely used for fast A/D conversion ...

... An A/D converter is the circuit which converts a continuous analog signal into a discrete digital signal. The power consumption of the A/D converter accounts for a large part of power consumption of the digital devices. Among others, a flash type A/D converter is widely used for fast A/D conversion ...

Analysis of Random Dopant Fluctuations and Oxide

... cells such as SRAMs are becoming more vulnerable to process variations. In this paper, process variation susceptibility of a L1 cache design in 16nm technology node has been analysed in detail. The aim is to characterize the possible errors with multiple process variations. We have designed a 32KB c ...

... cells such as SRAMs are becoming more vulnerable to process variations. In this paper, process variation susceptibility of a L1 cache design in 16nm technology node has been analysed in detail. The aim is to characterize the possible errors with multiple process variations. We have designed a 32KB c ...

PDF

... • Resistance of two via stacks at each end of M1 wire equivalent to about 0.1 mm wire (~20 Ω) • Resistance of two via stacks at each end of M6 wire about the same as 1 mm narrow M6 wire (~60 Ω)!!! • Use multiple vias in parallel to reduce effective contact ...

... • Resistance of two via stacks at each end of M1 wire equivalent to about 0.1 mm wire (~20 Ω) • Resistance of two via stacks at each end of M6 wire about the same as 1 mm narrow M6 wire (~60 Ω)!!! • Use multiple vias in parallel to reduce effective contact ...

Control of a DC/DC Converter Using FlexPWM`s Force

... This section describes the implementation of this control and details the configuration of each peripheral used for this function. ...

... This section describes the implementation of this control and details the configuration of each peripheral used for this function. ...

Wires - Massachusetts Institute of Technology

... • Resistance of two via stacks at each end of M1 wire equivalent to about 0.1 mm wire (~20 ) • Resistance of two via stacks at each end of M6 wire about the same as 1 mm narrow M6 wire (~60 )!!! • Use multiple vias in parallel to reduce effective contact ...

... • Resistance of two via stacks at each end of M1 wire equivalent to about 0.1 mm wire (~20 ) • Resistance of two via stacks at each end of M6 wire about the same as 1 mm narrow M6 wire (~60 )!!! • Use multiple vias in parallel to reduce effective contact ...

ACS1790T - Semtech

... generate outputs locked to an external reference source or standalone for standard frequency generation for common applications. The circuit includes an integrated VCO, loop filter, phase-and-frequency detector and output dividers. The default power-up mode is definable by pin settings and once oper ...

... generate outputs locked to an external reference source or standalone for standard frequency generation for common applications. The circuit includes an integrated VCO, loop filter, phase-and-frequency detector and output dividers. The default power-up mode is definable by pin settings and once oper ...

Kinetis K40: 72MHz Cortex-M4 up to 288KB Flash 100/121pin

... – USB full-/low-speed On-the-Go controller with onchip transceiver ...

... – USB full-/low-speed On-the-Go controller with onchip transceiver ...

Unit: 1 – Binary Systems and Logic Circuits

... The binary number system is a positional weighted system. The base or radix of this number system is 2. Hence, it has two independent symbols. The base itself cannot be a symbol. The symbols used are 0 & 1. A binary digit is called a bit. A binary number consists of a sequence of bits, each of which ...

... The binary number system is a positional weighted system. The base or radix of this number system is 2. Hence, it has two independent symbols. The base itself cannot be a symbol. The symbols used are 0 & 1. A binary digit is called a bit. A binary number consists of a sequence of bits, each of which ...

NCP1256 - Low Power Offline PWM Current

... • Current−mode operation with internal slope compensation: implementing peak current mode control at a fixed 65−kHz or 100−kHz frequency, the NCP1256 includes an internal slope compensation signal whose level will cover most of offline design cases. Additional ramp can be added via a simple scheme a ...

... • Current−mode operation with internal slope compensation: implementing peak current mode control at a fixed 65−kHz or 100−kHz frequency, the NCP1256 includes an internal slope compensation signal whose level will cover most of offline design cases. Additional ramp can be added via a simple scheme a ...

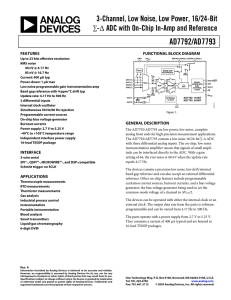

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16/24-Bit ∑

... CS falling edge to DOUT/RDY active time DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V SCLK active edge to data valid delay4 DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V Bus relinquish time after CS inactive edge ...

... CS falling edge to DOUT/RDY active time DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V SCLK active edge to data valid delay4 DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V Bus relinquish time after CS inactive edge ...

LTC1286/LTC1298 - Micropower Sampling 12

... Analog and Reference ................ – 0.3V to VCC + 0.3V Digital Inputs ......................................... – 0.3V to 12V Digital Output ............................. – 0.3V to VCC + 0.3V ...

... Analog and Reference ................ – 0.3V to VCC + 0.3V Digital Inputs ......................................... – 0.3V to 12V Digital Output ............................. – 0.3V to VCC + 0.3V ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.