* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Journal of Applied Science and Agriculture

Pulse-width modulation wikipedia , lookup

Power engineering wikipedia , lookup

Rotary encoder wikipedia , lookup

Electrical ballast wikipedia , lookup

Three-phase electric power wikipedia , lookup

Time-to-digital converter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Current source wikipedia , lookup

Electrical substation wikipedia , lookup

Alternating current wikipedia , lookup

Surge protector wikipedia , lookup

Stray voltage wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage regulator wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage optimisation wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Television standards conversion wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Mains electricity wikipedia , lookup

Power inverter wikipedia , lookup

Integrating ADC wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

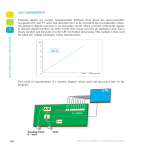

Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 AENSI Journals Journal of Applied Science and Agriculture ISSN 1816-9112 Journal home page: www.aensiweb.com/JASA A Size Reduction Technique for an A/D Converter Using Neuron CMOS Inverters 1 1 2 Yujiro Harada, 2Kei Eguchi, 1Kuniaki Fujimoto Course of Information Engineering, The Graduate School of Industrial Engineering, Tokai University, Japan. Faculty of Engineering, Department of Information Electronics, Fukuoka Institute of Technology, Japan. ARTICLE INFO Article history: Received 25 June 2014 Received in revised form 8 July 2014 Accepted 10 August May 2014 Available online 30 August 2014 Keywords: A/D converter neuron CMOS inverter low power consumption ABSTRACT Background: The power consumption of the A/D converter accounts for a large part of power consumption of the digital devices. Among A/D converters, a flash type A/D converter is widely used for fast A/D conversion. However, the flash type A/D converter requires 2n-1 analog comparators to achieve resolution of n-bits. Therefore, power consumption, circuit scale and layout area of the A/D converter exponentially increase in proportion to the resolution. To solve this problem, we proposed an A/D converter using neuron CMOS inverters in past studies. However, according to the increase of the resolution, the layout area of this A/D converter becomes very large. Objective: To solve the problem that the layout area becomes very large, a novel circuit topology for an A/D converter using neuron CMOS inverters is proposed in this paper. The circuit scale of the proposed A/D converter is a half of that of the conventional A/D converter using neuron CMOS inverters, because the single neuron CMOS inverter in the proposed A/D converter judges two voltage levels. Results: We confirmed the validity of the circuit design of the A/D converter in the SPICE simulation. Also, we fabricated an IC chip of the proposed A/D converter, and we confirmed the validity of the circuit design of the A/D converter in the experimental result of the IC chip. In the previous work, the layout area of the quantizer part of the proposed circuit was 0.7mm2 and layout area of encoder part was 0.13mm2. On the other hand, in the proposed A/D converter, the layout of the quantizer part is 0.32mm2 and layout area of the encoder part is 0.11mm2. This result shows that the layout area of the proposed A/D converter is about a half of that of the conventional A/D converter. Conclusion: In this paper, we proposed the A/D converter using neuron CMOS inverters that judge two voltage levels. Through SPICE simulations and experiments concerning the fabricated IC chip, we confirmed the validity of circuit design of the proposed A/D converter. Furthermore, we showed that the circuit scale of the proposed A/D converter is a half of the circuit scale of the conventional A/D converter. © 2014 AENSI Publisher All rights reserved. To Cite This Article: Yujiro Harada, Kei Eguchi, Kuniaki Fujimoto, A Size Reduction Technique for an A/D Converter Using Neuron CMOS Inverters. J. Appl. Sci. & Agric., 9(11): 132-137, 2014 INTRODUCTION An A/D converter is the circuit which converts a continuous analog signal into a discrete digital signal. The power consumption of the A/D converter accounts for a large part of power consumption of the digital devices. Among others, a flash type A/D converter is widely used for fast A/D conversion (Uyttenhove et al. (2003) and Wu et al. (2009)). By comparing an analog circuit input voltage and a reference voltage, the output of the flash type A/D converter is determined. In the flash type A/D converter, the reference voltage is usually realized by using resistor voltage dividers. However, the flash type A/D converter requires 2n-1 analog comparators to achieve resolution of n-bits. Therefore, circuit scale and layout area of the A/D converter exponentially increase in proportion to the resolution. Furthermore, power consumption also exponentially increases. To solve this problem, we proposed an A/D converter using neuron CMOS inverters in past studies (Sato et al. (2013) and Shibata et al. (1992)). The power consumption of our A/D converter is smaller than that of the conventional A/D converter using analog comparators. Also, the resistor voltage divider is not required in our A/D converter. However, according to the increase of the resolution, the layout area of this A/D converter becomes very large. To solve this problem, a novel circuit topology for an A/D converter using neuron CMOS inverters is proposed in this paper. The circuit scale of the proposed A/D converter is a half of that of the conventional A/D converter using neuron CMOS inverters, because the single neuron CMOS inverter in the proposed A/D converter judges two voltage levels. Also, number of inputs of an encoder part becomes a half of that of the conventional A/D converter. Therefore, circuit scale and power consumption of the encoder part can be reduced. Corresponding Author: Yujiro Harada, Course of Information Engineering, The Graduate School of Industrial Engineering, Tokai University, Kumamoto, Japan. Tel: +81-386-2653 E-mail: [email protected] 133 Yujiro Harada et al, 2014 Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 Methodology: First, we describe the previously proposed flash type A/D converter using neuron CMOS inverters and its problem. Figure 1 shows the circuit configuration of the conventional flash type A/D converter using neuron CMOS inverters with a resolution of n-bits. This circuit is constituted like a generally flash type A/D converter by a quantizer part and an encoder part. In Figure 1, CMOSi(i=1 ~ 2n-1-1, 2n-1+1 ~ 2n-1) is a neuron CMOS inverter, and CMOS2n-1 is a CMOS inverter, Vin is the analog input voltage, and VDD is the supply voltage. The A/D conversion of this circuit is achieved by using a variable threshold voltage characteristic of neuron CMOS inverters. However, if the resolution increases, the layout area becomes large due to capacitors Ci. To solve this problem, the proposed circuit is constituted by making two stage of the conventional circuit constitution. Encoder Quantizer VDD V1 C1 C0 CMOS1 VDD C2 n-1 -1 C0 V2n-1-1 CMOS2n-1-1 VDD VIN Vout1 Vout2 V2 n-1 CMOS2n-1 Vout n VDD C0 n-1 C2 +1 V2n-1+1 CMOS2n-1+1 VDD C0 n C2 -1 V2n-1 CMOS2n-1 Fig. 1: Circuit configuration of the conventional flash type A/D converter using neuron CMOS inverters. Figure 2 shows the circuit configuration of the proposed A/D converter using neuron CMOS inverters. In Figure 2, CMOSj (j=1~2n-1-1) is a neuron CMOS inverter, and N is a CMOS inverter, Vin is the analog input voltage, and VDD is the supply voltage. The capacitance C0 and Cj between the floating gate and the input terminal of CMOSj are designed to satisfy the following conditions: C0 = 2 n −1 Cu (1) C j = (2n−1 − j )Cu (2) 134 Yujiro Harada et al, 2014 Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 In (1) and (2), Cu is a unit of capacitance. Figure 3 shows the circuit configuration of the neuron CMOS inverter CMOSj and its equivalent circuit in the proposed A/D converter. In Figure 3, the capacitance C0 is connected to the analog input voltage Vin, and capacitance Cj is connected to V2n-1. When the initial charge of the neuron CMOS inverter CMOSj is "0", the floating gate voltage Vfj of CMOSj is written as V fj = VinC0 + V2n −1 C j + VDDCFN (3) Ctotal Quantizer Encoder VDD C0 V1 CMOS1 C1 Vout1 VDD Vin Vout2 C0 Vj CMOSj Cj Vout n VDD C0 N V2n-1-1 CMOS2n-1-1 C2n-1-1 V2n-1 Fig. 2: Circuit configuration of the proposed A/D converter. VDD Vin V2n-1 VDD C0 Vin C0 Vj Cj CMOSj (a)Neuron CMOS inverter Vj V2n-1 CMOSj Cj (b)Equivalent circuit Fig. 3: Circuit configuration of the neuron CMOS inverter and its equivalent circuit. In (3), the total capacitance Ctotal is expressed as Ctotal = C0 + C j + CFP + C FN (4) 135 Yujiro Harada et al, 2014 Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 In (3) and (4), CFP is the capacitance between the floating gate and p-type region, and CFN is the capacitance between the floating gate and n-type region. We design CFP and CFN to become (Fujimoto (2013)) C FP = C FN (5) The threshold voltage of CMOSj for the floating gate is designed to be VDD/2 that is the center of the supply voltage. The quantizer output Vj of CMOSj is expressed as VDD 0;V fj ≥ 2 Vj = V VDD ;V fj < DD 2 (6) Therefore, from (1), (2), (5), and (6), Vj is represented by VDD 2n −1 − j 0 ; V ≥ + (VDD − 2V2n −1 ) in 2 2n Vj = n −1 VDD ;Vin < VDD + 2 − j (VDD − 2V n −1 ) 2 2 2n V2 n-1 (7) In (7), V2n-1 is the output of the inverter N. If the threshold voltage of the inverter N is designed to be VDD/2, is expressed as V2 n−1 VDD 0;Vin ≥ 2 = V VDD ;Vin < DD 2 (8) From (8), when the analog input voltage Vin is lower than VDD/2, the output of the inverter N becomes the supply voltage VDD. In this case, the quantizer output voltage Vj is expressed as follows: j 0;Vin ≥ 2n VDD Vj = j VDD ;Vin < n VDD 2 (9) On the other hand, when the analog input voltage Vin is higher than VDD/2, the output of the inverter N becomes 0V. In this case, the quantizer output voltage Vj is expressed as follows: j 0;Vin ≥ VDD − 2 n VDD Vj = j VDD ;Vin < VDD − n VDD 2 (10) From (9) and (10), the quantizer output voltage Vj is expressed as j Vin ≥ VDD − n VDD 2 0; VDD j > Vin ≥ n VDD 2 2 Vj = j V VDD − n VDD > VIN ≥ DD 2 2 VDD ; j VDD > Vin 2n (11) 136 Yujiro Harada et al, 2014 Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 From (11), when the analog input voltage Vin gradually increases from 0V to VDD, the quantizer output voltage Vj changes from a high level to a low level in the order of V1 whenever Vin increases VDD/2n. When the analog input voltage is beyond VDD/2, the output of inverter N becomes 0V, and all quantizer output voltage Vj changes to high level. Furthermore, whenever Vin increases VDD/2nV, the quantizer output voltage Vj changes from a high level to a low level in the order of V2n-1-1 in the opposite direction. Therefore, we can get the A/D conversion result with n-bits by inputting the quantizer output voltage Vj into the encoder part. Results: Figure 4 shows the simulation result of the proposed A/D converter using the neuron CMOS inverters with 4-bits. In the SPICE simulation, the supply voltage VDD was set to 5V and the analog input voltage Vin is applied a triangle wave of 50kHz from 0V to VDD. In Figure 4, the outputs of neuron CMOS inverter CMOSj are V7 from V1, the output of inverter N is V8, and Vout4 from Vout1 are the conversion result that Vout1 is MSB and Vout4 is LSB. From Figure 4, we can confirm the validity of the circuit design. Analog input Vin V1 V2 V3 Output of the qantizer V4 V5 V6 V7 V8 Vout1 Output of the AD converter Vout2 Vout3 Vout4 Fig. 4: Simulation results of the proposed A/D converter. Analog input Vin V1 V2 V3 Output of the qantizer V4 V5 V6 V7 V8 Vout1 Output of the AD converter Vout2 Vout3 Vout4 Fig. 5: Experimental results of the proposed A/D converter. 137 Yujiro Harada et al, 2014 Journal of Applied Science and Agriculture, 9(11) Special 2014, Pages: 132-137 We fabricated an IC chip of the proposed A/D converter using neuron CMOS inverters with 4-bits at “The 3th Novel Device Design & Fabrication Contest in Hibikino” held at the Semiconductor Center in Kitakyushu Science and Research Park. This IC chip was fabricated using 2μm CMOS process. Figure 5 shows the experimental result of the proposed A/D converter. In the experiment using the IC chip, the supply voltage VDD was set to 5V and the analog input voltage Vin is applied a triangle wave of 50kHz from 0V to VDD. A unit of capacitance Cu was designed 80fF. As Figure 5 shows, the validity of the IC fabrication can be confirmed. Discussion: From Figures 1 and 3, we showed that the number of elements of the proposed A/D converter is a half of the number of elements of the conventional A/D converter. In the previous work (Sato et al. (2013)), the layout area of the quantizer part of the proposed circuit was 0.7mm2 and layout area of encoder part was 0.13mm2. On the other hand, in the proposed A/D converter, the layout of the quantizer part is 0.32mm2 and layout area of the encoder part is 0.11mm2. This result shows that the layout area of the proposed A/D converter is about a half of that of the conventional A/D converter. Conclusion: In this paper, we proposed the A/D converter using neuron CMOS inverters that judge two voltage levels. Through SPICE simulations and experiments concerning the fabricated IC chip, we confirmed the validity of circuit design of the proposed A/D converter. Furthermore, we showed that the circuit scale of the proposed A/D converter is a half of the circuit scale of the conventional A/D converter. In a future, we plan to compare the operating speed and the power consumption between the proposed A/D converter and the conventional A/D converter. REFERENCES Sato, Y., M. Yoshida, Y. Harada, K. Fujimoto, 2013. Flash AD Converter using Neuron CMOS Inverter, IEICE Transactions on Electronics, J96-C: 552-553. Shibata, T. and T. Ohmi, 1992. A functional MOS transistor featuring gate-level weighted sum and threshold operations, IEEE Transactions on Electron Devices, 54: 1444-1455. Fujimoto, K., 2013. Japan Patent Kokai, 2013-37737. Uyttenhove, K. and M. Steyaert, A 1.8-V 6-bit 1.3-GHz-flash ADC in 0.25μm CMOS. IEEE Journal of Solid-State Circuits, 38: 1115-1122. Wu, L., F. Huang, Y. Gao, Y. Wang, J. Cheng, 2009. A 42mW 2GS/s 4-bit flash ADCi in 0.18-μm CMOS. International Conference on Wireless Communication and Signal Proceeding, pp: 1-5.