lecture 240 – simulation and measurements of

... Example 1 Simulation of the CMOS Op Amp of Ex. 6.3-1. VDD = 2.5V The op amp designed in Example 6.3M3 M4 M6 1 and shown in Fig. 6.3-3 is to be analyzed ...

... Example 1 Simulation of the CMOS Op Amp of Ex. 6.3-1. VDD = 2.5V The op amp designed in Example 6.3M3 M4 M6 1 and shown in Fig. 6.3-3 is to be analyzed ...

TS3004 - Silicon Labs

... The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of informa ...

... The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of informa ...

Design Guide VT82C694X Apollo Pro133A with VT82C686A South

... 2.2.1.1 ATX Form Factor for Slot-1 System ................................................................................................................... 10 2.2.1.2 Micro ATX Form Factor for Slot-1 System............................................................................................ ...

... 2.2.1.1 ATX Form Factor for Slot-1 System ................................................................................................................... 10 2.2.1.2 Micro ATX Form Factor for Slot-1 System............................................................................................ ...

UM0355

... the voltage using a trimmer. The voltage level is displayed on a 3-digit display. The LVD will automatically hold the MCU in reset state while the voltage is below the safe threshold. No need for an external reset circuit so more savings in board space and components. ...

... the voltage using a trimmer. The voltage level is displayed on a 3-digit display. The LVD will automatically hold the MCU in reset state while the voltage is below the safe threshold. No need for an external reset circuit so more savings in board space and components. ...

AC WATT/WATTHOUR & VAR/VARHOUR TRANSDUCERS OSI GH-

... true power and a relay closure or TTL pulse output calibrated in terms of Watthours of energy consumption by the load. Accuracy is ±0.2% of reading. A Model VGH VAR/VARhour transducer provides an analog output proportional to time-averaged instantaneous reactive power and a relay closure or TTL puls ...

... true power and a relay closure or TTL pulse output calibrated in terms of Watthours of energy consumption by the load. Accuracy is ±0.2% of reading. A Model VGH VAR/VARhour transducer provides an analog output proportional to time-averaged instantaneous reactive power and a relay closure or TTL puls ...

M43067982

... rectifier circuits, followed by the second stage of dcdc converter using high frequency transformer. These two stages of power conversion has the problem of power quality in terms of harmonic current at ac mains, voltage distortion, reduced power factor, high peak factor and require a large size of ...

... rectifier circuits, followed by the second stage of dcdc converter using high frequency transformer. These two stages of power conversion has the problem of power quality in terms of harmonic current at ac mains, voltage distortion, reduced power factor, high peak factor and require a large size of ...

Design Considerations for Avoiding Timing Errors during High

... the LVDS pairs of ADC outputs and the FPGA inputs should be matched within 5 mm of each other for better performance. Mismatch creates a phase difference between voltages along the signal pairs and radiates as common mode noise. All LVDS signals need to be routed as 100-Ω differential lines. The ove ...

... the LVDS pairs of ADC outputs and the FPGA inputs should be matched within 5 mm of each other for better performance. Mismatch creates a phase difference between voltages along the signal pairs and radiates as common mode noise. All LVDS signals need to be routed as 100-Ω differential lines. The ove ...

AN118 - Silicon Labs

... ware routine that takes a set of samples and To increase the effective number of bits (ENOB), averages (filters) them for the result. the signal is oversampled, or sampled by the ADC at a rate that is higher than the system’s required Increasing the Resolution of sampling rate, fs. The required samp ...

... ware routine that takes a set of samples and To increase the effective number of bits (ENOB), averages (filters) them for the result. the signal is oversampled, or sampled by the ADC at a rate that is higher than the system’s required Increasing the Resolution of sampling rate, fs. The required samp ...

MM54C74 Dual D Flip-Flop

... The MM54C74/MM74C74 dual D flip-flop is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. Each flipflop has independent data, preset, clear and clock inputs and Q and Q outputs. The logic level present at the data input is transferred ...

... The MM54C74/MM74C74 dual D flip-flop is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. Each flipflop has independent data, preset, clear and clock inputs and Q and Q outputs. The logic level present at the data input is transferred ...

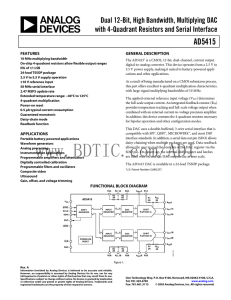

AD5415 数据手册DataSheet 下载

... register on the active edge of the subsequent clocks. In standalone mode, the serial interface counts the clocks, and data is latched into the shift register on the 16th active clock edge. Active Low Control Input. This pin clears the DAC output, input, and DAC registers. Configuration mode allows t ...

... register on the active edge of the subsequent clocks. In standalone mode, the serial interface counts the clocks, and data is latched into the shift register on the 16th active clock edge. Active Low Control Input. This pin clears the DAC output, input, and DAC registers. Configuration mode allows t ...

MONTONE.42 Operating Instructions

... • All devices must be connected to the mains using the three-cord power leads supplied with the system. Only supply electrical interfaces with the voltages and signals described in these instructions. • Do not use the device at extreme temperatures. Proper operation can only be guaranteed be ...

... • All devices must be connected to the mains using the three-cord power leads supplied with the system. Only supply electrical interfaces with the voltages and signals described in these instructions. • Do not use the device at extreme temperatures. Proper operation can only be guaranteed be ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.