LTC1286/LTC1298 - Micropower Sampling 12

... Analog and Reference ................ – 0.3V to VCC + 0.3V Digital Inputs ......................................... – 0.3V to 12V Digital Output ............................. – 0.3V to VCC + 0.3V ...

... Analog and Reference ................ – 0.3V to VCC + 0.3V Digital Inputs ......................................... – 0.3V to 12V Digital Output ............................. – 0.3V to VCC + 0.3V ...

AN13 - High Speed Comparator Techniques

... two functions. Because it is flat (AC currents travel along the surface of a conductor) and covers the entire area of the board, it provides a way to access a low inductance ground from anywhere on the board. Also, it minimizes the effects of stray capacitance in the circuit by referring them to gro ...

... two functions. Because it is flat (AC currents travel along the surface of a conductor) and covers the entire area of the board, it provides a way to access a low inductance ground from anywhere on the board. Also, it minimizes the effects of stray capacitance in the circuit by referring them to gro ...

Measurement Types in Machinery Monitoring

... imperial units (in/s2). For prediction measurements especially on antifriction bearings the accelerometer output in G’s is used to determine the bearing health. One method of doing this consists of mining the time series for high frequency stress content. Emerson uses a technique called PeakVueTM to ...

... imperial units (in/s2). For prediction measurements especially on antifriction bearings the accelerometer output in G’s is used to determine the bearing health. One method of doing this consists of mining the time series for high frequency stress content. Emerson uses a technique called PeakVueTM to ...

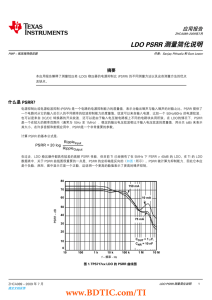

简化的 LDO PSRR 测量

... will make measurements moreLdifficult. The highest frequency that can VDC and from each other. be measured is determined by the self resonant frequencies of the L and C components. The L and C will create a high pass filter for VAC which will limit how low in frequency we can measure Fthe 1/ 2Ȇ ¥LC ...

... will make measurements moreLdifficult. The highest frequency that can VDC and from each other. be measured is determined by the self resonant frequencies of the L and C components. The L and C will create a high pass filter for VAC which will limit how low in frequency we can measure Fthe 1/ 2Ȇ ¥LC ...

MODEL 148A 20 MHz AM/FM/PM GENERATOR

... Set up the generator as for continuous operation (refer to paragraph 3.2.1). Switch to internal or external amplitude modulation. If internal, note that the carrier (main generator waveform) mean amplitude is decreased to half. This is to prevent clipping (overdriving the output amplifier) when the ...

... Set up the generator as for continuous operation (refer to paragraph 3.2.1). Switch to internal or external amplitude modulation. If internal, note that the carrier (main generator waveform) mean amplitude is decreased to half. This is to prevent clipping (overdriving the output amplifier) when the ...

A Nyquist-Rate Pixel-Level ADC for CMOS Image Sensors

... produce color NTSC video with only an external power supply and a crystal oscillator. This “system-on-chip” approach of combining the functional blocks of a multichip digital camera onto a single chip reduces the imaging system’s cost and power. However, it does not fully exploit the potential of in ...

... produce color NTSC video with only an external power supply and a crystal oscillator. This “system-on-chip” approach of combining the functional blocks of a multichip digital camera onto a single chip reduces the imaging system’s cost and power. However, it does not fully exploit the potential of in ...

DS3232M ±5ppm, I C Real-Time Clock with SRAM 2

... Figure 4 illustrates a single-supply configuration using VCC only, with the VBAT input grounded. When VCC < VPF, the RST output is asserted (active low). Temperature conversions are executed once per second. Figure 5 illustrates a single-supply configuration using VBAT only, with the VCC input groun ...

... Figure 4 illustrates a single-supply configuration using VCC only, with the VBAT input grounded. When VCC < VPF, the RST output is asserted (active low). Temperature conversions are executed once per second. Figure 5 illustrates a single-supply configuration using VBAT only, with the VCC input groun ...

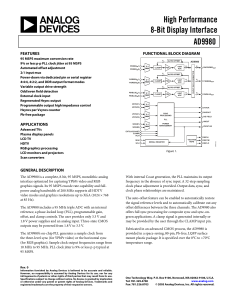

AD9980 VGA Input CODEC

... reference and provides the frequency reference for pixel clock generation. The logic sense of this pin can be automatically determined by the chip or manually controlled by Serial Register 0x12, Bits [5:4] (Hsync polarity). Only the leading edge of Hsync is used by the PLL; the trailing edge is used ...

... reference and provides the frequency reference for pixel clock generation. The logic sense of this pin can be automatically determined by the chip or manually controlled by Serial Register 0x12, Bits [5:4] (Hsync polarity). Only the leading edge of Hsync is used by the PLL; the trailing edge is used ...

AVR1005: Getting started with XMEGA

... The AVR® product portfolio has been expanded with the XMEGA family. Many ask if this is a new architecture and are uncertain how their experience with megaAVR transfers to AVR XMEGA. This document briefly introduces the similarities and differences between the two AVR families, and provides an overv ...

... The AVR® product portfolio has been expanded with the XMEGA family. Many ask if this is a new architecture and are uncertain how their experience with megaAVR transfers to AVR XMEGA. This document briefly introduces the similarities and differences between the two AVR families, and provides an overv ...

128 bit carry select adder using binary to excess-one

... 0.18-m CMOS process technology. The results analysis shows that the proposed CSLA structure is better than the regular CSLA. Keywords- Delay; Area; Array Multiplier, low power, VHDL Modeling & Simulation. I. INTRODUCTION Area and power reduction in data path logic systems are the main area of resear ...

... 0.18-m CMOS process technology. The results analysis shows that the proposed CSLA structure is better than the regular CSLA. Keywords- Delay; Area; Array Multiplier, low power, VHDL Modeling & Simulation. I. INTRODUCTION Area and power reduction in data path logic systems are the main area of resear ...

ics8543.pdf

... While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circui ...

... While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circui ...

Oscillators - Learn About Electronics

... It is the nature of a capacitor that when the voltage on one plate changes rapidly, the other plate also undergoes a similar rapid change, therefore as the right hand plate of C2 falls rapidly from supply voltage to almost zero, the left hand plate must fall in voltage by a similar amount. With TR1 ...

... It is the nature of a capacitor that when the voltage on one plate changes rapidly, the other plate also undergoes a similar rapid change, therefore as the right hand plate of C2 falls rapidly from supply voltage to almost zero, the left hand plate must fall in voltage by a similar amount. With TR1 ...

2102-282 Digital Electronics - IC Design & Application Research Lab.

... Setup time, tsetup is the time that the data inputs (D) must be valid before the clock transition 0 to 1 transition for a positive edge-triggered device 1 to 0 transition for a negative edge-triggered device ...

... Setup time, tsetup is the time that the data inputs (D) must be valid before the clock transition 0 to 1 transition for a positive edge-triggered device 1 to 0 transition for a negative edge-triggered device ...

Wire delay - Ping-Pong

... In another CMOS process, the wire fringing field capacitance along the wire sidewalls cannot be neglected. Being 35 aF/m (including both sidewalls) it must be added to the wire bottom plate capacitance of 30 aF/m2. The wire sheet resistance is 0.10 /square as in the previous example. a. Calculate ...

... In another CMOS process, the wire fringing field capacitance along the wire sidewalls cannot be neglected. Being 35 aF/m (including both sidewalls) it must be added to the wire bottom plate capacitance of 30 aF/m2. The wire sheet resistance is 0.10 /square as in the previous example. a. Calculate ...

ML405 User Guide

... XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners. ...

... XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners. ...

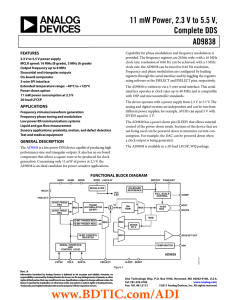

11 mW Power, 2.3 V to 5.5 V, Complete DDS AD9838

... capacitor should be connected between AVDD and AGND. Positive Power Supply for the Digital Section. DVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling capacitor should be connected between DVDD and DGND. The digital circuitry operates from a 2.5 V power supply. This 2.5 V is generated fr ...

... capacitor should be connected between AVDD and AGND. Positive Power Supply for the Digital Section. DVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling capacitor should be connected between DVDD and DGND. The digital circuitry operates from a 2.5 V power supply. This 2.5 V is generated fr ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.