IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... Low-Power Pulse Triggered Flip Flip-Flop Design with Conditional Pulse Enhancement Method type P-FF, the pulse generator is a built-in logic of the TSPC latch design, and no explicit pulse signals are generated. In an explicit-type P-FF, the designs of pulse generator and latch are separate [11]. I ...

... Low-Power Pulse Triggered Flip Flip-Flop Design with Conditional Pulse Enhancement Method type P-FF, the pulse generator is a built-in logic of the TSPC latch design, and no explicit pulse signals are generated. In an explicit-type P-FF, the designs of pulse generator and latch are separate [11]. I ...

document

... The pixel is shown in Fig. 17.7.2a; it comprises a SPAD, implemented as a p+/pwell/deep n-well junction, a TDC based on the architecture reported in [5], and a memory. The TDC is composed of a ring oscillator (RO) with fast start-up, shown in Fig. 17.7.2b, that is activated by the SPAD through falli ...

... The pixel is shown in Fig. 17.7.2a; it comprises a SPAD, implemented as a p+/pwell/deep n-well junction, a TDC based on the architecture reported in [5], and a memory. The TDC is composed of a ring oscillator (RO) with fast start-up, shown in Fig. 17.7.2b, that is activated by the SPAD through falli ...

DC1164 - High Speed ADC Signal Source Evaluation Kit Quick Start

... J2: Signal Output – Outputs the filtered signal. Connect this port to the analog input of the ADC demo board. ...

... J2: Signal Output – Outputs the filtered signal. Connect this port to the analog input of the ADC demo board. ...

Introductin to Sequential logic

... Wait until combinational logic has finished and result it stable... Then sample the output value and save... Feed the saved output back to the input of the combinational logic Make sure the saved output can’t change Key idea: we sample the result at the right time, i.e. when it is ready ...

... Wait until combinational logic has finished and result it stable... Then sample the output value and save... Feed the saved output back to the input of the combinational logic Make sure the saved output can’t change Key idea: we sample the result at the right time, i.e. when it is ready ...

Final Presentation

... New wireless applications : Wearable body sensor node (19uW) running on harvested energy – small devices, long lifetimes! ...

... New wireless applications : Wearable body sensor node (19uW) running on harvested energy – small devices, long lifetimes! ...

Design of a Restartable Crystal Controlled Clock for Use in... Asynchronous, Locally Synchronous Design Methodology

... not an efficient technique because reducing clock speeds reduces the performance of the system. The second approach often used is to place two synchronizers in between the asynchronous input and the rest of the synchronous circuit. This technique decreases the probability of both synchronizers going ...

... not an efficient technique because reducing clock speeds reduces the performance of the system. The second approach often used is to place two synchronizers in between the asynchronous input and the rest of the synchronous circuit. This technique decreases the probability of both synchronizers going ...

paper

... The ADC and DAC each need Nyquist bandwidth of 4 GHz so that the circuits do not limit link performance. Capacitance is minimized at the I/O for high data bandwidth. No electrostatic discharge (ESD) structures are included in the design. The input and output each use four pads, with two converters c ...

... The ADC and DAC each need Nyquist bandwidth of 4 GHz so that the circuits do not limit link performance. Capacitance is minimized at the I/O for high data bandwidth. No electrostatic discharge (ESD) structures are included in the design. The input and output each use four pads, with two converters c ...

Signal to noise ratio (SNR)

... like ISI (inter symbol interference) jitter, comes from system consideration and are not part of this presentation. Since most jitter in a electrical circuit is caused by thermal noise, which has a Gaussian distribution, random jitter also follows a Gaussian distribution (Normal distribution). Jitte ...

... like ISI (inter symbol interference) jitter, comes from system consideration and are not part of this presentation. Since most jitter in a electrical circuit is caused by thermal noise, which has a Gaussian distribution, random jitter also follows a Gaussian distribution (Normal distribution). Jitte ...

IBM Presentation - Rochester Institute of Technology

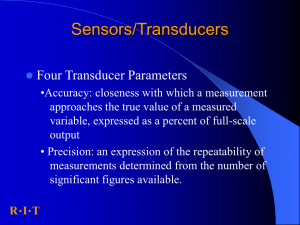

... variable, expressed as a percent of full-scale output • Precision: an expression of the repeatability of measurements determined from the number of ...

... variable, expressed as a percent of full-scale output • Precision: an expression of the repeatability of measurements determined from the number of ...

Manual - Mad Professor

... • There are no noise reduction circuits, which keeps decay of echo as natural as possible. • The direct signal path is short and made with analog amplifiers with no filtering. • There should be no distortion or tone coloration as long as input level is in range below maximum allowed. • The echo sign ...

... • There are no noise reduction circuits, which keeps decay of echo as natural as possible. • The direct signal path is short and made with analog amplifiers with no filtering. • There should be no distortion or tone coloration as long as input level is in range below maximum allowed. • The echo sign ...

Type here the title of your Paper

... the position of operation of the switching device (closed or open position) and on the position of the device inside the substation or bay. It could be demonstrated that the influence of the ...

... the position of operation of the switching device (closed or open position) and on the position of the device inside the substation or bay. It could be demonstrated that the influence of the ...

PDF

... can do the operation of serialization but practically we don’t get the proper serialization. The different timing requirements (set up time, hold time, other types of delay) put stringent limitations on the design. The basic internal blocks are shown in fig-3. Two flip-flops , one latch and one mux ...

... can do the operation of serialization but practically we don’t get the proper serialization. The different timing requirements (set up time, hold time, other types of delay) put stringent limitations on the design. The basic internal blocks are shown in fig-3. Two flip-flops , one latch and one mux ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.