altmann

... player, master or reference clock) via TOSLINK, ST, Cinch or XLR connection, then does a complete signal reconditioning, and then transmits the „new born“ signal via „Direct Clock Injection“ into the Cinch, XLR or BNC input of the receiver (fe. AD or DA converter). ...

... player, master or reference clock) via TOSLINK, ST, Cinch or XLR connection, then does a complete signal reconditioning, and then transmits the „new born“ signal via „Direct Clock Injection“ into the Cinch, XLR or BNC input of the receiver (fe. AD or DA converter). ...

Experiment to verify Faraday’s Law of Electro-Magnetic- Induction 7EM

... - why the signal generator is set to “triangle” output and why you must maintain a constant peak voltage - why resistor R is needed - how your results verify Faraday’s law (assuming that they do !) Your report should also include a diagram showing what you saw on the oscilloscope screen. 4. The expe ...

... - why the signal generator is set to “triangle” output and why you must maintain a constant peak voltage - why resistor R is needed - how your results verify Faraday’s law (assuming that they do !) Your report should also include a diagram showing what you saw on the oscilloscope screen. 4. The expe ...

ICS1561A Differential Output PLL Clock Generator Integrated Circuit

... The ICS1561A has a VDDO pin which is the supply of +5 volt power to all output stages. This pin should be connected to the power plane (or bus) using standard high frequency decoupling practice. This decoupling consists of a low series inductance bypass capacitor, using the shortest leads possible, ...

... The ICS1561A has a VDDO pin which is the supply of +5 volt power to all output stages. This pin should be connected to the power plane (or bus) using standard high frequency decoupling practice. This decoupling consists of a low series inductance bypass capacitor, using the shortest leads possible, ...

PDF

... Skew Sources and Cures Systematic skew due to manufacturing variation can be mostly trimmed out with adaptive deskewing circuitry – cross chip skews of <10ps reported ...

... Skew Sources and Cures Systematic skew due to manufacturing variation can be mostly trimmed out with adaptive deskewing circuitry – cross chip skews of <10ps reported ...

meres stilusfajl

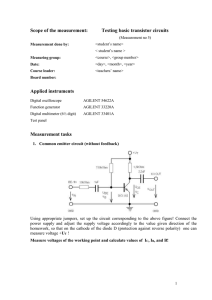

... Using appropriate jumpers, set up the circuit corresponding to the above figure! Connect the power supply and adjust the supply voltage accordingly to the value given direction of the homework, so that on the cathode of the diode D (protection against reverse polarity) one can measure voltage +UT ! ...

... Using appropriate jumpers, set up the circuit corresponding to the above figure! Connect the power supply and adjust the supply voltage accordingly to the value given direction of the homework, so that on the cathode of the diode D (protection against reverse polarity) one can measure voltage +UT ! ...

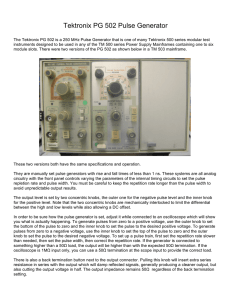

Tektronix PG 502 Pulse Generator

... repletion rate and pulse width. You must be careful to keep the repetition rate longer than the pulse width to avoid unpredictable output results. The output level is set by two concentric knobs, the outer one for the negative pulse level and the inner knob for the positive level. Note that the two ...

... repletion rate and pulse width. You must be careful to keep the repetition rate longer than the pulse width to avoid unpredictable output results. The output level is set by two concentric knobs, the outer one for the negative pulse level and the inner knob for the positive level. Note that the two ...

Synchronous Vs Asynchronous Design

... for such an element to complete, allowing robust mutual exclusion. Also, since there is no clock with which signals must be synchronized, asynchronous circuits more gracefully accommodate inputs from the outside world, which are by nature asynchronous. With all of the potential advantages of asynchr ...

... for such an element to complete, allowing robust mutual exclusion. Also, since there is no clock with which signals must be synchronized, asynchronous circuits more gracefully accommodate inputs from the outside world, which are by nature asynchronous. With all of the potential advantages of asynchr ...

Creating your design: Timing (part2)

... Knowledge like “this block will not run in two modes at the same time” is often crucial to determine false paths So: you need to specify them by hand… ...

... Knowledge like “this block will not run in two modes at the same time” is often crucial to determine false paths So: you need to specify them by hand… ...

ISSCC 2015 / SESSION 25 / RF FREQUENCY GENERATION FROM

... This paper presents an all-digital phase-locked loop (PLL) using a voltage-domain digitization realized by an analog-to-digital converter (ADC). It consists of an 18b Class-C digitally-controlled oscillator (DCO), 4b comparator, digital loop filter (DLF), and frequency-locked loop (FLL). Implemented ...

... This paper presents an all-digital phase-locked loop (PLL) using a voltage-domain digitization realized by an analog-to-digital converter (ADC). It consists of an 18b Class-C digitally-controlled oscillator (DCO), 4b comparator, digital loop filter (DLF), and frequency-locked loop (FLL). Implemented ...

A Solution for Peak EMI Reduction with Spread Spectrum Clock

... TIMING SAFE is a trademark of Semiconductor Components Industries, LLC (SCILLC). ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, rep ...

... TIMING SAFE is a trademark of Semiconductor Components Industries, LLC (SCILLC). ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, rep ...

current meter and integrator - High Voltage Engineering Europa B.V.

... The HVEE current-meter and integrator is a precision instrument designed for current- and dose measurements on particle accelerators, isotope separators, etc. The current-meter and integrator has an analog meter (60 mm scale) for current measurements and a digital readout (6 digits) for dose measure ...

... The HVEE current-meter and integrator is a precision instrument designed for current- and dose measurements on particle accelerators, isotope separators, etc. The current-meter and integrator has an analog meter (60 mm scale) for current measurements and a digital readout (6 digits) for dose measure ...

EH22815819

... The proposed design is an attempt to design a low power, half-swing clock double edge triggered flip-flop. Clock and clock circuitry generally consume more power, so Halfswing clock system reduces clock power. Clocked C2MOS latches suitable for half-swing clock. But Transmission-gates latch output i ...

... The proposed design is an attempt to design a low power, half-swing clock double edge triggered flip-flop. Clock and clock circuitry generally consume more power, so Halfswing clock system reduces clock power. Clocked C2MOS latches suitable for half-swing clock. But Transmission-gates latch output i ...

SG2525 SG3525 smps pwm

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

Analog to Digital (A/D) Conversion

... otherwise it is increased using an algorithm to home in on the matching value. – When the counter step size is within the tolerance desired (usually 1 count) then conversion is stopped and the digital value being output to the D/A is output ...

... otherwise it is increased using an algorithm to home in on the matching value. – When the counter step size is within the tolerance desired (usually 1 count) then conversion is stopped and the digital value being output to the D/A is output ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.