The Fridge Door Monitoring and Alarm Circuits

... 0 disables it turning the bell off. The signal from the computer is held in the transparent d-type flip-flop and the computer turns the bell on and off by changing the value in the flip-flop. The value from the flip-flop cannot drive the bell directly, as it cannot provide sufficient current to ring ...

... 0 disables it turning the bell off. The signal from the computer is held in the transparent d-type flip-flop and the computer turns the bell on and off by changing the value in the flip-flop. The value from the flip-flop cannot drive the bell directly, as it cannot provide sufficient current to ring ...

DS2401 - Maxim

... When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The ROM search proces ...

... When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The ROM search proces ...

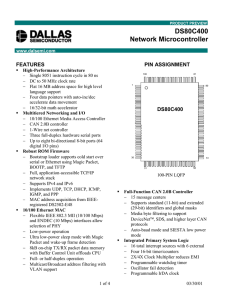

DS80C400-FCS - Maxim Integrated Products, Inc.

... The DS80C400 is a fast 8051-compatible microcontroller. The redesigned core executes 8051 instructions up to 3 times faster than the original for the same crystal speed. The DS80C400 supports a maximum crystal speed of 50 MHz, resulting in a minimum instruction cycle time of 80 ns. The DS80C400 util ...

... The DS80C400 is a fast 8051-compatible microcontroller. The redesigned core executes 8051 instructions up to 3 times faster than the original for the same crystal speed. The DS80C400 supports a maximum crystal speed of 50 MHz, resulting in a minimum instruction cycle time of 80 ns. The DS80C400 util ...

Intro to distributed OS

... Symmetric multiprocessors (SMP) - multiple processors sharing memory such that the access from each processor to each memory location takes the same amount of time (uniform access) advantages: single - processor applications can run without modifications (OS has to be modified. Why? How?) inter- ...

... Symmetric multiprocessors (SMP) - multiple processors sharing memory such that the access from each processor to each memory location takes the same amount of time (uniform access) advantages: single - processor applications can run without modifications (OS has to be modified. Why? How?) inter- ...

Interface Architecture Development

... • Each shared memory system has the ability to tap into the shared memory of other systems • Provides a demand-based service, unlike message passing where scheduled transfers take place. • Networks can serve hundreds of nodes (message passing architecture is limited to 32 nodes) • Includes communica ...

... • Each shared memory system has the ability to tap into the shared memory of other systems • Provides a demand-based service, unlike message passing where scheduled transfers take place. • Networks can serve hundreds of nodes (message passing architecture is limited to 32 nodes) • Includes communica ...

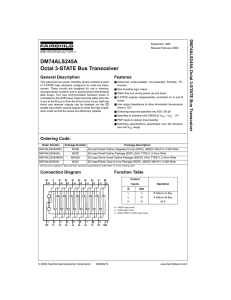

DM74ALS245A Octal 3-STATE Bus Transceiver

... of 3-STATE logic elements configured as octal bus transceivers. These circuits are designed for use in memory, microprocessor systems and in asynchronous bidirectional data buses. Two way communication between buses is controlled by the (DIR) input. Data transmits either from the A bus to the B bus ...

... of 3-STATE logic elements configured as octal bus transceivers. These circuits are designed for use in memory, microprocessor systems and in asynchronous bidirectional data buses. Two way communication between buses is controlled by the (DIR) input. Data transmits either from the A bus to the B bus ...

University of Ottawa - School of Electrical Engineering and

... In order to keep track if write operation was performed for each cache line. In case it was performed, the cache line has to be written back to the main memory. ...

... In order to keep track if write operation was performed for each cache line. In case it was performed, the cache line has to be written back to the main memory. ...

Technology Guide 1

... • Contain a small CPU, memory, and an input/output device that allow these “computers” to used in everyday activities such as person identification and banking ...

... • Contain a small CPU, memory, and an input/output device that allow these “computers” to used in everyday activities such as person identification and banking ...

Elektromotus CAN bus topology recommendations v0.2 rc2 Table of

... CAN transceiver (transceivers delay) and bus line delay per unit length (typ. 5 ns/m). All in all, biggest limitation to the bus length is the transceivers propagation delay. Unterminated drop lines do cause signal reflections. Although reflected signals will disappear once they arrive at a bus term ...

... CAN transceiver (transceivers delay) and bus line delay per unit length (typ. 5 ns/m). All in all, biggest limitation to the bus length is the transceivers propagation delay. Unterminated drop lines do cause signal reflections. Although reflected signals will disappear once they arrive at a bus term ...

Tests e supporto per l’ENEA GRID

... Tests and tools for ENEA GRID Performance test: HPL (High Performance Linpack) Network monitoring ...

... Tests and tools for ENEA GRID Performance test: HPL (High Performance Linpack) Network monitoring ...

LAB 3 Timer Interrupt and ADC

... • Digital input pins subject to shoot-through current – Input voltages between VIL and VIH cause shoot-through if input is allowed to “float” (left unconnected) ...

... • Digital input pins subject to shoot-through current – Input voltages between VIL and VIH cause shoot-through if input is allowed to “float” (left unconnected) ...

MArex OS III FOr A SAFe JOurney

... AVENTICS control systems can be found on all type of ships around the world. Work vessels with classification, passenger liners, coastal cargo ships and even yachts rely on engineering expertise Made in Germany. Regardless of which propulsion concept is required – the reversing gear system, the cont ...

... AVENTICS control systems can be found on all type of ships around the world. Work vessels with classification, passenger liners, coastal cargo ships and even yachts rely on engineering expertise Made in Germany. Regardless of which propulsion concept is required – the reversing gear system, the cont ...

Primii pasi in PSS/E Hardware and Software Requirements

... The Load button is used to create a load on a bus. When the load item is selected, the cursor changes to a crosshair. The load is started by placing the crosshair on the bus and pressing the left mouse button. The mouse is then dragged to where the load symbol is to appear and released. The Generato ...

... The Load button is used to create a load on a bus. When the load item is selected, the cursor changes to a crosshair. The load is started by placing the crosshair on the bus and pressing the left mouse button. The mouse is then dragged to where the load symbol is to appear and released. The Generato ...

Error Frame - Personal Web Pages

... • With conventional systems, data is exchanged by means of dedicated signal lines. • But this is becoming increasingly difficult and expensive as control functions become ever more complex. • In case of complex control systems in particular, the number of connections cannot be increased much further ...

... • With conventional systems, data is exchanged by means of dedicated signal lines. • But this is becoming increasingly difficult and expensive as control functions become ever more complex. • In case of complex control systems in particular, the number of connections cannot be increased much further ...

network topology

... Bus Topology is a bus pattern connecting the computers and other devices to the same communication line. All devices are connected in a line to a central cable, called the bus or backbone. There is no central computer or server. The data transmission is bidirectional. ...

... Bus Topology is a bus pattern connecting the computers and other devices to the same communication line. All devices are connected in a line to a central cable, called the bus or backbone. There is no central computer or server. The data transmission is bidirectional. ...

Product Specification - The UK Mirror Service

... memory or an I/O device. The addressed I/O device or memory should use this signal to gate data onto the CPU data bus. Tri-state output, active low. WR indicates that the CPU data bus holds valid data to be stored in the addressed memory or I/O device. ...

... memory or an I/O device. The addressed I/O device or memory should use this signal to gate data onto the CPU data bus. Tri-state output, active low. WR indicates that the CPU data bus holds valid data to be stored in the addressed memory or I/O device. ...

Mapping the Data Warehouse to a Multiprocessor Architecture

... • The goals of linear performance and scalability can be satisfied by parallel hardware architectures, parallel operating systems, and parallel DBMSs. • Parallel hardware architectures are based on Multi-processor systems designed as a Shared-memory model, Shared-disk model or distributed-memory mod ...

... • The goals of linear performance and scalability can be satisfied by parallel hardware architectures, parallel operating systems, and parallel DBMSs. • Parallel hardware architectures are based on Multi-processor systems designed as a Shared-memory model, Shared-disk model or distributed-memory mod ...

Denial of Service Attack on Automotive CAN Networks

... the problem of CAN is. The messages on CAN bus are transmitted to all nodes and each node would accept the message by identifier it is interested or drop it. No one consider where the packet comes from. That is, no authentication is applied during CAN network. It is fine in the past because the netw ...

... the problem of CAN is. The messages on CAN bus are transmitted to all nodes and each node would accept the message by identifier it is interested or drop it. No one consider where the packet comes from. That is, no authentication is applied during CAN network. It is fine in the past because the netw ...

CHAPTER 1: Introduction of Computers

... information on the World Wide Web. Other manufacturers of chips (such as Cyrix) produce chips of similar power and capabilities. The faster the processor in a computer, the more quickly the computer will perform operations. The most common type of memory that most users are familiar with is ‘main me ...

... information on the World Wide Web. Other manufacturers of chips (such as Cyrix) produce chips of similar power and capabilities. The faster the processor in a computer, the more quickly the computer will perform operations. The most common type of memory that most users are familiar with is ‘main me ...

CSCE590/822 Data Mining Principles and Applications

... Do not scale down well to “starter” systems Rely on custom VLSI for processors ...

... Do not scale down well to “starter” systems Rely on custom VLSI for processors ...

CAN BUS (Controller Area Network)

... transmitter inserts a stuff bit with a compliment value into the bit stream. The receivers remove this stuff bit. ...

... transmitter inserts a stuff bit with a compliment value into the bit stream. The receivers remove this stuff bit. ...

PJ2325572560

... interfaced to the web server by pressing a button provided in the web page. However, many different protocols used in the industrial control network make the system performance inefficiency and handicap the application flexibility of field bus devices. In Control area network interface special softw ...

... interfaced to the web server by pressing a button provided in the web page. However, many different protocols used in the industrial control network make the system performance inefficiency and handicap the application flexibility of field bus devices. In Control area network interface special softw ...

Lecture 3 - Network hardware, Ethernet

... • So yes, there is a network-speed path to CPU registers… • We may need to "touch" each word of data in a network packet multiple times to process it (possibly because it needs to be copied from one buffer to another). – If memory/CPU path crossed n times, then effective throughput is 3200 Mbps/n. – ...

... • So yes, there is a network-speed path to CPU registers… • We may need to "touch" each word of data in a network packet multiple times to process it (possibly because it needs to be copied from one buffer to another). – If memory/CPU path crossed n times, then effective throughput is 3200 Mbps/n. – ...

Network Topoogies

... whose address matches the address attached with the data. In this topology only one computer can send data at a time. Therefore, the speed of a network reduces as the number of computer attached to the bus increase. ...

... whose address matches the address attached with the data. In this topology only one computer can send data at a time. Therefore, the speed of a network reduces as the number of computer attached to the bus increase. ...

Bus (computing)

In computer architecture, a bus (related to the Latin ""omnibus"", meaning ""for all"") is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components (wire, optical fiber, etc.) and software, including communication protocols.Early computer buses were parallel electrical wires with multiple connections, but the term is now used for any physical arrangement that provides the same logical functionality as a parallel electrical bus. Modern computer buses can use both parallel and bit serial connections, and can be wired in either a multidrop (electrical parallel) or daisy chain topology, or connected by switched hubs, as in the case of USB.