* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download The Fridge Door Monitoring and Alarm Circuits

Survey

Document related concepts

Transcript

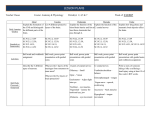

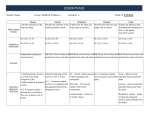

The Fridge Door Monitoring and Alarm Circuits The system is designed to monitor the state of a fridge door, open or closed, and to set an alarm bell ringing if the door is open. Input Interface The circuit to monitor the door is presented first and is shown to the right. A mechanically operated switch on the door opens and closes with the door to make or break a circuit. The voltage at point A is 5V if the switch and the door are open, when no current flows through the switch; the voltage is 0V if the switch and the door are closed and a current flows. The resistor in the circuit is purely to limit the current flow when the switch is closed. 9V Data bus line used determines which bit of register gets value of “A”. Data Bus Line A Gnd Read The voltage at A is passed to the input of the tri-state driver the output of which drives one of the Data bus lines when the tri-state is enabled. To input the state of the fridge door requires the computer to enable the driver and read the value of the Data Bus into a register, where it can be analysed. Mechanical Door Switch Active low output Address Decoder AddressBus Address decoder logic defines address of interface This can be performed by the CPU executing an instruction such as:lw $8, 0($6) // where $6 holds the address assigned to the interface which generates a read cycle at the address specified and puts the data value read into the register. In this read cycle, the address from the instruction is sent on the Address bus and is analysed by address decoding logic at the input interface, which checks for the address assigned to the interface. If the decoding logic identifies the address, it activates its output by setting it low. When the read control signal goes active, as part of the read cycle, the OR gate has both inputs low and sets its output low enabling the tri-state driver. The driver drives the attached Data bus line with the value of A, 0 or 1. This value is held on the bus line and read into the CPU at the end of the read cycle, and then transferred into the destination register. The read control signal is then de-activated, disabling the tristate driver which ceases to drive the Data bus line. Which bit of the register the data value ends up in is determined by which Data bus line is attached to the tri-state driver. Once the value has been read other instructions can be executed to test the appropriate bit of the register to determine whether it is 0 or 1, i.e. whether the fridge door is open or closed. The input interface is accessed just as a memory during a read. The CPU does not need to treat a read of the input interface any differently from a read of a memory: it reads a data value from an address. 44 Output Interface The Output interface is shown in the figure. The bell circuit consists of the bell unit which rings when a current flows through it. The power transistor operates as a switch, which controls whether a current flows through the bell or not. A special "power" transistor is used which can handle the high current required to ring the bell. The power transistor is controlled by the output of the computer system: a 1 enables the transistor ringing the bell, a 0 disables it turning the bell off. The signal from the computer is held in the transparent d-type flip-flop and the computer turns the bell on and off by changing the value in the flip-flop. The value from the flip-flop cannot drive the bell directly, as it cannot provide sufficient current to ring the bell. Data bus line used determines which bit of register carries value for bell on/off. Data Bus Line D 9V Bell Power Transistor Q WE 0V WRITE Active low output Address Decoder Address Bus Address decoder logic defines address of interface An output value can be written into the flip-flop just as a value is written into a memory. The flip-flop write control is enabled during a write cycle generated by an instruction such as:sw $8, 0($6) // where $6 holds the address assigned to the interface As with the read interface the address is put on the address bus and is recognised by the address decoding logic in the same way as for the input interface, setting its output low. Next the data value is put on to the Data bus. When the write control signal goes active in the middle of the write cycle, both inputs of the OR-gate are low and its output goes low activating the write control input to the flipflop. The flip-flop is now enabled for writing and writes the data value from the Data bus line attached to its D input into the flip-flop. This value appears on the flip-flop output. After a delay the CPU sets the write control line inactive, de-activating the write signal to the flip-flop and setting the flip-flop into storage mode. The CPU then moves on to the next instruction, while the output interface holds the data value keeping the bell in the required state, ringing or not ringing. The Data bus line that is connected to the D input of the flip-flop of the interface determines which bit in the data value is written to the flip-flop. The circuit looks just the storage part of a memory. Again, the processor does not need to treat a write to the output interface any differently from a write to a memory: it just writes a data value to an address. The use of a flip-flop is required in order to hold the bell ringing for a long period so that the bell can be heard, i.e. the output value has to be held for long enough for it to be recognised by the receiver. A tri-state driver cannot be used as the data value would only be present for a fraction of the length of the write cycle, a few 10s of nano-seconds in a modern microprocessor. 45 Software to control the interface Flowchart for Fridge Door ENTRY Input Data - ‘0’ or ‘1’ from Fridge Door Switch (read from switch address) Check if ‘0’ - door Closed or ‘1’ - door Open Door Open ? yes no Set Bell to ring! Turn Bell off! (write 1 to bell address) A flowchart for the operation of the interfaces is shown. The input interface is read, the data value read in is checked to see if the door is open: if the door is open, the bell is turned on; if the door is closed the bell is turned off. The MIPS for this flowchart is shown. In this example both the input and output interfaces are attached to the least significant bit of the Data bus. (write 0 to bell address) Exit Flowchart for Fridge Door ENTRY Input Data - ‘0’ or ‘1’ from Fridge Door Switch (read from switch address) Check if ‘0’ - door Closed or ‘1’ - door Open Door Open ? yes no Set Bell to ring! Turn Bell off! (write 1 to bell address) (write 0 to bell address) Exit Of course, for this simple system, a computer is not really required, the door being open could be wired to ring a bell. However, it demonstrates the key factors in I/O circuits: tri-state drivers between the input interface and the Data bus; flip-flops between the Data bus and the output interface. I/O systems differ in the number of connections to the data bus, and the logic on the other side of the tristate drivers (for input interfaces) or of the flip-flops (for output interfaces). An advantage of a computer controlled interface is the ability to modify the operation of the system by modifying the program. Thus, for the fridge door, a programmable delay could be introduced to prevent the bell ringing as soon as you open the door, but allows a moderate time for access to the fridge, avoiding irritation to the user. 46