* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Differential Amplifiers

Cellular repeater wikipedia , lookup

Index of electronics articles wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Integrating ADC wikipedia , lookup

Oscilloscope types wikipedia , lookup

Oscilloscope history wikipedia , lookup

Audio power wikipedia , lookup

Power MOSFET wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Surge protector wikipedia , lookup

Power electronics wikipedia , lookup

Wilson current mirror wikipedia , lookup

Regenerative circuit wikipedia , lookup

Radio transmitter design wikipedia , lookup

Voltage regulator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Two-port network wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Rectiverter wikipedia , lookup

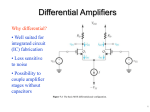

Differential Amplifiers

What is a Differential Amplifier ?

Some Definitions and Symbols

Differential Amplifier: A differential amplifier is an amplifier that amplifies the

difference between two voltages and rejects the average or common mode value

of the two voltages.

Symbol for a

Differential

Amplifier

v1

v2

vout

Differential-mode input voltage, vID , is the voltage difference between v1 and v2 .

Common-mode input voltage, vIC , is the average value of v1 and v2 .

Therefore

vID = v1 - v2

and

vIC = (v1 + v2) / 2

vID/2

vID/2

vIC

vout

The output voltage of the differential amplifier can be expressed in terms of its

differential-mode and common-mode input voltage as -

Vout = AVDvID + AVCvIC = AVD (v1-v2) + AVC(v1+v2)/2

Where

AVD = differential-mode voltage gain

AVC = common-mode voltage gain

Common mode rejection ration (CMRR)

CMRR =

AVD

AVC

CMRR - a measure of performance

For ideal diff Amp – AVC is zero and hence an infinite CMRR

Input Common-mode range (ICMR)

ICMR is the range of common-mode voltages over which the differential

amplifier continues to sense and amplify the difference signal with the same gain.

Typically , ICMR is defined as common-mode voltage range over which all

MOSFETs remain in the saturation region.

Offsets:

Output offset voltage (VOS(out)) : It is defined as the voltage which appears at

the output of the Diff Amp when the inputs terminal are shorted.

Input offset voltage (VOS(in)) : It is equal to the output offset voltage divided

by the differential voltage gain VOS = (VOS(out) / AVD)

LARGE SIGNAL ANALYSIS

VDD

iD1

iD2

M1

Ibias

M2

vG2

vG1

vGS1

M3

M4

vGS2

VBulk

ISS

CMOS differential amplifier using NMOS transistors

M3 and M4 are a typical implementation of current sink ISS.

Configuration of M1 and M2 is known as

source coupled pair.

Large signal analysis starts with the assumption that M1 and M2 are perfectly matched

Transconductance Characteristics of the Differential Amplifier

Defining Equations:

vID = vGS1-vGS2 = (2iD1/b)1/2 - (2iD2/b)1/2 and

Valid for vID < (2ISS/b)1/2

Solution of above equations:

ISS

ISS

iD1 =

+

2

2

bvID2

ISS

ISS = iD1 + iD2

b2

vID4

1/2

iD2 =

and

4ISS2

ISS

ISS

2

2

bvID2

b2 vID4

ISS

4ISS2

1/2

Differentiating iD1 w r t vID and setting vID=0V gives differential transconductance

of the Diff Amp as

gm = d(iD1)/d(vID) at [VID=0] = (bISS/4)1/2 = (K’1ISSW1/4L1)1/2

iD/ISS

1.0

0.8

0.6

0.4

iD1

iD2

(vID/(ISS/b)0.5)

0.2

1.414

0.0

1.414

Voltage Transfer Characteristics of the Differential Amplifier

VDD

iD3

M1

M4

M3

iD1

iD2

vGS1

vG1

iD4

iout

M2

vGS2

M5

vG2

ISS

Vbias

CMOS differential Amplifier using a current-mirror load

Differential-in, differential-out transconductance gmd is given as:

gmd = d(iout)/d(vID) at [VID=0] = (K’1ISSW1/L1)1/2 = Twice of gm

vout

Voltage Transfer Characteristics of the Diff Amp (cont.)

5

M4 active

Vout(volts)

4

M4 saturated

3

VIC=2V

2

M2 saturated

1

0

M2 active

-1

-0.5

0

0.5

1.0

vID(volts

)

Region of operation of the transistors:

M2 is saturated when,

vDS2 >= vGS2-VTN vout – VS1 >= VIC- 0.5vID – VS1 – VTN vout >= VIC – VTN

Where we have assumed that the region of transition for M2 is close to vID = 0V.

Similarly M4 is saturated when,

vSD4>= vSG4- !VTP! VDD- vout >= VSG4 - !VTP! vout =< VDD – VSG4 + !VTP!

Differential Amplifier Using p-channel Input MOSFETs

VDD

Vbias

M1

M5

iD1

IDD

iD2

M2

iout

vG1

M3

iD3

vG2

M4

iD4

Vout

Input Common Mode Range (ICMR)

ICMR is found by setting vID = 0 and varying vIC until one of the transistors leaves

the saturation region.

Highest Common Mode Voltage:

There are two paths from VIC to VDD –

(1) From G1 through M1 and M3 to VDD

and

(2) From G2 through M2 and M4 to VDD

For path (1),

VIC(max) = VG1(max) =VG2(max) = VDD – VSG3 –VDS1 (sat)+ VGS1

= VDD –VSG3 +VTN1

For path (2),

VIC(max)’ = VDD – VSD4(sat) – VDS2(sat) + VGS2

= VDD –VSD4(sat) +VTN2

………………… is more than the first case.

Therefore VIC(max) = VDD –VSG3 + VTN1

Lowest Common Mode Voltage:

VIC(min) = VDS5(sat) + VGS1 = VDS5(sat) + VGS2

We have assumed that VGS1 = VGS2 during changes in the input common mode voltage.

SMALL SIGNAL ANALYSIS

Analysis of the Differential-Mode of the Differential Amplifier

When both sides of the amplifier are perfectly matched then -

ac ground

D1=G3=D3=G4

rds1

G2

G1

S1= S2

vid

vg1

iout’

rds2

i

i

3

3

vg2

gm1vgs

rds3

D2=D4

1/gm3

1

vout

gm2vgs

rds5

S3

rds4

2

S4

Small signal model for the CMOS differential Amplifier (exact model)

Simplifies

to

Analysis of the Differential-Mode of the Differential Amplifier (cont.)

iout’

G2

G1

D1=G3=D3=G4

D2=D4

vid

vgs1

i

i

3

3

vgs2

gm1vgs1

rds1

rds3

1/gm3

gm2vgs2

rds2

rds4

S1=S2=S3=S4

Simplified equivalent model

Differential Transconductance:

We assume that the output is ac short.

iout’ = {(gm1gm3rp1)/(1+gm3rp1)}vgs1- gm2vgs2 = gm1vgs1 – gm2vgs2 =

gmdvid

Where gm1 = gm2 = gmd , rp1 = rds1!! rds3

in a short circuit.

and iout’ designates the output current

Analysis of the Differential-Mode of the Differential Amplifier (cont.)

To calculate unloaded differential voltage gain:

rout = 1/(gds2+gds4) = rds2 rds4

Therefore differential voltage gain:

Av = (vout/vin) = { gmd / (gds2+gds4) }

If we assume that all transistors are in saturation and replace the small signal parameters

of gm and rds in terms of their large-signal model equivalents, we achieve

Av = (vout/vin) =

(K’1ISSW1/L1)1/2

(l2 + l4)(ISS/2)

=

2

(l2 + l4)

K’1W1

ISSL1

1/2

Note that the small signal gain is inversely proportional to the square root of the bias current.

Common–Mode Analysis for the Current Mirror Load Differential Amplifier

In an ideal case when there are no mismatches, the current-mirror load rejects any

common-mode signal.

So the common-mode gain of the differential amplifier

with a current mirror load is ideally zero.

In order to show how to analyze the small signal, common-mode gain of the differential

amplifier, we will consider a different circuit.

Let’s see …

Common–Mode Analysis for the Differential Amplifier (an illustration)

Let us consider the circuit shown below:

VDD

VDD

M3

M3

M4

vo1

M4

vo1

vo

vo

2

2

v1

M1

v2

M1

M2

Vid/2

General circuit

M2

M5

Vid/2

ISS

Vbias

Differential-mode circuit

Differential-Mode Analysis:

vo1/vid = - (gm1/2gm3) and vo2 /vid = + (gm2 /2gm4)

Common–Mode Analysis for the Diff Amp (an illustration) …(cont.)

Common-mode analysis:

VDD

VDD

M3

M4

vo1

M3

vo

M4

vo1

2

2

v1

v2

M1

M1

M2

vic

M5

ISS

Vbias

General Circuit

vo

M2

ISS/2

ISS/2

M5/2

M5/2

Vbias

Common-mode circuit

vic

Common–Mode Analysis for the Diff Amp (an illustration) …(cont.)

Small-signal model for common-mode analysis gm1vgs1

vgs

1

vi

c

rds

2rds

rds

1

3

5

1/gm

vo1

3

For simplification let’s assume that rds1 is large and can be ignored.

vgs1 = vic – 2gm1rds5vgs1

The single ended output voltage, vo1 , as a function of vic is

vo1

vic

CMRR =

=-

(gm1/2gm3)

(gds5/2gm3)

gm1[rds3 (1/gm3)]

1 + 2gm1rds5

= gm1rds5

=-

(gm1/gm3)

1 + 2gm1rds5

= - (gds5/2gm3)

Frequency Response of the Differential Amplifier (differential-mode)

VDD

Cgs3 +

Cgs4

M3

Cbd

Cbd

M4

4

3

Cgd

4

Cgd

v1G1

M1

Cbd

Cbd

1

2

C

2

L

vout

vG2

M2

vGS1

Cgd

vGS2

M5

Vbias

After some approximations we will finally get -

Vout(s)

Vin(s)

=

gm1

gds2 + gds4

C2 = Cbd2 + Cbd4 + Cgd2 + CL

w2

s + w2

First order approximation

Where w2 = [(gds2 + gds4)/ C2]

Slew Rate of the Differential Amplifier

Slew Rate: Maximum output-voltage rate (either positive or negative)

For the differential amplifier with current mirror as loads,

SR =

ISS

C

Where C is the total capacitance connected

to the output node.

Note that slew rate can only occur when the differential input signal is large enough to cause

ISS to flow through only one of the differential input transistors.

For MOSFET differential amplifier SR can be + 2mV or more.

Solved Example: Design of a CMOS

Differential Amplifier with a Current Mirror Load

DESIGN CONSIDERATIONS:

Constraints:

Power Supply

Technology

Temperature

Specifications

Small-signal gain

Frequency response

ICMR

Slew Rate

Power Dissipation

WHAT IS DESIGN ?

The design in most CMOS circuits consists of an architecture represented by a

schematic, W/L values of transistors, and dc currents.

Av = gm1Rout

RELATIONSHIPS:

w-3dB = 1/RoutCL

VIC(max) = VDD – VSG3 + VTN1

VIC(min) = VDS5(sat) + VGS1 = VDS5(sat) + VGS2

SR = ISS/CL

Pdiss = (VDD – VSS) times all dc currents flowing from VDD to VSS

Design: continued

STEPS:

1. Choose I5 to satisfy the slew rate knowing CL or the power dissipation.

2. Check to see if Rout will satisfy the frequency response, if not change ISS

or modify circuit.

3. Design W3/L3 (W4/L4) to satisfy the upper ICMR.

4. Design W1/L1 (W2/L2) to satisfy the small signal differential gain.

5. Design W5/L5 to satisfy the lower ICMR.

6. Iterate where necessary.

EXAMPLE:

Specs:

VDD = -VSS = 2.5 V, SR > 10V/ms (CL = 5pF)

f-3dB > 100kHz (CL = 5pF), Av = 100V/V,

-1.5V < ICMR < 2V and Pdiss < 1mW.

Given parameters:

K’N = 110mA/V2, K’P = 50mA/V2 ,

VTN = 0.7 V, VTP = -0.7V, lN = 0.04V-1 , lP = 0.05V-1.

Design: continued

Solution

1. Slew rate gives, ISS > 50mA. Pdiss gives ISS < 200mA.

2. f-3dB Rout < 318kW. From here and using Rout=[2/((lN + lP)ISS], we get

ISS > 70mA. Let’s pick ISS = 100mA.

3. VIC(max) = VDD – VSG3 + VTN1 gives W3/L3 = (W4/L4) = 8

4. Av = 100V/V = gm1Rout

W1/L1 = (W2/L2) = 18.4

5. VIC(min) = VSS + VDS5(sat) + VGS1 W5/L5 = 300

6. Since W5/L5 is too large, we should increase W1/L1 to reduce VGS1 and allow

a smaller W5/L5. If W1/L1 = 40, then W5/L5 = 9.

Note: Here Av increases to 111.1 V/V, which should be Okay.

Thank You