* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Resource efficient implementation of PWM core on FPGAs

Survey

Document related concepts

Telecommunication wikipedia , lookup

Phase-locked loop wikipedia , lookup

UniPro protocol stack wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electronic engineering wikipedia , lookup

Opto-isolator wikipedia , lookup

Index of electronics articles wikipedia , lookup

Integrated circuit wikipedia , lookup

Power electronics wikipedia , lookup

Microprocessor wikipedia , lookup

Radio transmitter design wikipedia , lookup

Magnetic-core memory wikipedia , lookup

Transcript

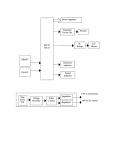

Resource efficient FPGA implementation of PWM core Sharmelee Thangjam, Lecturer, Department of Telecomm & IT, UIET, Panjab University, Chandigarh, India. PIN-160014 Tel: +91-1722541242 Email: [email protected] Dr Sanjay Attri, Assistant Professor, Department of ECE, NITTTR, Sector-26, Chandigarh, India. Tel: +91-1722791351 Email: [email protected] Dr B. S. Sohi, Director, UIET, Panjab University, Chandigarh, India. PIN-160014 Tel: +911722541242 Email: [email protected] Abstract As geometries shrink and device counts multiply, opportunities abound to do incredible things within the confines of a single chip. This breakthrough in silicon technology has, however, reached the point, where it is hard to design a complete system from scratch. The growing complexity of SoC(System-On-Chip) technology dramatically increases design loading and creates the needs for verified IP cores to simplify multifunctional chip designs. IP cores play a vital role in SoC development for three reasons. First, IP cores provide essential elements for any SoC design. Second, the growing complexity of SoC designs introduces an increasing demand for integrating more functionality and sophisticated IP cores on a chip. Third, designers need reusable IP cores to accelerate the design migration to smaller geometry chips. Core-based designs have the advantages of faster time-to-market, reduced place and route time with pre-placed cores, less engineering required with pre-designed cores and facilitate design re-use. This paper details a resource efficient implementation of a Pulse Width Modulator(PWM) core on Xilinx XC4003E FPGA. A prototyping board, built around the device, is used for the implementation of the above mentioned core. The PWM outputs a variable duty cycle at a fixed frequency. The core is designed to operate at a clock frequency of 4Mhz. The duty cycle of the PWM signal is controlled by a data value that is loaded via sixteen input switches provided on the prototyping board. The corresponding PWM signal is observed on one of the output pins of the XC4003E. In many of the PWM applications, the single bit digital output is subject to a low-pass filter that results in an analog output level. The output level is the analog equivalent of the digital PWM’s duty-cycle. The Synopsis WorkView Office CAD tool is used for the design purpose, starting from design entry, encompassing the functional simulation and synthesis phase and finally culminating in the optimized implementation on the target device, the XC4003E. The optimized implementation, in the form of bit-streams, is then downloaded onto the device, configuring the FPGA for the PWM function. The optimized implementation on the XC4003E is found to take up 33 flip-flops on the CLBs taking up a meager 16% of the total available flip-flops. Implementation results also indicate a maximum working frequency of 17.517 Mhz, if speed optimization is used. The remaining portion of the device can be used to integrate the rest of the circuitry in a SoC scenario, leading to a complete system on a small device. The PWM core developed in this way can be integrated into a complete system where PWM is required, as in applications requiring motor and motion control, robotics, data acquisition system, anti-lock braking systems etc. This approach makes use of the core to save development time while focusing engineering time and energy on those parts of the design that add value and differentiation to the product.