* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download MRFIC1859 Dual-Band/GSM 3.6 V Integrated Power Amplifier

Solar micro-inverter wikipedia , lookup

Wireless power transfer wikipedia , lookup

Electrical substation wikipedia , lookup

Electric power system wikipedia , lookup

Electrical ballast wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Power over Ethernet wikipedia , lookup

Distributed control system wikipedia , lookup

Utility frequency wikipedia , lookup

Power engineering wikipedia , lookup

History of electric power transmission wikipedia , lookup

Stray voltage wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Power inverter wikipedia , lookup

Audio power wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Power MOSFET wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage regulator wikipedia , lookup

Alternating current wikipedia , lookup

Voltage optimisation wikipedia , lookup

Buck converter wikipedia , lookup

Mains electricity wikipedia , lookup

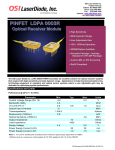

Order this document by MRFIC1859/D MRFIC1859 Dual-Band/GSM 3.6 V Integrated Power Amplifier The MRFIC1859 is a dual–band, single supply RF Power Amplifier for GSM900/DCS1800 hand held radios. The on–chip spur free voltage generator reduces the number of external components by eliminating the need for a negative voltage supply. The device output power can be controlled open loop without the use of directional coupler and detection diode. The MRFIC1859 is General Packet Radio Service (GPRS) compatible. The device is packaged in a TQFP–32EP with exposed backside pad allowing excellent electrical and thermal performance through a solderable contact. • • • • • DUAL–BAND GSM 3.6 V IPA SEMICONDUCTOR TECHNICAL DATA Single Positive Supply Solution Input/Output External Matching High Power and Efficiency Typical 3.6 V Characteristics: Pout = 36.2 dBm, PAE = 53% for GSM Pout = 34 dBm, PAE = 43% for DCS Crosstalk Harmonic Leakage of –27 dBm Typical (GSM) 32 1 (Scale 2:1) PLASTIC PACKAGE CASE 873E (TQFP–32EP) ORDERING INFORMATION Device MRFIC1859R2 Operating Temperature Range Package TC = –35 to 100°C TQFP–32EP Simplified Block Diagram D1G D2B B2B B1G B23G D2G InG OutG Negative and Positive Voltage Generator VSS VP VSC InD OutD B1D D1D D1B G2D B23D D2D This device contains 21 active transistors. Motorola, Inc. 2000 MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA Rev 4 1 MRFIC1859 PIN CONNECTIONS VSS D2B B2B OutD 32 31 30 29 OutD Out D OutD 28 27 OutD 26 25 24 B23D B23G 1 VP 2 23 D2D Gnd 3 22 D2D OutG 4 21 VSC OutG 5 20 G2D OutG 6 19 D1G OutG 7 18 B1G OutG 8 17 InG 9 10 11 12 13 14 15 16 M2G D2G D2G D2G D1D D1B B1D InD Exposed Pad (Gnd–on bottom) MAXIMUM RATINGS Symbol Value Unit Supply Voltage Rating VD1B,D2B VD1G,D2G, D3G,D1D, D2D,D3D 6.0 V RF Input Power InG, InD 12 dBm OutG OutD 38 36 TC –35 to 100 Tstg –55 to 150 °C RθJC 15 °C/W RF Output Power GSM Section DCS Section dBm Operating Case Temperature Range Storage Temperature Range Thermal Resistance, Junction to Case °C NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Recommended Operating Contitions or Electrical Characteristics tables. 2. Meets Human Body Model (HBM) ≤100 V and Machine Model (MM) ≤60 V. Additional ESD data available upon request. RECOMMENDED OPERATING CONDITIONS Characteristic Symbol Min Typ Max Unit VD1B,D2B VD1G,D2G, D3G,D1D, D2D,D3D 2.8 – 5.5 V Input Power GSM InG 3.0 – 10 dBm Input Power DCS InD 5.0 – 12 dBm Supply 2 MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 ELECTRICAL CHARACTERISTICS (VD1B, D2B = 3.6 V, VD1G,D2G,D3G = 3.6 V or VD1D,D2D,D3D = 3.6 V, Peak measurement at 12.5% duty cycle, 4.6 ms period, TA = 25°C, unless otherwise noted.) Characteristic Symbol Min Typ Max Unit Frequency Range BW 880 – 915 MHz Output Power Pout 35 36.2 – dBm Power Added Efficiency PAE 45 53 – % Output Power @ Low Voltage (VD1G,D2G,D3G= 3.0 V) Pout dBm GSM SECTION (Pin = 3.0 dBm) 33.5 34.7 – Harmonic Output 2fo ≥3fo – – –35 –60 –30 –45 Second Harmonic Leakage at DCS Output (Crosstalk isolation) – –25 –20 dBm dBc Input Return Loss |S11| – 12 – dB Output Power Isolation with Buffer On (Pin = 3.0 dBm, VD1B,D2B = 3.6 V, VD1G,D2G,D3G = 0 V) Pon – –8.0 –3.0 dBm Output Power Isolation (Pin = 3.0 dBm, VD1B,D2B = 0 V, VD1G,D2G,D3G = 0 V) Poff – –42 – dBm Noise Power in Rx Band 925 to 960 MHz (100 kHz measurement bandwidth) 925 to 935 MHz 935 to 960 MHz NP Negative Voltage (Pin = 2.0 dBm, VD1B, D2B = 3.0 V) Negative Voltage Settling time (Pin = 3.0 dBm, VD1B,D2B stepped from 0 to 3.0 V) Stability–Spurious Output (Pout = 5.0 to 35 dBm, Load VSWR = 6:1 all Phase Angle, Source VSWR = 3:1, at any phase angle Adjust VD1G,D2G,D3G for specified power) dBm –67 –79 VSS – – –4.85 V TS – 0.7 2.0 µs Pspur – – –60 dBc Load Mismatch Stress (Pout = 5.0 to 35 dBm, Load VSWR = 10:1 all phase angles, 5 seconds, Adjust VD1G,D2G,D3G for specified power) Positive Voltage (Pin = 3.0 dBm, VD1B = VD2B = 3.0 V) –90 -90 No Degradation in Output Power Before and After Test VP 6 10 – V Frequency Range BW 1710 – 1785 MHz Output Power Pout 33 34 – dBm DCS SECTION (Pin = 5.0 dBm) Power Added Efficiency PAE 35 43 – % Output Power @ Low Voltage (VD1D,D2D,D3D= 3.0 V) Pout 31.5 32.4 – dBm – – –40 –35 –35 –30 Harmonic Output 2fo ≥3fo dBc Input Return Loss |S11| – 12 – dB Output Power Isolation with Buffer On (Pin = 5.0 dBm, VD1B,D2B = 3.6 V, VD1D,D2D,D3D = 0 V) Pon – –8.0 –2.0 dBm Output Power Isolation (Pin = 5.0 dBm, VD1B,D2B = 0 V, VD1D,D2D,D3D = 0 V) Poff – –36 – dBm Noise Power in Rx Band 1805 to 1880 MHz (100 kHz measurement bandwidth) NP – –85 –71 dBm VSS – – –4.85 V TS – 0.7 2.0 µs Pspur – – –60 dBc Negative Voltage (Pin = 5.0 dBm, VD1B,D2B = 3.0 V) Negative Voltage Settling time (Pin = 5.0 dBm, VD1B,D2B stepped from 0 to 3.0 V) Stability–Spurious Output (Pout = 3.0 to 33 dBm, Load VSWR = 6:1 all Phase Angle, Source VSWR = 3:1, at any phase angle Adjust VD1D,D2D,D3D for specified power) MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA 3 MRFIC1859 ELECTRICAL CHARACTERISTICS (continued) (VD1B, D2B = 3.6 V, VD1G,D2G,D3G = 3.6 V or VD1D,D2D,D3D = 3.6 V, Peak measurement at 12.5% duty cycle, 4.6 ms period, TA = 25°C, unless otherwise noted.) Characteristic Symbol Min Typ Max Unit DCS SECTION (continued) (Pin = 5.0 dBm) Load Mismatch Stress (Pout = 3.0 to 33 dBm, Load VSWR = 10:1 all phase angles, 5 seconds, Adjust VD1D,D2D,D3D for specified power) Positive Voltage (Pin = 5.0 dBm, VD1B = VD2B = 3.0 V) No Degradation in Output Power Before and After Test VP 6 10 – V PIN FUNCTION DESCRIPTION Pin No. Symbol I/O Description Functionality 1 B23G I GSM Bias for 2nd and 3rd stage Bias pin of GSM second and third stages. Biasing circuit is made of an internal resistor connected to RF transistor gate, and in series with a current source, connected to VSS (Pin 32). An external resistor allows to tune biasing point for best gain (Class AB). To switch off GSM line–up, setting this pin (and Pin 18) to high impedance, which will apply VSS (–5.0 V) to the gates, i.e., a voltage two times lower than FET threshold voltage. 2 VP O Positive voltage A buffer amplifier is designed to produce the required negative voltage, based on RF signal amplification and rectification. Also a positive voltage is generated in the same way, with rectification and a voltage doubler. This voltage supplies an op amp in order to drive a NMOS as drain switch. Refer to application schematic, with MC33170 and MTSF3N02 (products of On Semiconductor). 3 Gnd 4,5,6,7,8 OutG 9 Ground O GSM output RF output and power supply for output GSM stage. Supply voltage is provided through those five pins. An external matching network is required to provide optimum load impedance. N.C. 10,11,12 D2G I GSM 2nd stage drain Power supply for GSM second stage, and inter–stage matching. Wire bonds and pins form the required inductor for optimum inter–matching tuning. Make note that decoupling capacitor on those pins needs to be placed as close as possible to the pins. Refer to application schematic for component value. 13 D1D I DCS 1st stage drain Power supply for DCS first stage, and inter–staging matching. This pin associated with a printed line (80 Ω) forms the required inductor for a proper match. 14 D1B I Buffer 1st stage drain Power supply for buffer amplifier first stage, and inter–staging matching. This pin, associated with a printed line (80 Ω) forms the required inductor for a proper match. 15 B1D I DCS 1st stage Bias Same function as Pin 18 for DCS amplifier. 16 InD I DCS RF Input RF input for DCS amplifier. A series inductor or line and a parallel inductor are required for a proper matching to 50 Ω and maximum gain. See application circuit. 17 InG I GSM RF Input RF input for GSM amplifier. An inductor and a capacitor are required for a proper matching to 50 Ω and maximum gain. See application circuit. 18 B1G I GSM 1st stage Bias Bias pin of GSM first stage and associated buffer stage. Biasing circuit is made of an internal resistor connected to RF transistor gate, and in series with a current source, connected to VSS (Pin 32). An external resistor allows to tune biasing point for best gain (Class AB). See comments on Pin 1. 19 D1G I GSM 1st stage drain Power supply for GSM first stage, and inter–stage matching. This pin, associated with a printed line (80 Ω) form the required inductor for a proper match. 20 G2D I DCS 2nd stage gate Access to DCS 2nd stage gate. A shunt capacitor connected to this pin contributes to the inter–stage matching between 1st and 2nd DCS stages. 21 VSC O Check for Negative voltage An opened drain transistor connected to this pin, with VSS as gate voltage, gives a checking signal for negative voltage generation. Used in application circuit to forbid on state to the NMOS Drain switch when VSS is not working. Prevents IC degradation when bias is not present. This pin is not used with MC33170 which has its own protection circuit. 4 MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 PIN FUNCTION DESCRIPTION (continued) Pin No. Symbol I/O Description 22,23 D2D I DCS 2nd stage drain 24 B23D I DCS Bias for 2nd and 3rd stage 25,26,27, 28,29 OutD O DCS RF Output RF output and power supply for output DCS stage. Supply voltage is provided through those five pins. An external matching network is required to provide optimum load impedance. 30 B2B I Buffer 2nd state Bias Like Pins 1, 15, and 18, this is a bias pin. Pin 30 is used to bias 2nd stage of buffer amplifier. 31 D2B I Buffer 2nd stage Drain Drain supply and matching of buffer amplifier to maximize VSS and VP voltages. 32 VSS O Negative Voltage A buffer amplifier is designed to produce the required negative voltage, based on RF signal amplification with a two stages wide band amplifier and rectification of the resulting signal. An external zener diode is used to regulate this voltage and provide to the gates a stabilized biasing voltage. VSS is also used to switch off the unused amplifier. Refer to Bias Pins 1, 18 and 15, 24. Exposed Pad Gnd I Main Gnd MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA Functionality Power supply for DCS driver stage, and inter–staging matching. These pins form the required inductor for a proper match. Same as Pin 1 for DCS amplifier. The bottom pad of the TQFP–32EP package is used for electrical/RF grounding and thermal dissipation. The PCB pattern where it fits has to be tailored for good ground and thermal continuity (with many ground via holes). 5 MRFIC1859 Figure 1. Application Schematic Vbat C23 100 nF Vramp CE MTSF3N02* R8 10k MC33170* 1 Band Select BS 2 TxEN 3 BGSM 4 BDCS 5 VDB 6 Gnd 7 V bat Tx EN 14 CE VSS 13 12 Out 11 VP 10 InV 9 NinV LDO 8 S D S D S D G D R6 10k C20 N.C. R7 10k C19 100 nF C16 1.0 nF T5 1.5 mm R2** 6.8 k C9 47 pF T2 47 mm T3 22 mm 1.5 mm T6 1 24 2 23 3 22 4 C4 4.7 pF C3 12 pF 6 19 T4 7 18 8 17 9 10 11 12 13 14 15 16 C8 6.8 pF T9 11 mm C17 47 pF R5 12 k L1 15 nH C21 5.6 pF In GSM R4 8.2 k C14 47 pF C12 10 nF 6 20 2.5 mm N.C. T1, T2, T3, T4 Zc = 50 Ω T5, T6 Zc = 30 Ω T7, T8, T9, T10 Zc = 80 Ω Substrate FR4 Er = 4.5 C2, C3, C4 are high Q capacitors * Products of ON Semiconductor ** ±1% tolerance C15 12 pF C13 12 pF T8 12 mm T1 6.0 mm T7 5.5 mm C5 47 pF R3** 5.6 k 21 MRFIC1859 5 Out GSM Exposed Pad (Gnd – on bottom) 32 31 30 29 28 27 26 25 N.C. C6 1.0 pF C10 22 pF R9 1.5 k C7 22 pF L3 56 nH Out DCS C2 3.9 pF C18 47 pF R1 2.2 k C11 3.3 pF C1 47 pF T10 4.0 mm C22 47 pF In DCS L2 2.7 nH MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 GSM TYPICAL CHARACTERISTICS Figure 3. Power Added Efficiency versus Frequency Figure 2. Output Power versus Frequency 38 55 37.5 54 37 Vbat = 4.2 V 52 36 3.6 V PAE (%) Pout (dBm) 3.6 V 53 36.5 35.5 35 34 33.5 890 895 3.0 V 50 48 TA = 25°C Pin = 3.0 dBm 885 51 49 3.0 V 34.5 33 880 Vbat = 4.2 V 900 905 910 TA = 25°C Pin = 3.0 dBm 47 46 880 915 885 905 Figure 5. Output Power versus Frequency TA = –35°C 915 TA = –35°C 36.5 Pout (dBm) 25°C 34.5 34 85°C 33.5 885 890 895 900 905 910 36 35.5 85°C 35 Vbat = 3.0 V Pin = 3.0 dBm 34.5 880 915 Vbat = 3.6 V Pin = 3.0 dBm 885 890 895 900 905 910 f, FREQUENCY (MHz) f, FREQUENCY (MHz) Figure 6. Output Power versus Frequency Figure 7. Power Added Efficiency versus Frequency 38 915 58 37.5 TA = –35°C 56 25°C 54 PAE (%) 37 85°C 36.5 TA = –35°C 25°C 52 85°C 50 36 35.5 880 910 37 25°C Pout (dBm) 900 Figure 4. Output Power versus Frequency 35 Pout (dBm) 895 f, FREQUENCEY (MHz) 35.5 33 880 890 f, FREQUENCY (MHz) Vbat = 4.2 V Pin = 3.0 dBm 885 890 895 900 905 f, FREQUENCY (MHz) MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA 910 Vbat = 3.6 V Pin = 3.0 dBm 48 915 46 880 885 890 895 900 905 910 915 f, FREQUENCY (MHz) 7 MRFIC1859 GSM TYPICAL CHARACTERISTICS Figure 9. Third Harmonics versus Frequency Figure 8. Second Harmonics versus Frequency 46 67 44 66 TA = 25°C 40 64 –35°C H3 (dBc) H2 (dBc) TA = –35°C 65 85°C 42 38 36 25°C 63 62 61 34 32 30 880 885 890 895 900 905 910 85°C 60 Vbat = 3.6 V Pin = 3.0 dBm Vbat = 3.6 V Pin = 3.0 dBm 59 58 880 915 885 890 895 900 905 f, FREQUENCY (MHz) f, FREQUENCEY (MHz) Figure 10. Positive Voltage Generator Output versus Frequency Figure 11. Crosstalk versus Frequency 13 910 915 –22 –23 12 –24 XTALK (dBm) Vpos (V) TA = –35°C 11 25°C 10 85°C 8.0 880 885 890 40 900 910 –30 880 915 85°C 895 900 905 TOTAL CURRENT (A) 15 10 5.0 f = 897.5 MHz Vbat = 3.6 V Pin = 3.0 dBm 25°C 1.0 1.5 Vramp (V) 910 915 2.5 20 0.5 890 3.0 25 0 885 Figure 13. Total Current versus Vramp 30 –10 Vbat = 3.6 V Pin = 3.0 dBm –29 Figure 12. Output Power versus Vramp TA = –35°C 0 25°C f, FREQUENCY (MHz) –5.0 8 905 –27 f, FREQUENCY (MHz) 35 Pout , OUTPUT POWER (dBm) 895 85°C –26 –28 Vbat = 3.6 V Pin = 3.0 dBm 9.0 TA = –35°C –25 2.0 TA = –35°C 2.0 85°C 25°C 1.5 1.0 f = 897.5 MHz Vbat = 3.6 V Pin = 3.0 dBm 0.5 2.5 0 0 0.5 1.0 1.5 2.0 2.5 Vramp (V) MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 DCS TYPICAL CHARACTERISTICS Figure 15. Power Added Efficiency versus Frequency Figure 14. Output Power versus Frequency 47 35 Vbat = 4.2 V 34 3.6 V 46 3.6 V 33 32 1725 1740 1755 1770 40 1710 1785 1725 1740 1755 1770 f, FREQUENCY (MHz) f, FREQUENCY (MHz) Figure 16. Output Power versus Frequency Figure 17. Output Power versus Frequency 1785 35 34.5 TA = –35°C 32.5 25°C 32 31.5 Pout (dBm) Pout (dBm) TA = 25°C Pin = 5.0 dBm 41 33 85°C TA = –35°C 34 25°C 33.5 85°C 33 31 Vbat = 3.0 V Pin = 5.0 dBm 30.5 1725 1740 1755 1770 Vbat = 3.6 V Pin = 5.0 dBm 32.5 32 1710 1785 1725 1740 1755 1770 f, FREQUENCY (MHz) f, FREQUENCY (MHz) Figure 18. Output Power versus Frequency Figure 19. Power Added Efficiency versus Frequency 36 1785 48 35.5 TA = –35°C 46 TA = –35°C 25°C 44 25°C 42 85°C 35 PAE (%) Pout (dBm) 3.0 V 43 42 TA = 25°C Pin = 5.0 dBm 33.5 30 1710 44 3.0 V 31 30 1710 Vbat = 4.2 V 45 PAE (%) Pout (dBm) 36 85°C 34.5 40 34 33.5 1710 Vbat = 4.2 V Pin = 5.0 dBm 1725 1740 1755 1770 f, FREQUENCY (MHz) MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA Vbat = 3.6 V Pin = 5.0 dBm 38 1785 36 1710 1725 1740 1755 1770 1785 f, FREQUENCY (MHz) 9 MRFIC1859 DCS TYPICAL CHARACTERISTICS Figure 21. Third Harmonics versus Frequency Figure 20. Second Harmonics versus Frequency 49 46 47 45 25°C 43 41 –35°C 85°C 37 34 39 31 Vbat = 3.6 V Pin = 5.0 dBm 37 35 1710 1725 1740 1755 Vbat = 3.6 V Pin = 5.0 dBm 28 1770 25 1710 1785 1725 1740 1755 1770 f, FREQUENCY (MHz) f, FREQUENCEY (MHz) Figure 22. Positive Voltage Generator Output versus Frequency Figure 23. Output Power versus Vramp 12 40 TA = –35°C 10 25°C 9.0 85°C Vbat = 3.6 V Pin = 5.0 dBm 8.0 TA = –35°C 30 85°C 25 25°C 20 15 10 f = 1747.5 MHz Vbat = 3.6 V Pin = 5.0 dBm 5.0 0 7.0 1710 1725 1740 1755 1770 –5.0 1785 1785 35 Pout , OUTPUT POWER (dBm) 11 Vpos (V) TA = –35°C 40 85°C H3 (dBc) H2 (dBc) 43 TA = 25°C 0 0.5 1.0 f, FREQUENCY (MHz) 1.5 2.0 2.5 Vramp (V) Figure 24. Total Current versus Vramp 2.0 1.8 TOTAL CURRENT (A) 1.6 TA = –35°C 1.4 85°C 1.2 1.0 25°C 0.8 0.6 f = 1747.5 MHz Vbat = 3.6 V Pin = 5.0 dBm 0.4 0.2 0 0 0.5 1.0 1.5 2.0 2.5 Vramp (V) 10 MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 APPLICATIONS INFORMATION Design Philosophy The MRFIC1859 is a dual–band single supply RF integrated power amplifier designed for use in GSM900/DCS1800 handheld radios under 3.6 V operation. With matching circuit modifications, it is also applicable for use in triple band GSM900/DCS1800/PCS1900 equipment. Typical performances in GSM/DCS at 3.6 V are: GSM: 35.8 dBm with 53% PAE and, DCS: 34 dBm with 43% PAE. It features a large band (900 to 1800 MHz) internal Negative Voltage Generator based on RF rectification of the input carrier after its amplification by two dedicated buffer stages (See Simplified Block Diagram). This method eliminates spurs found on the output signal when using dc/dc converter type negative voltage generators, either on or off chip. The buffer generates also a step–up positive voltage, which can be used to drive a NMOS drain switch. External Circuit Considerations The MRFIC1859 can be tuned by changing the values and/or positions of the appropriate external components (see Figure 1: Application Schematic). While tuning the RF line–up, it is recommended to apply external negative supply in order to prevent any damage to the power amplifier stages. Poor tuning on the input may not provide enough RF power to operate the negative voltage generator properly. Input matching is a shunt–C, series–L, low pass structure for GSM and a shunt–L, series–L high pass structure for DCS. It should be optimized at the rated input power (e.g. 3.0 dBm in GSM, 5.0 dBm in DCS). Since the input lines feed both 1st stages and 1st stage buffers, input matching should be iterated with buffer and Q1 drain matching. Note that dc blocking capacitors are included on chip. First stage buffer amplifier is tuned with a short 80 Ω microstrip line which may be replaced by a chip inductor. Second stage buffer amplifier is supplied and matched through a discrete chip inductor. Those two elements are tuned to get the maximum output from voltage generator. The overall typical buffer current (DB1 + DB2) is about 60 mA in GSM and 100 mA in DCS. However, the negative generator needs a settling time of 1.0 µs (see burst mode paragraph). During this transient period of time, both stages are biased to IDSS, which is about 200 mA each. The step–up positive voltage available at Pin 2, which is approximately 10 V in each band, can be used to drive a NMOS drain switch for best performances. Q1 drains are supplied and matched through 80 Ω printed microstrip lines that could be replaced by discrete chip inductors as well. Their lengths (or equivalent inductor values) are tuned by sliding the RF decoupling capacitors along to get the maximum gain on the first stages. Q2 drains are supplied through 60 Ω printed microstrip lines that contribute also to the interstage matching in order to optimum drive to the final stages. The line length for Q2G and Q2D is small, so replacing it with discrete inductors is not practical. Q3 stages are fed via 50 Ω printed microstrip lines that must handle the high supply current of that stages (2.0 Amp peak) without significant voltage drop. This line can be buried in an inner layer to save PCB space or be a discrete RF choke. Output matching is accomplished in both bands with two stages low pass networks. Easy implementation is achieved MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA with shunt capacitors mounted along a 50 Ω microstrip transmission line. Value and position are chosen to reach a load line of 2.0 Ω while conjugating the device output parasitics. The networks must also properly terminate the second and third harmonic level. Use of high–Q capacitors for the first output matching capacitor circuits is recommended in order to get the best output power and efficiency performances. Note: the choice of output matching capacitor type and supplier will affect H2 and H3 level and efficiency, because of series resonant frequency. Tuning Methodology The following section gives the user some guidelines and hints to tune and optimize the MRFIC1859 operation inside their own radio PCB. First of all, one must keep in mind that negative and positive voltage generation is based on RF carrier rectification. This means that RF input signal must always be present when running the part as a standalone solution. Therefore, in order to ease the tuning phase, it is recommended to apply the negative voltage externally in order to avoid any damage to the large RF MESFET transistors. This is particularly true if one uses the complete application with MC33170 (product of On Semiconductor) as control IC to do the optimization. In that case, both negative and positive voltage should be provided externally. The RF decoupling capacitors have been selected as 47 pF for GSM band (C17, C14, C22, C9. C1, and C8) and 22 pF or 12 pF for DCS band (C10, C15, and C13). But those can be optimized depending on their size and source, for example 12 pF were used at some places for DCS to provide better decoupling of the harmonics too, thus providing some extra performance. The recommended tuning procedure consists of several steps that need to be performed in sequential order. Several iterations can be performed if appropriate. Due to low interaction between line–ups, each band can be tuned independently. • Optimize the buffer operation using D1B (T8 line) and D2B matching (L3 inductor). Simultaneously, tune GSM or DCS input matching using L1, C21 or L2, T10, respectively. Check the margin on Pin to generate VSS and VP (those voltages should still meet their specification with a 5.0 dB reduction in Pin). A small shunt capacitor can be placed on VP to maximize that voltage. • Optimize RF line up linear gain using D1G, D2G matching (T9 line) or D1D, D2D, G2D matching (T7 line, C8) for GSM or DCS line–up, respectively. The goal is to maximize and center small signal gain. Pin has to be reduced for this exercise, hence the negative voltage needs to be applied externally. A broad band measurement is helpful to visualize the frequency response. Linear gain should peak at around 40 dB for GSM and 32 dB for DCS. The input matching has to be checked again and eventually refined during this step. • Optimize output matching using T4, C3, T1, C4 and T2 for GSM or T6, C2, T5, C6, T3 for DCS, respectively. Those elements set the Pout/PAE trade–off and harmonics rejection performance. 11 MRFIC1859 • Finally, one can iterate some of the above steps to fine tune RF behavior and also to find the best configuration for Cross–Talk and Harmonics content reduction. For example, D2B inductor L3 and VSS decoupling capacitor C11 have a small influence on the GSM second harmonic leaking through the DCS output. The nominal impedance seen from the IPA package pins have been measured on the demoboard (after removing the MRFIC1859) and are listed in the following table. They can be taken as a starting point for the optimization. Also this gives the equivalent lumped element if one uses a lumped element instead of microstrip line. Impedance on the different GSM I/Os: (expressed in Ω at 900 MHz) – – – – – – InG = 16.2 + j83.5 OutG = 1.9 – j2.3 D2G = close to 0 since decoupled as short as possible D1G = 1 + j19.8 (3.5 nH) D1B = 1.2 + j28.7 (5.0 nH) D2B = infinite since 56 nH behaves as choke Impedance on the different DCS I/Os: (expressed in Ω at 1750 MHz) – – – – – – – InD = 12.5 + j36.5 OutD = 3.6 – j4.4 D2D = close to 0 since decoupled as short as possible G2D = 0.9 + j6.8 (0.64 nH) D1D = 1.1 + j20.8 (1.9 nH) D1B = 8.8 + j84.7 (7.6 nH) D2B = infinite since 56 nH behaves as choke One should note that except for RFin/RFout impedance, all others should be ”in theory” pure reactive shunt elements. The fact that their resistive part is not zero is linked to the finite quality factor of the equivalent inductor and also to the limited accuracy of the measurement (when close to the Smith chart border). Control Considerations The MRFIC1859 application uses drain control technique developed for our generations of GaAs IPAs. This method relies on the fact that for an RF power amplifier operating in saturation mode, the RF output power is proportional to the square of the Amplifier drain voltage: Pout (Watt) = k * VD (V) * VD (V). A dedicated control IC MC33170 has been designed to manage all those control, biasing and band selection functions. When the emitting order is sent (TxEn = High), the MC33170 activates the power supply VDbuf of the negative voltage generator NVG (VDbuf = Vbat), involving the presence of Vneg as well as a positive VP of about 9.0 V. Once Vneg detected and regulated at –5.0 V, the MC33170 enables a N–channel MOSFET to be driven. 12 The NMOS is used as a ballast transistor whose drain–source resistance is controlled by Vramp. This allows to supply the PA with a voltage from 0 V (Vramp = 0 V) to Vbat (Vramp = 2.0 V) and hence to control the output power. Such a way of control provides an excellent predictability of the RF output power (since the output voltage is proportional to the drain voltage) and eliminates the need for a power or current detection loop. The band selection is achieved by setting the BS pin of the MC33170 to 0 V (GSM) or 1.0 V (DCS), hence biasing the GSM or DCS transistors through BiasGSM and BiasDCS pins. Burst Mode In order to perform burst mode measurements, the following time can be used as a guideline. Figure 25. 2.0 V CE 0V 2.0 V TxEn (& Pin) 0V 10 µs 2.0 V Vramp 0V 1.0 µs – First the MC33170 must be awaken through CE to activate its Low Drop Out Regulator. The BS pin has also to be set according to the selected frequency band. – Then TxEn is set high which supply the buffer stages and activates the Negative and Positive Voltage Generation. TxEn signal can be used to switch the input power (using a driver or attenuator) in order to provide higher isolation for on/off burst dynamic. – Vramp (Pin 1) can be applied soon after TxEn since the internal negative voltage generator settles in less than 1.0 µs. References (Motorola Application Notes) AN1599 – Power Control with the MRFIC0913 GaAs Integrated Power Amplifier and MC33169 Support IC. AN1697 – GSM900/DCS1800 Dual–Band 3.6 V Power Amplifier Solution with Open Loop Control Scheme. MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 NOTES MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA 13 MRFIC1859 NOTES 14 MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA MRFIC1859 OUTLINE DIMENSIONS 4X PLASTIC PACKAGE CASE 873E–02 (TQFP–32EP) ISSUE A 0.2 C A–B D D q2 D/2 G D G 24 q1 R1 R2 S q A A2 25 16 A A1 B q3 0.25 L GAGE PLANE (L1) E E1 DETAIL F E1/2 E/2 PLATING 9 32 ÌÌÌÌÌ ÏÏÏÏ ÌÌÌÌÌ ÏÏÏÏ ÌÌÌÌÌ b1 c1 8 1 6 BASE METAL c (b) D1/2 D1 SECTION G–G 4X 0.2 H A–B D H F SEATING PLANE C 4X e/2 28X 0.08 C e 32X b 0.08 J M C A–B D J M EXPOSED FLAG N NOTES: 1. DIMENSIONS ARE IN MILLIMETERS. 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994. 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H. 4. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25–MM PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH. 5. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM b DIMENSION BY MORE THAN 0.08–MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN A PROTRUSION AND ADJACENT LEAD IS 0.07–MM 6. EXACT SHAPE OF CORNERS IS OPTIONAL. DIM A A1 A2 b b1 C C1 D D1 e E E1 L L1 M N R1 R2 S q q1 q2 q3 MILLIMETERS MIN MAX ––– 1.13 0.039 0.089 0.95 1.05 0.17 0.27 0.17 0.23 0.09 0.2 0.09 0.16 7 BSC 5 BSC 0.5 BSC 7 BSC 5 BSC 0.45 0.75 1 REF 2.09 2.19 2.09 2.19 0.08 ––– 0.08 0.2 0.2 ––– 0° 7° 0° ––– 11° 13° 11° 13° VIEW J–J MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA 15 MRFIC1859 Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer. How to reach us: USA / EUROPE / Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447 Technical Information Center: 1–800–521–6274 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan. 81–3–3440–3569 ASIA / PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334 HOME PAGE: http://www.motorola.com/semiconductors/ 16 ◊ MRFIC1859/D MOTOROLA WIRELESS SEMICONDUCTOR SOLUTIONS – RF AND IF DEVICE DATA