* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Digital Electronics Tutorial - 2

Survey

Document related concepts

Transcript

Digital Electronics Tutorial

2

13th February, 2006

Indian Institute of Technology,

Kharagpur, India.

Tutors : Daibashish, Subhodeep, Narayanan and Saurabh,

5th Year Dual Degree, Dept. of E &ECE. IIT Kharagpur.

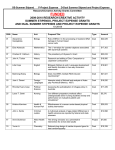

Digital Electronics Class Test -1

Solutions

•

Question 1.

– Compute the logic equations for a BCD

to 7 segment code converter.

– For example if the input <x3,x2,x1,x0> =

<0,0,1,1> i.e. decimal equivalent of 3 then

LEDs a,b,c,d and g turn on. For input

=<1,0,0,0> all LEDs turn on.

Write the logic equations for a,b, d and g

LEDs

Solution

for Q1.

Fig. A 7 Segment Display

a = X3’ ( X1 + (X2X0)’ ) + X3 X2’X1’

b = X3’ ( X2’ + (X1X0)’ ) + X3 X2’X1’

c = X3’ ( X2+X1’+X0) + X3 X2’X1’

d = X3’ ( X2(X1X0) +X2’(X1+X0’) )+X3 X2’X1’

e = X3’ X0’ ( X1 + X2’ ) +X3 X2’X1’X0’

f = X3’ (X2 X1’ X0’) +X3 X2’X1’

g = X3’(X1X2) + X3’X2 X1 X0’ +X3 X2’X1’

NO need to optimize.

Just straight 4-variable

equation required

Question 2.

•

Let

F(A,B,C,D)= f(A,B,C,D) + g(A,B,C,D) .

Given f =B’D’ + A’C’D’ + AB’C’ , find

g(A,B,C,D) such that F is self-dual.

Also find the minimal sop and pos

expressions for F.

[ Note : A function is self dual if

F(a’,b’,c’,d’)=F’ (a,b,c,d) ]

Solution to Q2.

• A 4 variable, self dual function will have

opposite entries in locations marked n and

15 – n . We observe that location pairs

(12,3) and (14,1) are the only

complementary locations which do not

have 1 in them. So, to make F self dual set

locations { 12 and 14 } to 1.

• (Note : We may also set { 12 and 1 } or { 3

and 14 } or { 3 and 1} to 1 )

• This makes G(A,B,C,D) =∑(12,14) =ABD’

• Minimal Sop expression of F(A,B,C,D) =

B’D’ + C’D’ + AD’ + AB’C’

• Minimal Pos expression of F(A,B,C,D) =

(B’+D’) (C’+D’)(A+D’) ( A+B’+C’)

Question 3.

Design a magnitude comparator M101 which

compares the 3 bit numbers A=<a2,a1,a0> and

B=<b2,b1,b0> taking three additional inputs

Ein, Gin and Lin, that represent the equal,

greater than and lesser than signals from a

previous more significant stage. Write the

logic equations for Eout , Gout and Lout for

this module in terms of its inputs.

[ Use two M101 modules to compare two 5-bit

numbers viz.

X=<x4,x3,x2,x1,x0> and Y= <y4,y3,y2,y1,y0>]

Solution for Question 3.

• Let ci = ( ai xor bi )’ for I = 0,1,2.

Then :

Eout = Ein . c0.c1 .c2

Gout = Gin + Ein ( a2 . b2’ + c2 a1 b1’ +

c2 c1 a0 b0’ )

Lout = Lin + Ein ( a2’ .b2 + c2 a1’ b1 +

c2 c1 a0’ b0 )

Fig. Recommended design.

Question 4.

• What is the minimum number of 2 to 1

multiplexers required to determine the

square of a 3 bit number <x2,x1,x0> ?

Solution for Q4.

Fig. Shows the Truth Table of the Squaring circuit

From above it’s quite clear that

• Y0=X0 , Y1=0 , Y2 = X2’ X1 X0’ + X2 X1 X0’

= X1 X0’

• Y3 = X2’ X1 X0 + X2 X1’ X0

= X0 ( X1 X2)

• Y4 = X2 X1’ X0’ + X2 X1’ X0 + + X2 X1 X0

= X2 ( X0 + X1’)

• Y5 = X2 X1

• So Y0 and Y1 do not require muxes.

Y2 requires 1 mux .

Y3 requires 3 muxes : 2 for Xor & 1 for And. Y4

requires 2 muxes : 1 for Or & 1 for And.

Y5 requires 1 mux.

Hence a total of 7 2-to-1 multiplexers are needed.

• Please Submit your homework sheets

from the previous Tutorial (the QM Problems)

******** The End.********

Have a Good time at the

Mid-Semester Examinations!