* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Self-Bias Configuration

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Stray voltage wikipedia , lookup

Mains electricity wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Buck converter wikipedia , lookup

Distribution management system wikipedia , lookup

Two-port network wikipedia , lookup

Current mirror wikipedia , lookup

History of the transistor wikipedia , lookup

Opto-isolator wikipedia , lookup

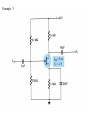

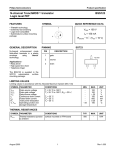

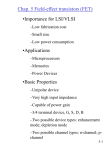

SMALL SIGNAL FET (Field– Effect Transistors) AMPLIFIER 1. 2. 3. 4. 5. 6. 7. Introduction/Basic FET Small-Signal Model Fixed-Bias Configuration Self-Bias Configuration Voltage-Divider Configuration Common-Drain Configuration Common-Gate Configuration 1. INTRODUCTION / BASIC Field–Effect Transistors (FET) FET’s (Field – Effect Transistors) are much like BJT’s (Bipolar Junction Transistors). FET is usually called a unipolar transistor being that the current carrier is wholly of a single type either electron or holes only. While the bipolar transistor is a dual current carrier system having both electrons and holes together. Similarities: • Amplifiers • Switching devices • Impedance matching circuits Differences: • FET’s are voltage controlled devices whereas BJT’s are current controlled devices. • FET’s also have a higher input impedance, but BJT’s have higher gains. • FET’s are less sensitive to temperature variations and because of there construction they are more easily integrated on IC’s. • FET’s are also generally more static sensitive than BJT’s. FET Types • JFET ~ Junction Field-Effect Transistor • MOSFET ~ Metal-Oxide Field-Effect Transistor - D-MOSFET ~ Depletion MOSFET - E-MOSFET ~ Enhancement MOSFET Bipolar Junction Transistors Transistor Construction There are two types of transistors: pnp and npn-type. Note: the labeling of the transistor: E - Emitter B - Base C - Collector JFET Construction There are two types of JFET’s: n-channel and p-channel. The n-channel is more widely used. n There are three terminals: Drain (D) and Source (S) Gate (G) Basic Operation of JFET JFET operation can be compared to a water spigot: The source of water pressure – accumulated electrons at the negative pole of the applied voltage from Drain to Source The drain of water – electron deficiency (or holes) at the positive pole of the applied voltage from Drain to Source. The control of flow of water – Gate voltage that controls the width of the n-channel, which in turn controls the flow of electrons in the n-channel from source to drain. JFET Operating Characteristics There are three basic operating conditions for a JFET: A. VGS = 0, VDS increasing to some positive value B. VGS < 0, VDS at some positive value C. Voltage-Controlled Resistor JFET Symbols n-channel p-channel Common JFET Biasing Circuits General Relationships The general relationships that can be applied to dc analysis of all FET amplifiers are: IG 0A ID IS Shockley’s equation is applied to relate the input and output quantities: Pinch-off ID IDSS(1 VGS 2 ) VP Fixed-Bias Configuration Fixed-bias configuration VGS = - VGG VDS = VDD – IDRD VS = 0 VD = VDS VG = VGS Network for dc analysis Plotting the Transfer Curve From Shockley’s equation, IDSS and Vp (VGS(off)), the Transfer Curve can be plotted using these 3 steps: Step 1: ID IDSS(1 Solving for VGS = 0V: ID IDSS Step 2: VGS 0V ID IDSS(1 Solving for VGS = Vp (VGS(off)): ID 0 A VGS 2 ) VP VGS 2 ) VP VGS VP Step 3: Solving for VGS = 0V to Vp: ID IDSS(1 VGS 2 ) VP Fixed-Bias Transfer Curve Finding the solution for the fixed-bias configuration Plotting shockley’s equation Shorthand Method VGS versus ID using Shockley’s equation VGS ID 0 IDSS 0.3 VP IDSS/2 0.5 VP IDSS/4 VP 0 mA ID IDSS(1 VGS VGS 2 ) VP ID VP 1 I DSS Example 1: Determine : VGSQ, IDQ, VDS, VD, VG and VS Graphical solution for the network Self-Bias Configuration JFET self-bias configuration DC analysis of the self-bias configuration Self-Bias Calculations For the indicated loop: VGS I D RS • To solve this equation select an ID < IDSS and use the component value for RS. • Plot this point: ID and VGS and draw a line from the origin of the axis to this point. • Next plot the transfer curve using IDSS and VP (VP = VGSoff in specification sheets) and a few points such as ID = IDSS/4 and ID = IDSS/2 etc. Where the first line intersects the transfer curve is the Q-point. Use the value of ID at the Q-point (IDQ) to solve for the other voltages: VDS VDD I D ( RS RD ) VS I D RS VG 0V VD VDS VS VDD VRD Self-Bias Transfer Curve Defining a point on the self-bias line. Self-Bias Transfer Curve Sketching the self-bias line. Example 6.2 Sketching the self-bias line for the network Sketching the device characteristics for the JFET Determining the Q-point for the network Determining the quiescent point of operation for the network of Example 2. Example 3 Example 4 Sketching the dc equivalent of the network Voltage-Divider Bias IG = 0A in FETs. Unlike BJTs, where IB affected IC; in FETs it is VGS that controls ID. Voltage-Divider Bias Calculations VG Using Kirchoff’s Law: Rearranging and using ID =IS: R2VDD R1 R2 VG VGS VRS 0 VGS VG I D RS Again the Q point needs to be established by plotting a line that intersects the transfer curve. Voltage-Divider Q-point 1. 2. 3. Plot the line: By plotting two points: VGS = VG, ID =0 and VGS = 0, ID = VG/RS Plot the transfer curve by plotting IDSS, VP and calculated values of ID. Where the line intersects the transfer curve is the Q point for the circuit. Voltage-Divider Bias Calculations Using the value of ID at the Q-point, solve for the other variables in the Voltage-Divider Bias circuit: VDS VDD I D ( RD RS ) VD VDD I D RD VS I D RS VDD IR1 IR2 R1 R2 Example 5 Determining the Q-point for the network Example 6 Determining the network equation for the configuration Determining the Q-point for the network Summary Table P-Channel FETs For p-channel FETs the same calculations and graphs are used, except that the voltage polarities and current directions are the opposite. The graphs will be mirrors of the nchannel graphs. Practical Applications • Voltage-Controlled Resistor • JFET Voltmeter • Timer Network • Fiber Optic Circuitry