* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download FETs, the curve trace,r and PSpice simulation -

Variable-frequency drive wikipedia , lookup

Current source wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Power inverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Schmitt trigger wikipedia , lookup

Semiconductor device wikipedia , lookup

Stray voltage wikipedia , lookup

Oscilloscope history wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Surge protector wikipedia , lookup

Voltage regulator wikipedia , lookup

Power electronics wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Current mirror wikipedia , lookup

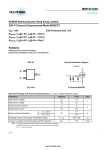

ECEN 3711 FETs, the curve tracer, and PSpice simulation [10 points] Lab #5 Purpose: To use a curve tracer to obtain and study V-I traces for a JFET which is a good device for this lab work and will be used with the tracer. To simulate MOSFET digital circuits with PSpice. Equipment: Tektronix 577 curve tracer. Spec Sheets: Obtain a copy of MPF102 and 2N7000 spec (specification) sheets. Procedure: Listen carefully and take notes as needed while your instructor explains and demonstrates how to use the 577 curve tracer to get JFET characteristics. We will use an MPF102 n-channel junction field-effect transistor for our curve-tracer work. In the experimental work below, please do not spend more than your group’s share of time with a 577 tracer. You may watch another group work with their JFET, but do your own work on the tracer. Explain why you need to invert the step generator with the JFET. [0.5 pt] 1. Experiment: Take an MPF102 from the tray and insert it properly into the 577 test socket. Carefully adjust the sweep (VDS) and the display to show the common-source characteristics for VDS from 0 to 20 V (horizontal axis) and its ID from about 0 to 10 mA (vertical axis). Gate voltage steps and sweep-voltage series resistance should be set so your curve family fills about ¾ of the screen. Sketch (or photograph and print) the characteristics. Be sure to label your axes values and the values of the VGS steps since the 577 tracer does not do this for you. With the device still in the test fixture, find the gate voltage, VGS, needed to give (ID, VDS) = (3 mA, 7 V). Find IDSS, the value of ID when VGS = 0 V. Find the pinch-off voltage, VP, by looking for the value of VGS where ID is between 10 and 100 A. Ideally ID = 0 at VGS = VP. One more test: switch the S (source) and D (drain) connections and compare the results. [3 pts] 2. Lower the VDS sweep range and expand the VDS scale to do a detailed sketch of the low-voltage nonsaturation (ohmic) region of the curves. [1 pt] 3. Compare values obtained in the measurements above with the spec-sheet values. [0.5 pt] 4. OrCAD/PSpice: Use a 2N7000 n-channel enhancement-mode MOSFET. Find and use the one named 2N7000/PWRMOS in the PSPICE\PWRMOS library. Create a circuit to obtain its output family of curves, i.e., ID versus VDS. Obtain the family for 0 ≤ VDS ≤ 6V and for 0 ≤ VGS ≤ 5V with VGS steps of 1V. In your report print the following: an .OUT file, the curve-family plot, and the schematic. Include labels and notes on your prints. [1 pt] 5. The 2N7000 is not a chip-level FET, so edit the PSpice model and reset the following parameters to more suitable values for a chip-level logic device: Kp = 35µ (A/V2), Vto = 0.8V, W = 0.3µm, L = 2µm, Rds = 48MEG (Ω). [Comparing with the Neamen text, Kp is kn', Vto is VTN, and Rds is ro.] Obtain the family again with these new parameter values. Compare the results with #4. [1.5 pts] 6. Find a design for a logic inverter for 5-V logic using NMOS enhancement mode driver and load devices (e.g., Neamen text, pp 1153-1155). Use two 2N7000s with parameters reset as in #5, and run some PSpice tests with the design. For example, get a plot of its transfer characteristic (output voltage versus input voltage). [2 pts] 7. Conclusions: Discuss differences between the JFET and the MOSFET devices used in this lab. [0.5 pt] P.Munro 11-May-2017 04:52 AM