* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download On the design of a very high resolution DAC at 1 kHz for

Current source wikipedia , lookup

History of electric power transmission wikipedia , lookup

Mains electricity wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Control system wikipedia , lookup

Electronic engineering wikipedia , lookup

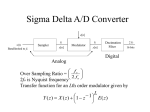

Power electronics wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Rectiverter wikipedia , lookup

Alternating current wikipedia , lookup

On the design of a very high resolution DAC at 1 kHz for space applications D. Mitrovgenis, K. Makris, D. Fragopoulos, G. Tsiligiannis, C. Papadas Integrated Systems Development (ISD S.A) Athens, Greece Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 1/28 Overview Context of the project Architecture Radiation and low frequency noise Preliminary results Conclusion Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 2/28 Context of the project The 24-bit Digital-to-Analog data converter is intended to be suitable for space and is designed using the 0.13um CMOS technology of STM. The converter will be used by ESA in the Laser Interferometer Space Antenna (LISA) experiment for detecting and observing gravitational waves in the frequency range 10-4 to 10-1 Hz from massive black holes and galactic binaries. This work is supported by an ESA contract. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 3/28 Key Features The core of the converter is a 3rd order ΣΔ modulator with an internal multibit quantizer for achieving excellent dynamic performance and monotonic behavior in the range of 0.1 mHz up to 1 kHz. It supports both serial and 24-bit parallel input format. Target SNR performance ~120 dB at full bandwidth. Programmable Oversampling Ratio for sampling rates of 6 or 12 kHz. Slave I2C for register configuration. Differential current output (0 to 5.84mA). Reference current of internal DAC may be fixed through an external resistor. 1.2V/3.3V for the digital and analog part respectively. Separate Digital and Analog power down features. Power consumption <70 mW. Cascade of multiple DAC devices by using common biasing signals. This converter can be used as a stand alone device or embedded as an IP core. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 4/28 Specifications for radiation tolerance LET for SEL immunity: ≥ 70 MeV/mg.cm-2 TID tolerance: ≥100 krad Temperature range (functional) : Temperature range (full performance) : Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. -55 °C < T < 125 °C 0 °C < T < 50 °C 5/28 Architecture 24-bit digital input Input interface I2C slave IRP1 x2 IRP2 x2 Dynamic Element Matching Algorithm (DWA) 32 Generation of reference current IRP3 x2 3rd order ΣΔ modulator Thermometer encoded data Matrix Array of 32 current sources Biasing scheme Second International Workshop on AMICSA SINC x32/x16 Differential current output 24-bit D/A IIIntegrated SD Systems Development S.A. 6/28 Architecture – Digital Part (1/4) Efficient implementation of the digital interpolation implies using a multi-stage structure (reduced computational complexity) for the filtering, which is inherent in the interpolation procedure. FIR filters have linear phase and symmetric coefficients (symmetric direct-form topology). Interpolation filters are designed using a a MAC architecture based on a polyphase implementation, which is optimal for x2 upsampling. Linear interpolation is achieved by a SINC Filter (x16/x32): Fs Simple HW implementation. Medium attenuation of image replicas. FIR Equiripple Linear Phase (IRP1) x2 Second International Workshop on AMICSA Half Band (IRP2) x2 Half Band (IRP3) x2 IIIntegrated SD Systems Development S.A. SINC x32 or x16 OSR·Fs 7/28 Architecture – Digital Part (2/4) 3rd order ΣΔ architecture employing oversampling and quantization noise shaping. Multi-bit quantization for stability and relaxation of the requirements of the analog post filter. 2 3 2L 1 N DR 10 log10 2 L 2 1 OSR 2 L 1 2 L: Order of the ΣΔ modulator N: Number of quantization bits OSR: Oversampling Ratio Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 8/28 Architecture – Digital Part (3/4) The modulator under DC excitation or with very low frequency signals may produce periodic patterns, which give rise to idle tones. The in-band tones will not be suppressed by the postreconstruction filter. • A 19-bit pseudo-random signal generated by a 35-bit Linear Feedback Shift Register (LFSR) is used to break the periodicity of the tones. • This additional random noise will be shaped to higher frequencies by the ΣΔ modulator with negligible SNR degradation. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 9/28 Architecture – Digital Part (4/4) The inferior linearity of the internal DAC in multibit architectures degrades the overall performance. The selection of elements is based on the DWA algorithm, which is used so as to suppress in-band harmonic distortion that stems from element mismatch. The DWA circuitry selects the DAC elements in a rotational way, resulting in a firstorder shaping of the error due to element mismatch. The algorithm gives good results for σE ≤ 0.1%. 2 N OSR3 ENOB log 2 1- 1 E N 2 Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 10/28 Architecture - Analog Part (1/6) Matrix of 32 PMOS differential current sources (correspond to 5-bit DAC). Level shifter for adjustment of digital signals from 1.2V to 3.3V. Reference current is generated internally and can be tuned by an external resistor. Appropriate biasing scheme. Low frequency design (because of flicker noise) is a challenge. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 11/28 Architecture - Analog Part (2/6) 10uA Current Bias Bandgap 1.2V + LPF LOW NOISE OPAMP - Array of current sources IRef M1 Iout+ IoutRRef Rext The Bandgap block is used for generating a stable voltage tolerant to temperature variations. The Low Pass Filter before the amplifier is used to decrease the noise bandwidth of the Bandgap reference block. The Operational amplifier is biased by a 10uA current in order to generate a fixed reference current IRef through transistor M1. The reference current can be fixed inside or outside by using an external resistor. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 12/28 Architecture - Analog Part (3/6) 1:32 M2 M3 Current Bias 1.2V Bandgap LPF IRef I2n,in + LOW NOISE OPAMP - M1 Iout R2 I2n,out I/V converter Vout RRef The Bandgap and the operational amplifier are low noise designs. The noise from the various blocks is additive and its total amount at the output of the converter is related to the number of current sources that steer current at a given time. An I/V converter which converts the current (and each noisy component) to voltage before the later is fed to the reconstruction filter is used in the noise calculations. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 13/28 Architecture - Analog Part (4/6) The Bandgap reference block provides 1.2V at low temperature coefficient. Resistors with different temperature coefficient are used for generating the reference voltage. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 14/28 Architecture - Analog Part (5/6) Low noise and distortion implementation based on a two stage implementation: a differential first stage followed by a push-pull output gain stage. Large devices are used in the input stage to achieve low noise levels. The amplifier senses the voltage drop across RRef and fixes the current IRef by biasing appropriately transistor M1. Second International Workshop on AMICSA 1.2V IIIntegrated SD Systems Development S.A. 10 uA Bias current + LOW NOISE OPAMP - M1 IRef RRef 15/28 Architecture - Analog Part (6/6) Differential folded cascode PMOS current sources for increased output M4 impedance controlled by a complementary 32-bit signal. In this Regulated Cascode topology, the drain source voltage of M2 is kept stable for obtaining high overall output Amplifier impedance against channel length modulation. This is accomplished by a feedback loop consisting of an amplifier (M4 and M3) and M1 acting as a follower, Increased transistor size for high linearity and decrease of flicker noise. The layout follows the commoncentroid technique to avoid systematic errors and achieving better matching. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. M2 Follower M1 M3 16/28 For addressing the radiation (1/3) The design of a radiation-hardened chip follows the general design flow with some manufacturing and design variations that reduce the susceptibility to high-energy subatomic particles and electromagnetic radiation, such as would be encountered in outer space, high-altitude flights or nuclear reactors. The 0.13 um CMOS technology of STM is qualified for space applications, disposes a Radiation Hardened digital library, whereas it assures small threshold voltage drifts. Measurements with heavy ions and protons no latchup nor hard fail occurred up to 120 MeV/mg.cm-2 High intrinsic radiation hardness measured with gamma rays. The irradiated chip functionality was 100% at 100 krad (Si) with no over-consumption. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 17/28 For addressing the radiation (2/3) fsm_state For the digital part the robust cells from the library are used during synthesis. Moreover: Fault masking by TMR at FSM level. Synchronous reset. fsm_state_next_1 FSM1 FSM2 fsm_state_next_2 FSM3 FSM1 control_signal control_signal_1 VOTING SCHEME fsm_state_next_3 D-flip flop control_signal_3 VOTING SCHEME control_signal Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 18/28 For addressing the radiation (3/3) For the analog part: Surrounding each n-channel device with a p+ guard ring, which cuts any possible radiation induced parasitic path. Increase the W/L ratio of the transistors, which increases the capacitance and the driving power. Adding additional capacitances to the most sensitive nodes. Increase the distance between the p+ diffusion in the well and the n+ in the substrate. Increase the number of the substrate and well contacts. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 19/28 For reducing the flicker noise (1/2) Flicker noise is the main limiting factor and affects the low frequency performance of the device. The flicker noise is mainly generated by the trapping and releasing of the charge carriers whose time constant is finite and the phenomenon is maybe not accurately modeled by the circuit simulator during current source switching. For an acceptor like trap: τe=emission time τc =capture time Electrical noise and RTS fluctuations in advanced CMOS devices G. Ghibaudo, T. Boutchacha, Microelectronics Reliability 42 (2002) 573–582 Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 20/28 For reducing the flicker noise (2/2) Our strategy is based on: Increasing the device size. Using very low noise biasing schemes. Reducing the time slot for which the current sources drive current in order to avoid quasi-static phenomena. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 21/28 Preliminary results(1/4) Flicker noise is dominant in low frequencies. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 22/28 Preliminary results(2/4) SNR improvement when large devices are used (flicker noise reduces by increasing the WL product). Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 23/28 Preliminary results(3/4) By further improving the bandgap. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 24/28 Preliminary results(4/4) SNR results vs temperature at 10-4 Hz. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 25/28 Output current variation vs temperature The output current variations are in the order of uA. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 26/28 Conclusion A high resolution Digital to Analog Converter for space application has been presented. The DAC exhibits more than 120 dB SNR above 0.1 Hz and 80 dB in the 0.1 mHz range. The DAC exhibits low power characteristics and has a very small footprint about 1 mm2 with pads. Suitable for stand-alone and embedded applications. Multiples instances of the same DAC. Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 27/28 Thank you for your attention ! Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 28/28 External filtering considerations OUTP Differential current output Analog Part VOUTP Low Pass Differential Differential I/V converter voltage Reconstruction voltage Filter output output OUTM VOUTM DAC VOUTP VOUTM The reconstruction filtering (stop-band attenuation, ripple) is related to the content of the application. An I/V converter should be placed before the continuous time reconstruction filter. It is desirable for the driven load to exhibit a low pass characteristic. Passband (kHz) Stopband (kHz) Stopband Attenuation Passband Ripple Filter type Order 1.01 45 100 dB 0.001 dB Chebyshev-II 4 1.01 45 80 dB 0.01 dB Chebyshev-II 3 1.01 45 70 dB 0.01 dB Butterworth 3 Second International Workshop on AMICSA IIIntegrated SD Systems Development S.A. 29/28