* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

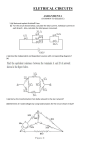

Download Review for Exam #1

Integrating ADC wikipedia , lookup

Topology (electrical circuits) wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Josephson voltage standard wikipedia , lookup

RLC circuit wikipedia , lookup

Two-port network wikipedia , lookup

Electrical ballast wikipedia , lookup

Schmitt trigger wikipedia , lookup

Wilson current mirror wikipedia , lookup

Operational amplifier wikipedia , lookup

Voltage regulator wikipedia , lookup

Power electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power MOSFET wikipedia , lookup

Surge protector wikipedia , lookup

Current source wikipedia , lookup

Rectiverter wikipedia , lookup

Opto-isolator wikipedia , lookup

Exam #1 Review Dr. Holbert February 18, 2008 LectR1 EEE 202 1 Basic Circuit Analysis Methods • • • • While Obeying Passive Sign Convention Ohm’s Law; KCL; KVL Voltage and Current Division Series/Parallel Resistance combinations Rseries R1 R2 RN R j 1 1 1 1 1 Rpar R1 R2 RM Ri LectR1 EEE 202 2 Default Sign Convention • Passive sign convention : current should enter the positive voltage terminal I + Circuit Element – • Consequence for P = I V – Positive (+) Power: element absorbs power – Negative (-) Power: element supplies power LectR1 EEE 202 3 Ohm’s Law V=IR I + The Rest of the Circuit LectR1 R V – EEE 202 4 KCL (Kirchhoff’s Current Law) i1(t) i5(t) i2(t) i4(t) i3(t) The sum of currents entering the node is zero: n i (t ) 0 j 1 j Analogy: mass flow at pipe junction LectR1 EEE 202 5 KVL (Kirchhoff’s Voltage Law) + v1(t) + – v2(t) – + v3(t) – The sum of voltages around a loop is zero: n v j 1 j (t ) 0 Analogy: pressure drop through pipe loop LectR1 EEE 202 6 KVL Polarity • A loop is any closed path through a circuit in which no node is encountered more than once • Voltage Polarity Convention – A voltage encountered + to – is positive – A voltage encountered – to + is negative LectR1 EEE 202 7 In General: Voltage Division • Consider N resistors in series: Ri VRi (t ) VSk (t ) Rj • Source voltage(s) are divided between the resistors in direct proportion to their resistances LectR1 EEE 202 8 In General: Current Division • Consider N resistors in parallel: iR j (t ) iS k (t ) R par Rj 1 1 1 1 1 R par R1 R2 RN Ri • Special Case (2 resistors in parallel) R2 iR1 (t ) iS (t ) R1 R2 LectR1 EEE 202 9 Equivalent Impedance • If we wish to replace two parallel resistances with a single resistor whose voltage-current relationship is the same, the equivalent resistance has a value of: R1 R2 Req R1 R2 • Parallel elements share the same two (distinct) end nodes LectR1 EEE 202 10 Steps of Nodal Analysis 1. Choose a reference (ground) node, V=0. 2. Assign node voltages to the other nodes. 3. Apply KCL to each node but the reference node; V1 V2 express currents in terms R of node voltages. 4. Solve the resulting system V1 V2 of linear equations for the I R nodal voltages. LectR1 EEE 202 11 Steps of Mesh/Loop Analysis 1. Identify mesh (loops). 2. Assign a current to each mesh. 3. Apply KVL around each I2 loop to get an equation in V R + – R terms of the loop currents. I1 4. Solve the resulting system of linear equations for the V = (I – I ) R R 1 2 mesh/loop currents. LectR1 EEE 202 12 Nodal and Loop Analyses Nodal Analysis Recipe 1&2) Identify and label N nodal voltages plus the ground node (V=0) 3) Apply KCL at N nodes (supernode makes constraint eq.) 4) Solve for the nodal voltages LectR1 Loop Analysis Recipe 1&2) Identify and label M mesh currents 3) Apply KVL at the M meshes (a current source makes a constraint equation) 4) Solve for the mesh currents EEE 202 13 Superposition Procedure 1. For each independent voltage and current source (repeat the following): a) Replace the other independent voltage sources with a short circuit (i.e., V = 0). b) Replace the other independent current sources with an open circuit (i.e., I = 0). Note: Dependent sources are not changed! c) Calculate the contribution of this particular voltage or current source to the desired output parameter. 2. Algebraically sum the individual contributions (current and/or voltage) from each independent source. LectR1 EEE 202 14 Source Transformation A voltage source in series with a resistor is transformed into a current source in parallel with that resistor; and vice versa. Vs + – Rs Is Rs Vs Rs I s LectR1 EEE 202 15 Basic Approach to Finding the Thevenin/Norton Equivalent • Circuits with independent sources: – Find Voc and/or Isc – Compute RTh (= Voc / Isc) • Circuits without independent sources: – Apply a test voltage (current) source – Find resulting current (voltage) – Compute RTh (= Vtest / Itest) LectR1 EEE 202 16 Thevenin/Norton Equivalent RTh Voc + – Isc Thevenin equivalent circuit LectR1 RTh Norton equivalent circuit EEE 202 17 Op Amps • Generally apply KCL or nodal analysis • Ideal Op-Amp Relations i– = 0 = i+ v– = v+ LectR1 + – EEE 202 18