* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download V t

Josephson voltage standard wikipedia , lookup

Regenerative circuit wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Electronic engineering wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Thermal runaway wikipedia , lookup

Broadcast television systems wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Schmitt trigger wikipedia , lookup

Power electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Telecommunication wikipedia , lookup

Integrated circuit wikipedia , lookup

Current source wikipedia , lookup

Surge protector wikipedia , lookup

Rectiverter wikipedia , lookup

Operational amplifier wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

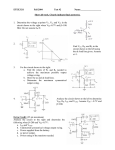

Lecture 20 Current Source Biasing and MOS Amplifier Design • Temperature and supply-independent biasing • OPAMP design • Summary Michael L. Bushnell CAIP Center and WINLAB ECE Dept.,Analog Rutgers U., Piscataway, NJ and Low-Power Design Lecture 20 (c) 2003 1 Temperature and SupplyIndependent Biasing • Biasing must also be independent of process variations – Critical for MOS circuits • Bias I fluctuations with T, VDD, and process cause wasted energy • Supply-independent biasing is important – Avoid injecting high-f noise on power lines into circuit signal path Analog and Low-Power Design Lecture 20 (c) 2003 2 Supply-Independent Biasing • Refer bias circuit to potential other than VDD: Vt – threshold voltage of MOSFET Vbg – band-gap voltage DVt of dissimilar devices VBE of parasitic bipolar transistor in CMOS VT – thermal voltage (k T / q) Zener diode breakdown V – too high breakdown V • Self-biasing requires a start-up circuit – Must force circuit into equilibrium in desired stable state Analog and Low-Power Design Lecture 20 (c) 2003 3 Vt Referenced Self-Biased Circuit • Fig 12.25a (old book) Analog and Low-Power Design Lecture 20 (c) 2003 4 Analysis • Feedback from M2, M3 & M4 forces same current I to flow in • • • • M1 and R Operating point must satisfy: I R = VGS1 = V t1 + 2I mn Cox (W / L)1 Neglect channel length modulation & body effect Make 2nd term small compared to Vt 1. Use low bias current 2. Use large W/L • I Vt / R Analog and Low-Power Design Lecture 20 (c) 2003 5 Analysis (continued) • If 2nd term included, O/P current is slightly reduced but T and • VDD dependence is the same Must ensure stability – need to verify that feedback loop gain is < 1 at operating point – Do by breaking the loop, injecting a signal, & checking the gain • Must determine degree of supply independence – Channel length modulation in M2 & M1 causes bias current variation • Reduce variation with cascode current source Analog and Low-Power Design Lecture 20 (c) 2003 6 Problem • In typical MOS process, Vt not well controlled 0.5 V Vt 0.8 V • Vtn has TC (temperature coefficient) of –2 mV / oC, but diffused R’s have a large positive TC • Results in O/P current with large negative TC Analog and Low-Power Design Lecture 20 (c) 2003 7 Delta Vt Temperature Independence • Use differences in Vt of two devices of same polarity but with different channel implants • Advantage: TC’s of two devices cancel to first order – Can get O/P Voltage TC as low as 20 ppm / oC Analog and Low-Power Design Lecture 20 (c) 2003 8 DVT Referenced Biasing • Fig 12.25b (old book) Analog and Low-Power Design Lecture 20 (c) 2003 9 Disadvantages • Large initial tolerance in O/P voltage value – Threshold voltages have large tolerance • Extensively used for precision voltage references in nMOS and CMOS – Need to trim a resistor to adjust absolute O/P voltage Analog and Low-Power Design Lecture 20 (c) 2003 10 VBE Referenced Biasing • Fig 12.26 (old book) Analog and Low-Power Design Lecture 20 (c) 2003 11 Analysis • pnp is a parasitic bipolar device in p-substrate CMOS • Can also use a parasitic npn transistor • Feedback involving M1, M2, M3, M4 forces emitter current in Q1 • • to match R current I R = VT ln I or I = VBE1 IS R Advantage: VBE is well-controlled, with 5% variation Disadvantage: VBE has a negative TC of –2 mV / oC – R has a strong positive TC – Leads to a strong negative TC in bias current – Can reduce reference current variation with a cascode or Wilson current source Analog and Low-Power Design Lecture 20 (c) 2003 12 VT-Referenced Biasing (Thermal Voltage) • Fig 12.27 (old book) Analog and Low-Power Design Lecture 20 (c) 2003 13 Analysis • Q1 & Q2 transistor areas differ by n factor • Feedback circuit makes them operate at same bias current Difference between two VBE’s appears across resistor R VBE = VT ln I VBE / VT IS I = IS e ( ) • Get: I R = VBE1 – VBE2 [ ] ( ) ( ) ( ) Or = VT ln I - VT ln I IS n IS = VT ln I n IS IS I I = VT ln (n) R Analog and Low-Power Design Lecture 20 (c) 2003 14 Discussion • Advantage: VT has positive temperature coefficient (VT = kT / q) • R has a positive TC, so current output is relatively T independent Analog and Low-Power Design Lecture 20 (c) 2003 15 VT Referenced Self-Biased Reference Circuit • With cascoded devices: – Improves power-supply rejection and initial accuracy • DV across R is ~ 100 mV • Small differences in VGS for M1 & M2 cause large O/P current (IOUT) changes – Result from device mismatches or from channel length modulation in M1 & M2 (with different drain voltages) Analog and Low-Power Design Lecture 20 (c) 2003 16 Self-Biased Reference Circuit • Fig 12.28 (old book) Analog and Low-Power Design Lecture 20 (c) 2003 17 Band-Gap Referenced Biasing • Fig 12.29 (old book) Analog and Low-Power Design Lecture 20 (c) 2003 18 Analysis • IM8 drain = VT ln (n) • • • R V0 = VBE + VT ln (n) x R R = VBE + x VT ln (n) OPAMP maintains V0 at both + and – terminals due to feedback IOUT = V0 / R2 Advantage: By weighting VBE and VT components, one gets a voltage of any desired TC ( ) – Can exactly cancel an R TC Analog and Low-Power Design Lecture 20 (c) 2003 19 Weighting • Parameter x determines weighting of VT-dependent portion: 1. Can use only common collector transistors 2. OPAMP has MOS transistors, so their input offset voltage and input offset voltage temperature drift influence O/P voltage of the reference • Must remove offset with analog storage and cancellation Analog and Low-Power Design Lecture 20 (c) 2003 20 Summary • Temperature and supply-independent biasing • OPAMP design Analog and Low-Power Design Lecture 20 (c) 2003 21